具有对计数器的改进的支持的FPGA逻辑单元

文献发布时间:2023-06-19 11:27:38

背景技术

本发明涉及用于用户可编程电路诸如现场可编程门阵列(FPGA)中的逻辑电路。更具体地,本发明涉及用于此类可编程集成电路的逻辑单元,所述逻辑单元具有对计数器应用的改进的支持。

如本领域中所公知的,FPGA由通过可编程路由网络连接的逻辑单元组成。连接至可编程路由网络的任何逻辑单元输出的值可通过网络传输到连接至网络的任何逻辑单元输入。常见类型的逻辑单元包括K-输入查找表(LUT)和附加的逻辑函数,诸如多路复用器和进位链。值K可在2至10或更大值的范围内;在实施过程中最常见的值为3、4和6。图1示出了现有逻辑单元10(如Microsemi

虚线30内示出的进位链实施方式包括附加的三个多路复用器。4-输入多路复用器32具有连接至3-输入LUT 14a和3-输入LUT 14b的相应输出以及连接至常数逻辑0和常数逻辑1的数据输入,并且产生输出G。由正方形34表示的配置位用于选择4-输入多路复用器32的输入中的哪一个输入将在G处传递至输出。

3-输入多路复用器36具有连接至多路复用器16的输出以及连接至常数逻辑0和常数逻辑1的数据输入,并且产生输出P。由正方形38表示的配置位用于选择第三多路复用器36的输入中的哪一个输入将在P处传递至输出。

进位输出多路复用器40具有连接至逻辑单元10的进位输入CI 42的数据输入和连接至4-输入多路复用器32的输出G的数据输入。进位输出多路复用器40的输出连接至逻辑单元10的进位输出CO 44。进位输出多路复用器40的选择输入连接至3-输入多路复用器36的输出P。

异或门46具有在多路复用器16的输出处连接至4-输入LUT 12的输出的第一输入,该第一输入还形成逻辑单元10的主要输出Y 48。异或门46的第二输入连接至逻辑单元10的进位输入CI 42。异或门46的输出是逻辑单元10的总和输出S 50。

In

现有的基于LUT的FPGA逻辑单元如图1的逻辑单元10可实施递增计数器或递减计数器的一位或累加器的一位。这在图2中示出,该图是使用被标识为逻辑单元10-0、10-1和10-(N-1)的N个逻辑单元以及D-触发器54-0、54-1和54(N-1)来实施的N-位计数器的框图。然而,因为在逻辑单元10-0、10-1和10-(N-1)中的每一个逻辑单元中需要第一多路复用器16来驱动3-输入多路复用器36和用于实施计数器函数的异或门46,因此逻辑单元10-0、10-1和10-(N-1)中没有一个逻辑单元可在实施计数器时将4-输入LUT 12用于其他目的,尽管它们并未用于实施计数器。

FPGA逻辑单元的一个重要特性是其输入和输出中有多少必须连接至可编程路由网络。例如,图3A所示的现有逻辑单元60在由加利福尼亚州圣何塞市的Xilinx,Inc.公司制造的

逻辑单元60包括具有分别在附图标号18、20、22和24处标识的输入In

逻辑单元60的进位链区段在虚线68内标识。进位链68包括6-输入多路复用器70。6-输入多路复用器70的第一输入由2-输入与门72驱动,该2-输入与门由至LUT 62的In

6-输入多路复用器70的输出耦合到2-输入进位输出多路复用器40的一个输入。进位输出多路复用器40的另一个输入由2-输入多路复用器78的输出驱动,其中一个输入耦合到线路80上的低阶逻辑单元的CO输出。至多路复用器78的另一个输入由虚线中示出的线路82上的X输入驱动,因为该连接仅在逻辑单元60的交替的(例如,奇数或偶数)实例中进行。

与LUT输入In

FPGA逻辑单元的另一个重要特性是至LUT的输入的数目K。一些现有FPGA使用4-输入LUT单元(K=4),如图1和图3A的逻辑单元10和逻辑单元60所示,这对于低成本、低功率FPGA而言总体上最好。其他现有FPGA使用可拆分的6-输入LUT(K=6)。这些FPGA可实施更多样的函数,但消耗更大的面积和更多的功率。对与LUT输入的数目相关的权衡的最新研究可见于2018年的ACM/SIGDA国际现场可编程门阵列研讨会论文集中的“Improving FPGAPerformance with a S44 LUT Structure”,2018年。

图3B中示出了6-输入LUT逻辑单元的一个现有示例。这是包括虚线92中示出的可拆分的6-输入LUT的逻辑单元90的框图。该逻辑单元等同于由加利福尼亚州圣何塞市的Xilinx,Inc.公司制造的系列7逻辑单元。

6-输入LUT 92由两个5-输入LUT 94a和5-输入LUT 94b形成。如在图1的逻辑单元10中,小正方形96和小正方形98分别表示用于定义LUT 94a和LUT 94b的函数的配置位。至LUT 94a和LUT 94b的五个函数输入以附图标号100(In

多路复用器110具有分别标记为F0和F1的LUT 94a和LUT 94b的相应输出作为其数据输入。在附图标号112处的多路复用器110的选择输入连接至逻辑单元90的In

逻辑单元90的进位逻辑在虚线114内示出,并且由两个多路复用器36和40以及异或门46形成。多路复用器36(G多路复用器)具有连接至LUT 94a的F0输出的第一数据输入、连接至LUT 94b的F1输出的第二数据输入,以及连接至恒定低逻辑电平的第三输入。小正方形38表示用于将多路复用器36的输入中的一个输入路由到其输出的配置位。

第二多路复用器40为进位输出多路复用器,其数据输入中的一个数据输入连接至多路复用器36的输出G,并且其数据输入中的另一个数据输入连接至在附图标号42处标识的逻辑单元的进位(CI)输入。其选择输入连接至多路复用器110的输出。进位输出多路复用器40的输出连接至逻辑单元90的CO输出,如附图标号44所示。

异或门46具有连接至逻辑单元90的进位输入42的第一输入和连接至多路复用器110的输出的第二输入。异或门46的输出连接至逻辑单元90的总和(S)输出,如附图标号50所示。

逻辑单元90具有在附图标号48处示出的表示六输入LUT 92的输出的第一输出Y,以及在附图标号116处示出的连接至5-输入LUT 94a的F0输出的第二输出Y1。图3B的逻辑单元90中的六输入LUT 92被称为“可拆分的”,原因在于5-输入LUT 94a和5-输入LUT 94b可独立使用,因为直接输出Y 48和Y1 116可得自两个5-输入LUT(通过多路复用器110,从5-输入LUT 94a获得输出Y1 116并且从5-输入LUT 94b获得输出Y 48)。

逻辑单元90在图3B中示出,该逻辑单元被配置为实施计数器的一位和4个输入的任何独立函数。In

编程到FPGA中的一些设计需要大量的递增计数器或递减计数器。特别是对于此类设计,如果图1的4-输入LUT单元可实施计数器,同时保留将LUT用于其他目的,则将是有益的。如果6-输入LUT单元可实施计数器,同时保留使用LUT的4个以上的输入,也是有益的。

此外,二元神经网络是越来越重要的应用。二元神经网络通常需要实施被称为“群体计数”或“pop计数”的函数。该函数将一组M个布尔输入中的一个布尔输入的数目表示为log2(M)-位二进制输出值。pop计数器通常使用压缩器和(允许在多个时钟周期内计算值的)累加器来实施。

压缩器是采用多个二进制数值作为输入并且将它们的总和产生为单个二进制数值输出值的一系列逻辑电路。例如,熟知的全加法器也可以被称为3:2压缩器;它需要三个一位输入并且产生单个两位输出。在一些情况下,压缩器可被组织在类似于进位链的链中,其中每个压缩器接收来自链中的先前的压缩器的一个或多个附加输入,并且生成到链中的下一个压缩器的相同数目的附加输出。关于压缩器的更多细节,参见1980年5月的Gajski的“Parallel Compressors”,《IEEE计算机汇刊》,第c-29卷,第5期。利用先前的逻辑单元诸如图1的(使用高功效的4-输入LUT和至可编程路由网络的有限连接的)逻辑单元,需要两个逻辑单元来实施每个3:2压缩器:其中一个逻辑单元用于产生两个输出中的每一个输出。可在图3A和图3B的逻辑单元中的单个逻辑单元中实施3:2压缩器,但图3A的逻辑单元60需要与可编程路由网络52的更多连接,并且图3B的逻辑单元90既消耗更多的面积又消耗更多功率,还具有与可编程路由网络的用于CO输出的附加连接。

在不增加连接至可编程路由网络的输入和输出的数目(使可编程路由网络更复杂且成本更高)或不增加LUT输入的数目K(这将显著增加逻辑单元的面积和功率消耗)的情况下,提高在4-输入LUT逻辑单元诸如图1的4-输入LUT逻辑单元中实施计数器和压缩器的效率将是有利的。这种效率提高将使得用户能够将更多逻辑封装在具有相同数目的单元的FPGA芯片中,并且可能使其计时更快。

发明内容

根据本发明的一个方面,呈现了一种用于可编程逻辑集成电路的逻辑单元,其中K为使得逻辑单元可计算K个输入的任何函数的最大数目,并且逻辑单元可被配置为与K-1个输入的任何独立函数并行地实施计数器的一位。

根据本发明的一个方面,计数器可以是递增计数器或递减计数器。

根据本发明的一个方面,逻辑单元可进一步被配置为与K个输入的任何独立函数并行地实施计数器的一位。

根据本发明的一个方面,逻辑单元可进一步被配置为实施双输入加法器的一位。

根据本发明的一个方面,逻辑单元可进一步被配置为实施双输入加法器的一位,并且逻辑单元具有将用来计算函数的K个函数输入;接收计数器位的当前状态的计数器输入;进位输入;进位输出;初级输出,K-输入函数的输出在初级输出处可用;总和输出,计数器的一位和一位加法器的输出中的一者的输出在总和输出处可用;K-输入LUT,该K-输入LUT的输入由K个函数输入驱动并且其输出驱动初级输出;以及进位电路,该进位电路耦合到进位输入和计数器输入并且驱动进位输出和总和输出。该进位电路可反转或不反转计数输入。

根据本发明的两个特定方面,K=4并且K=6。

根据本发明的一个方面,用于可编程逻辑集成电路的逻辑单元具有连接至可编程路由网络的仅4个输入,逻辑单元具有连接至可编程路由网络的仅两个输出,逻辑单元具有进位输入,逻辑单元可以第一方式被配置为使得进位输入的值出现在输出中的一个输出处,并且并行地,4个输入的任何函数出现在另一个输出处,并且逻辑单元可以第二方式被配置为实施双输入加法器的一位,其中总和位出现在两个输出中的一个输出处。

根据本发明的一个方面,逻辑单元可用于实施4:2压缩器的链,其中4:2压缩器的链中的每一个4:2压缩器可在逻辑单元的2个实例中实施。

根据本发明的一个方面,用于可编程逻辑集成电路的逻辑单元包括进位输入;产生进位输出信号的2-输入进位输出多路复用器;2-输入异或门,该2-输入异或门具有第一输入和第二输入,第一输入由不驱动可编程路由网络的进位输入驱动,第二输入由也不驱动可编程路由网络的信号驱动;多路复用器,该多路复用器产生驱动进位输出多路复用器的选择输入和异或门的一个输入的信号P。

根据本发明的一个方面,用于可编程逻辑集成电路的逻辑单元包括K个数据输入;初级输出;进位输入;进位输出;计数器输入;总和输出;K-输入查找表(LUT),该K-输入LUT具有各自连接至K个数据输入中的不同数据输入的K个LUT输入,以及直接连接至初级输出的LUT输出,该K-输入LUT包括第一(K-1)-输入查找表LUT和第二(K-1)-输入LUT,这两者共同共享至K-输入LUT的第二至第K输入,第一(K-1)-输入LUT和第二(K-1)-输入LUT中的每一者具有输出;第一多路复用器,该第一多路复用器具有耦合到第一(K-1)-输入LUT的输出的第一输入、耦合到第二(K-1)-输入LUT的输出的第二数据输入,以及耦合到K-输入LUT的第一输入的选择输入,该第一多路复用器具有形成直接连接至初级输出的LUT输出的输出。

根据本发明的一个方面,逻辑单元具有进位电路,该进位电路包括:第二多路复用器,该第二多路复用器具有耦合到第一(K-1)-输入LUT和第二(K-1)-输入LUT中的一者的输出的第一数据输入、耦合到逻辑低恒定电压的第二数据输入、耦合到逻辑单元的配置电路的选择输入,以及数据输出;第三多路复用器,该第三多路复用器具有耦合到逻辑单元的计数器输入的第一数据输入、耦合到LUT输出的第二数据输入、耦合到逻辑低恒定电压的第三数据输入、耦合到逻辑单元的配置电路的选择输入,以及数据输出;进位输出多路复用器,该进位输出多路复用器具有耦合到第二多路复用器的数据输出的第一数据输入、耦合到逻辑单元的进位输入的第二数据输入、耦合到第三多路复用器的数据输出的选择输入,以及耦合到逻辑单元的进位输出的数据输出;以及异或门,该异或门具有耦合到逻辑单元的进位输入的第一输入、耦合到第三多路复用器的数据输出的第二输入,以及耦合到逻辑单元的总和输出的输出。进位电路还可包括耦合在逻辑单元的计数器输入和第三多路复用器的第一数据输入之间的第四多路复用器,该第四多路复用器具有第一数据输入和第二数据输入,该第二数据输入为反相数据输入,第一数据输入和第二数据输入一起耦合到逻辑单元的计数器输入,该第四多路复用器具有耦合到逻辑单元的配置电路的选择输入,以及耦合到第三多路复用器的第一数据输入的输出。

根据本发明的一个方面,第二多路复用器和第三多路复用器中的至少一者具有耦合到逻辑高恒定电压的数据输入。

根据本发明的一个方面,第二多路复用器具有耦合到第一(K-1)-输入LUT的输出的数据输入,以及耦合到第二(K-1)-输入LUT的输出的数据输入。

附图说明

下面将参考各个方面和附图更详细地解释本发明,附图中示出:

图1是现有逻辑单元的框图;

图2是每一位使用一个图1的现有逻辑单元的递增计数器的框图;

图3A是现有逻辑单元的图,该逻辑单元包括4-输入LUT和用于进位输入和进位输出的与可编程路由网络的附加连接;

图3B是包括可拆分的K-输入LUT并且能够同时实施递增计数器和任何(K-2)-输入函数(其中K=6)的现有逻辑单元的框图;

图4是根据本发明的一个方面的逻辑单元的框图;

图5是根据本发明的一个方面的每一位使用图4的一个逻辑单元的递增计数器的框图;

图6是根据本发明的一个方面的支持递增计数器函数和递减计数器函数两者的逻辑单元的框图;

图7是根据本发明的一个方面的每一位使用图6的一个逻辑单元的递减计数器的框图;

图8是根据本发明的一个方面的每个输出位使用图4的一个逻辑单元的具有L-位输入和N-位输出的累加器的框图;

图9A是根据本发明的一个方面使用图4的逻辑单元实施的3:2压缩器的框图;

图9B是根据本发明的一个方面使用图4的逻辑单元实施的3:2压缩器的详细视图;

图10A是4:2压缩器的功能框图;

图10B是根据本发明的一个方面使用类似于图4的逻辑单元的逻辑单元实施的4:2压缩器的框图;并且

图11是根据本发明的一个方面使用类似于图4的逻辑单元的逻辑单元实施的2-输入加法器的框图。

具体实施方式

本领域普通技术人员将认识到,以下描述仅是例示性的而非以任何方式进行限制。本领域的技术人员将易于想到其他方面。

本发明提高了现有的基于LUT的FPGA逻辑单元在实施递增计数器、递减计数器和pop计数器方面的效率。当实施这些函数中的每一个函数时,逻辑单元中的一些逻辑单元中的K-输入LUT中的一些仍然可用于生成至那些LUT的K个输入的任何函数。

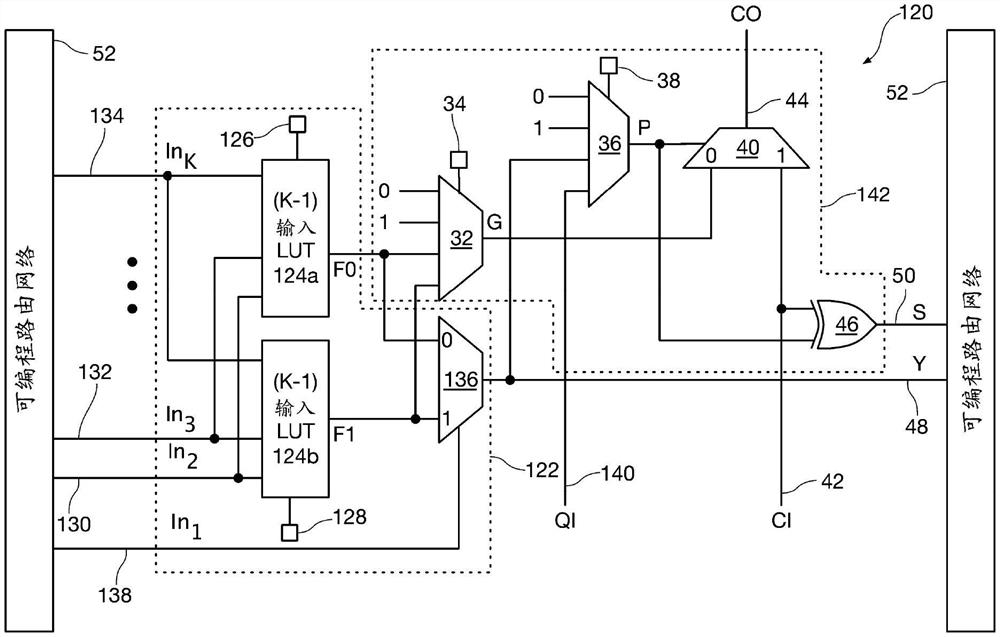

根据本发明的一个方面,图4中示出了允许提高递增计数器和pop计数器的效率的例示性的基于LUT的逻辑单元120,现在将注意力集中到该逻辑单元。图4的逻辑单元120的一些元件是与先前附图中所示的逻辑单元所共有的,并且将在图4中使用用于指定先前附图中的那些相同元件的相同的附图标号来指代。

图4的逻辑单元120包括在虚线122内示出的由第一(K-1)-输入LUT 124a和第二(K-1)-输入LUT 124b形成的K-输入LUT。小正方形126和小正方形128分别表示用于定义LUT124a和LUT 124b的函数的配置输入。LUT 124a和LUT 124b共同共享K-1函数输入(分别在附图标号130、132和134处示出的In

图4的逻辑单元120还包括进位输入CI 42、计数器输入QI 140、进位输出CO 44,以及总和输出S 50。图4的逻辑单元中的进位电路142包括在图4中示出为4-输入多路复用器32的第二多路复用器,其具有耦合到第一3-输入LUT 124a的F0输出的第一数据输入;耦合到第二3-输入LUT 124b的F1输出的第二数据输入;耦合到逻辑高恒定电压的第三数据输入;耦合到逻辑低恒定电压的第四数据输入;显示为小正方形34的选择输入,该选择输入耦合到用于多路复用器32的配置电路,用于选择第二进位多路复用器32的输入中的哪一个输入将被传递到其数据输出;以及表示为G的数据输出。第三多路复用器在图4中被示出为图4的逻辑单元的进位电路142中的4-输入多路复用器36,具有耦合到逻辑单元120的计数器输入QI 140的第一数据输入;在第一多路复用器136处耦合到K-输入LUT 122的输出的第二数据输入;耦合到逻辑高恒定电压的第三数据输入;耦合到逻辑低恒定电压的第四数据输入;显示为小正方形38的选择输入,该选择输入耦合到用于第三多路复用器36的配置电路,用于选择第三多路复用器36的输入中的哪一个输入将传递到其数据输出;以及表示为P的数据输出。在图4中示出为图4的逻辑单元110的进位电路142中的2-输入多路复用器40的进位输出多路复用器具有耦合到第二多路复用器32的数据输出G的第一数据输入;耦合到逻辑单元120的进位输入CI 42的第二数据输入;耦合到第三多路复用器36的P数据输出的选择输入;以及耦合到逻辑单元120的进位输出CO 44的数据输出。图4的逻辑单元120的进位电路142中的异或门46具有耦合到逻辑单元120的进位输入CI 42的第一输入、耦合到第三多路复用器36的数据输出P的第二输入,以及耦合到逻辑单元120的总和输出S 50的输出。

在本发明的一些具体实施中,来自LUT 124a和LUT 124b的F0或F1输入或者逻辑高恒定电压输入中的任一者可从第二多路复用器32省略,并且/或者逻辑高恒定电压输入可从第三多路复用器36省略。

图4所示的根据本发明的方面的逻辑单元120与图1中的现有逻辑单元之间的结构差异在于使用第二4-输入多路复用器36来驱动生成总和输出S 50的异或门46,以及向逻辑单元120添加QI计数器输入140,如图4所示。

广义地讲,图4的逻辑单元120具有K个函数输入、一个QI输入和一个进位输入。图4所示的特定示例包括K个函数输入,In

图5是示出可如何使用图4的逻辑单元120来实施递增计数器的框图。图5示出了由(N-1)个逻辑单元120-0、120-1和120-(N-1)形成的N-位递增计数器160。如图5所示,图4中的第二多路复用器32被设定为使得其输出G为值逻辑0,并且多路复用器36被设定为使得其输出P为图4的逻辑单元120的输入QI 140处的值。将表示最低有效位的逻辑单元120的进位CI输入42设定为逻辑1,并且将连续较高有效位中的每一者的进位CI输入42连接至相邻较低有效位逻辑单元120的进位输出CO 44。数据触发器162-0至162-(N-1)各自使其数据输入连接至包括在其相应计数器级中的逻辑单元110的S输出(图4中的138)。触发器162-0至162-(N-1)的Q输出各自连接至包括在其相应计数器级中的逻辑单元的QI输入(图4中的140)。

如图5所示,所有逻辑单元(120-0、120-1和120-(N-1)的LUT输入(为方便起见,在本发明的采用K-输入LUT 122的实例中示出为In

现在参见图6,框图示出了图4的逻辑单元的变型。图6的逻辑单元170包括存在于图4的逻辑单元120中的许多相同的元件。这两个附图中共有的这些元件将使用图4中采用的相同附图标号来表示。逻辑单元170中与逻辑单元120共有的元件如参考图4所述那样连接。

图6的逻辑单元170和图4的逻辑单元120之间的差异在于,图6的逻辑单元170还包括具有第一数据输入和第二数据输入的第四多路复用器172。第二数据输入为反相数据输入。第一数据输入和第二数据输入一起耦合到逻辑单元170的计数器输入QI 140,并且选择输入耦合到由小正方形174表示的逻辑单元的配置电路。第四多路复用器172的输出耦合到第三多路复用器36的第一数据输入。

第四多路复用器172选择性地反转QI输入134处存在的由配置位174配置的值。因此,图6的逻辑单元170采用第四多路复用器172作为可编程反相器,以通过将参考标号174处的配置位设定为传递参考标号140处的非反相或反相QI输入来支持递增计数器函数和递减计数器函数两者。与图4的逻辑单元的情况一样,在本发明的一些具体实施中,可从第二多路复用器32省略来自LUT 124a和LUT 124b的F0或F1输入或逻辑高恒定电压输入,并且/或者可从第三多路复用器36省略逻辑高恒定电压输入。

图7是示出用于实施递减计数器的图6的逻辑单元的框图。图7示出了使用(N-1)逻辑单元的N-位计数器180。具有最低有效位的进位CI输入被设定为逻辑0(而不是设定为图5所示的计数器中的逻辑1)。如图7所示,图6中的第二多路复用器32的输出被设定为传递值逻辑1,并且第三多路复用器36的输出P被设定为传递由第四多路复用器172反转的图6的逻辑单元170的输入QI 140处的值。同样如图7所示,所有逻辑单元(0、1和N-1)的所有LUT输入可用于与递增或递减计数器函数的运算同时生成K个输入的任何函数。

本发明的吸引人的特征之一在于,当实施递增计数器和递减计数器两者时,如图5和图7分别所示,每个逻辑单元120和170的所使用的整个K-输入LUT部分112保持可用于生成所有LUT输入的任何函数。使用现有逻辑单元不可能实现该特征,这是本发明的逻辑单元的显著优点,因为相比于现有技术可使用更少的逻辑单元来实施用户设计。

图8示出了图4和图6的逻辑单元120和逻辑单元170的灵活性的进一步说明,框图示出了可如何使用如图4的那些逻辑单元的逻辑单元来实施累加器。图8示出了具有L-位输入和N-位输出的累加器。N-位累加器190采用如图所示连接的示出为120-0至120-N的N个逻辑单元。逻辑单元120-0的CI输入连接至恒定的逻辑低“0”电平。每个逻辑单元的CO输出连接至累加器中的下一个逻辑单元的CI输入。

每个逻辑单元120-0至120-(N-1)分别与数据触发器192-0至192-(N-1)相关联。每个逻辑单元的S输出耦合到其相关联的数据触发器的D输入。每个数据触发器192-L至192-(N-1)的Q输出耦合到其相关联的逻辑单元的QI输入。

逻辑单元120-0至120-(L-1)的In

当实施累加器时,实施累加器190的较高有效位中的一者的逻辑单元的整个LUT部分保持完全可用于其他目的,如图8所示。从图8的检查可以看出,逻辑单元120-L至120-(N-1)的LUT函数保持可用于与累加器190的运算同时使用。虽然上文已经关于逻辑单元120进行了描述,但本领域的技术人员将认识到,这同样适用于逻辑单元170。

图4或图6的逻辑单元120和逻辑单元170的灵活性的另一个示例在图9A中示出。本发明的逻辑单元具有通过设定P=0将CI输入的值传输到S输出并且传输到可编程路由网络,同时使LUT可用于并行地实施K个输入的任何独立函数的能力。与图3A的现有单元相比,CI或CO与可编程路由网络之间不需要附加的价格高昂的连接。这种能力可例如允许更有效地实施压缩器。实施具有图1的现有逻辑单元的3:2压缩器将完全消耗两个单元。图9A示出了逻辑单元120或逻辑单元170可仅使用两个逻辑单元的部分来实施3:2压缩器的方式。本领域的普通技术人员将会知道,图9A的逻辑单元120-1仍然具有其可用的In1、In

图10A和图10B示出了图4或图6的逻辑单元120和逻辑单元170的灵活性的又一个示例。图10A是如图所示由两个全加法器212形成的4:2压缩器210的框图。图10A根据熟知的全加法器单元212来定义4:2压缩器的函数。压缩器210从任意指定为输入T、U、V、W和X的输入馈送。输入T将由链中的先前的压缩器的输出N驱动。图10B是示出如何仅需要两个逻辑单元120-0和120-1来实施图10A的4:2压缩器210的框图,并且包括示出实施该函数的逻辑单元120-0和120-1的配置的表。图10A的顶部全加法器212在图10B的逻辑单元1中实施。较低的全加法器212在逻辑单元0中实施,包括生成信号M,该信号然后从CI输入穿过逻辑单元1到达S输出。如图10B所示,可使用本发明的逻辑单元120中的两个逻辑单元来实施4:2压缩器,同时将需要图1所示的现有逻辑单元中的至少三个逻辑单元来实施该函数。虽然上文已经关于逻辑单元120进行了描述,但本领域的技术人员将认识到,这同样适用于逻辑单元170。

现在参见图11,框图示出了使用图4的逻辑单元120根据本发明的一个方面实施的双输入N-位加法器220。N-位加法器220采用如图所示连接的120-0至110-N所示的N+1逻辑单元。逻辑单元120-0的CI输入连接至恒定的逻辑低“0”电平。每个逻辑单元120的CO输出连接至加法器220中下一个逻辑单元120的CI输入。

逻辑单元120-0至120-(N-1)的In

虽然已经示出和描述了本发明的方面和应用,但是对于本领域的技术人员来说显而易见的是,在不脱离本文的发明构思的情况下,可能进行比上述更多的修改。例如,图9A、图9B和图10B所示的能力仅取决于本发明的方面,即,使用P而不是Y来驱动异或门,因此可在不包括添加图4所示的QI输入的另选实施方案中实现。因此,除了所附权利要求的实质之外,本发明不受限制。

- 具有对计数器的改进的支持的FPGA逻辑单元

- 一种具有改进的逻辑单元的集成电路