一种高压静电防护器件和电路

文献发布时间:2023-06-19 11:27:38

技术领域

本发明涉及半导体静电防护领域,尤其涉及一种高压静电防护器件和电路。

背景技术

静电防护(Electrostatic Discharge,ESD)是集成电路版图设计中的主要问题之一。现在集成电路发展迅速,工艺种类和芯片类型繁多,如何设计出一种通用的,简单的,有效的,小面积的高压ESD保护器件成为所有人关注的问题。

通常情况下,大家选择高压N金属氧化半导体(HVNMOS)晶体管或高压可控硅整流器(HVSCR)结构作为ESD保护器件,如图1和2所示。但是存在有如下问题:

1.如图1所示,HVNMOS作为ESD保护器件不能保护负电位(<0V)的PAD,且面积较大;隔离HVNMOS虽然可以用在负电位的PAD上,但大多数情况下需要添加层次,且版图所需面积更大。

2.HVSCR结构作为ESD保护器件虽然有较小的面积和较高的ESD能力,但结构复杂且对工艺的兼容性不高。

发明内容

为此,需要提供一种高压静电防护器件和电路,解决现有ESD保护器件结构复杂问题。

为实现上述目的,发明人提供了一种高压静电防护器件,包括P型衬底,所述P型衬底上设置有N型隔离层,所述N型隔离层上设置有N阱注入区和P阱注入区,所述N阱注入区和P阱注入区并排设置,所述N阱注入区顶部中间设置有N+注入区,所述P阱注入区顶部中间设置有P+注入区,N+注入区用于作为器件的阴极,P+注入区用于作为器件的阳极。

进一步地,所述N+注入区与P+注入区之间的所述N阱注入区和P阱注入区的尺寸与器件耐压值相关。

进一步地,所述N型隔离层被省去。

进一步地,所述N阱注入区和P阱注入区的数量为多个,所述N阱注入区和P阱注入区依次循环排列,相邻的所述N阱注入区之间设置有P阱注入区,相邻的所述P阱注入区之间设置有N阱注入区。

进一步地,所述器件表面覆盖有场氧化层,所述场氧化层上设置导电层,所述导电层分别与N+注入区、P+注入区连接。

进一步地,所述导电层为金属层。

本发明提供一种高压静电防护电路,所述电路包含有高压静电防护器件,所述高压静电防护器件为本发明任意一项实施例所述的高压静电防护器件,所述电路包含正电位点或者负电位点,所述高压静电防护器件的阳极、阴极分别与电路电源负极、正电位点连接或者所述高压静电防护器件的阳极、阴极分别与负电位点、电路电源正极连接。

区别于现有技术,上述技术方案结构简单,可以实现高压静电防护,同时能够提供负电位的保护,且具有较强的兼容性,能够用于不同的工艺和耐压。

附图说明

图1为背景技术所述一种简单结构的高压NMOS管剖面结构图;

图2为背景技术所述一种SCR静电防护器件结构图;

图3为本发明一种可选方案的剖面结构示意图;

图4为本发明一实施例的可靠性分析结果图;

图5是本发明另一种可选方案的器件剖面结构示意图;

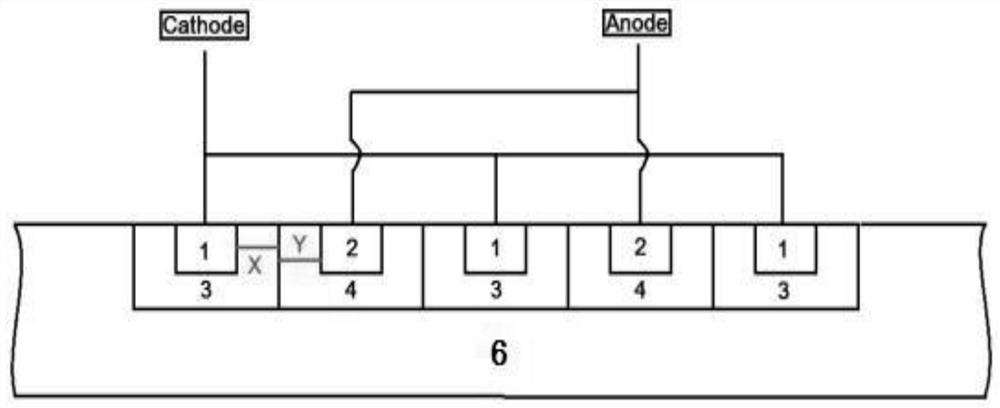

图6是图5所示器件的俯视图。

附图标记说明:

1、N+注入区;

2、P+注入区;

3、N阱注入区;

4、P阱注入区;

5、N型隔离层;

6、P型衬底;

7、导电层。

具体实施方式

为详细说明技术方案的技术内容、构造特征、所实现目的及效果,以下结合具体实施例并配合附图详予说明。

请参阅图3到图6,本实施例提供一种高压静电防护器件,包括P型衬底6,所述P型衬底上设置有N型隔离层5,所述N型隔离层5上设置有N阱注入区3和P阱注入区4,所述N阱注入区3和P阱注入区4并排设置。所述N阱注入区3顶部中间设置有N+注入区1,即N阱注入区3的内部设置有N+注入区1。所述P阱注入区4顶部中间设置有P+注入区2,即P阱注入区4内部设置有P+注入区2。N+注入区1用于作为器件的阴极(Cathode),P+注入区2用于作为器件的阳极(Anode)。

上述静电防护器件阴极接防护电压点(正),阳极接地;或器件阳极接防护电压点(负),阴极接电源。当ESD器件工作在正向到导通时,通过正偏结将ESD电流泄放到电源或地上;当ESD器件工作在反向截止时,通过反偏结的反向击穿,使ESD电流泄放到地。通过可靠性试验,如图4所示,上述静电防护器件可以实现±2000V的静电防护,作为高压ESD防护是可行的。

反向击穿电压决定了ESD电流泄放的速度。根据不同的工艺和芯片耐压,可以通过调节X(N+注入区1与P+注入区2之间N阱注入区3)和Y(P+注入区2与N+注入区1之间P阱注入区4的)的尺寸选择合适的反向击穿电压,即所述N+注入区1与P+注入区2之间的所述N阱注入区3和P阱注入区4的尺寸与器件耐压值相关。这使上述静电防护器件具有很高的兼容性。

上述静电防护器件,所述N阱注入区3内包括有N+注入区1可用半导体工艺最小尺寸;所述P阱注入区4内包括P+注入区2可用半导体工艺最小尺寸。在一可选实施例中,若对地做ESD保护,阳极接电源负极VSS,即P阱注入区4中的P+注入区2接VSS,可将N型隔离层5省去。

为了加快器件电流泄放,所述N阱注入区3和P阱注入区4的数量为多个,所述N阱注入区3和P阱注入区4依次循环列,相邻的所述N阱注入区3之间设置有P阱注入区4,相邻的所述P阱注入区4之间设置有N阱注入区3。而后阳极应当与多个的N+注入区1进行连接,阴极应当与多个的P+注入区2连接。在某些实施例中,所述为高压器件,P型衬底6外侧包覆在N阱注入区3和P阱注入区4的四周,及N阱注入区3和P阱注入区4陷入在P型衬底6中,可使所述器件阴极与P型衬底之间承受高压差。

如图6所示,所述器件表面覆盖有场氧化层,所述场氧化层上设置导电层7,所述导电层分别与N+注入区1、P+注入区2连接。优选的,所述导电层为金属层。场氧化层用于起到绝缘的作用,导电层用于实现对N+注入区1的连接,不同的导电层还用于实现P+注入区2,从而通过连接导电层可以实现与N+注入区1或者P+注入区2的连接。

本发明提供一种高压静电防护电路,所述电路包含有高压静电防护器件,所述高压静电防护器件为本发明任意一项实施例所述的高压静电防护器件,即上述的静电防护器件可以应用于集成电路中。所述电路包含正电位点(正电位PAD)或者负电位点(负电位PAD),所述高压静电防护器件的阳极、阴极分别与电路电源负极、正电位点连接或者所述高压静电防护器件的阳极、阴极分别与负电位点、电路电源正极连接。其具体线路连接方式如下:1.当PAD电位为正电位时,Cathode端接PAD,即N阱注入区3中的N+注入区1接PAD;Anode接VSS,即P阱注入区4中的P+注入区2接VSS。2.当PAD电位出现负电位是,Cathode接电源正极VDD,即N阱注入区3中的N+注入区1接VDD;Anode接PAD,即P阱注入区4中的P+注入区2接PAD。从而实现电路的正电位点或者负电位点的高压静电防护。

需要说明的是,尽管在本文中已经对上述各实施例进行了描述,但并非因此限制本发明的专利保护范围。因此,基于本发明的创新理念,对本文所述实施例进行的变更和修改,或利用本发明说明书及附图内容所作的等效结构或等效流程变换,直接或间接地将以上技术方案运用在其他相关的技术领域,均包括在本发明的专利保护范围之内。

- 一种高压静电防护器件和电路

- 一种应用于深亚微米级电路静电防护的可控硅器件