应用于伪静态随机存取存储器的控制电路及其控制方法

文献发布时间:2023-06-19 11:27:38

技术领域

本发明涉及一种应用于存储器装置的控制电路以及控制方法,尤其涉及一种应用于伪静态随机存取存储器的控制电路以及控制方法,用以产生行地址选通时脉信号与控制信号以供伪静态随机存取存储器产生行选择线信号。

背景技术

随着半导体存储器元件的整合水准变得愈来愈高,而存在对更高速度的需求,静态随机存取存储器(SRAM)及动态随机存取存储器(DRAM)作为高速存储器被使用。对于具有动态随机存取存储器的优点的伪静态随机存取存储器(pSRAM)的需求持续增加,特别是运用在行动装置中。

在伪静态随机存取存储器中,因为没有由使用者发出的更新命令,动态随机存取存储器需执行自更新操作。现有的伪静态随机存取存储器运用计数器来切换同步模式与非同步模式。于非同步模式中,写入操作以较外部时脉周期更短的周期来非同步完成,以吸收自更新操作的时间。于同步模式中,写入操作以与外部时脉相同的周期而同步完成。然而,依情况不同,这将导致同步写入模式中用以产生行选择线信号(Column Selection Linesignal,CSL signal)的脉冲宽度太短,进而导致伪静态随机存取存储器故障。

发明内容

本发明提供一种用于伪静态随机存取存储器的控制电路及其控制方法,可以在写入操作中动态延迟或省略用以产生行选择线信号的前导信号的脉冲,以避免伪静态随机存取存储器故障。

本发明的控制电路适用于伪静态随机存取存储器,控制电路包括写入数据判断电路与时脉产生电路。写入数据判断电路配置为计数并比较伪静态随机存取存储器的数据输入次数与数据实际写入次数以产生写入匹配信号,并依据计数伪静态随机存取存储器的数据输入次数来产生写入计数时脉信号。时脉产生电路耦接写入数据判断电路,时脉产生电路配置为依据写入匹配信号与写入计数时脉信号以产生前导信号,并依据前导信号产生行地址选通时脉信号与控制信号,其中时脉产生电路依据写入匹配信号与写入计数时脉信号决定是否动态延迟前导信号以延迟或省略伪静态随机存取存储器的行选择线信号的脉冲。

本发明的控制方法适用于伪静态随机存取存储器,该控制方法包括:计数并比较伪静态随机存取存储器的数据输入次数与数据实际写入次数以产生写入匹配信号,并依据该计数伪静态随机存取存储器的数据输入次数来产生写入计数时脉信号。依据写入匹配信号与写入计数时脉信号以产生前导信号,并依据前导信号产生行地址选通时脉信号与控制信号,其中依据写入匹配信号与写入计数时脉信号以产生前导信号的步骤包括依据写入匹配信号与写入计数时脉信号决定是否动态延迟前导信号以延迟或省略伪静态随机存取存储器的行选择线信号的脉冲。

基于上述,本发明的控制电路与控制方法调整前导信号的时序来产生具有适当时序的行选择线信号,以避免伪静态随机存取存储器故障或不稳定操作。本发明通过计数与比较伪静态随机存取存储器的数据输入次数与实际写入次数来产生前导信号,并决定是否动态延迟前导信号以延迟或省略行选择线信号的脉冲,从而避免行选择线信号的脉冲宽度过短。因此,可避免伪静态随机存取存储器故障或不稳定操作,并产生必要数量的行选择线信号。通过本发明,伪静态随机存取存储器可以实现更高的操作频率。

为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

附图说明

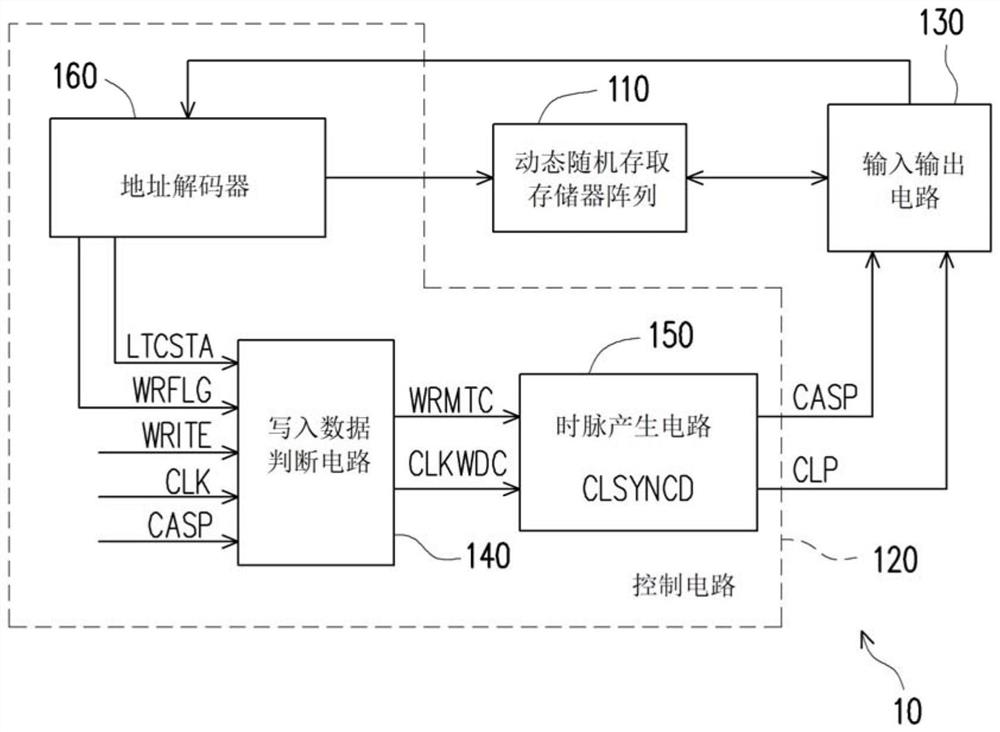

图1是本发明实施例的伪静态随机存取存储器的示意图;

图2是本发明实施例的写入数据判断电路的示意图;

图3是本发明实施例的时脉产生电路示意图;

图4A~图4C是本发明实施例的切换非同步模式与同步模式的控制信号时序图;

图5A是本发明实施例的比较器的电路图;

图5B是本发明实施例用于比较器的信号产生电路的电路图;

图6A是本发明实施例的同步控制电路的电路图;

图6B是本发明实施例的同步控制电路的信号产生电路的电路图;

图7是本发明实施例的非同步控制电路的电路图;

图8是本发明实施例的同步行地址选通时脉控制器的电路图;

图9是本发明实施例的非同步行地址选通时脉控制器的电路图;

图10是本发明实施例的单发脉冲产生器的电路图;

图11是本发明另一实施例的控制信号时序图;

图12A~图12C是本发明再一实施例的控制信号时序图;

图13是本发明一实施例的控制方法的流程图。

附图标记说明

10:伪静态随机存取存储器

110:动态随机存取存储器阵列

120:控制电路

130:输入输出电路

140:写入数据判断电路

150:时脉产生电路

160:地址解码器

210、220:计数器

230:比较器

310:同步与非同步控制器

320:延迟计数器

330:同步行地址选通时脉控制器

340:非同步行地址选通时脉控制器

350:单发脉冲产生器

360:时脉调整器

370:同步控制电路

380:非同步控制电路

550、650、660、930、1010:延迟电路

510、520、530、610、620、710、720、730、810、820:逻辑电路

CASASP:非同步基础信号

CASP:行地址选通时脉信号

CASP_t:反相行地址选通时脉信号

CASPD_t、CASPDB_c、CASPRP_c、CASSP_t、CLCLWAIT_c、CLKD_c、CLKD_t、CLKD2_t、CLKWDC3_t、CLP、CLPSTP_t、CON1、EN_t、IND_t、PCASP_c、PWRMTC_c、WR_t:控制信号

CASSP2:同步基础信号

CASSPMASK:同步基础禁止生成信号

CHRDY_t:芯片上电完成确认信号

CLK:基准时脉信号

CLKWDC:写入计数时脉信号

CLPTRIG、CLPTRIGSL_t:触发状态信号

CLSYNC:同步决定信号

CLSYNCD、CLSYNCD2_t:前导信号

CLSYNCDB:反相前导信号

CNTDIN<3:0>、CNTDIN<0>、CNTDIN<1>、CNTDIN<2>、CNTDIN<3>:数据输入次数

CNTDWR<3:0>、CNTDWR<0>、CNTDWR<1>、CNTDWR<2>、CNTDWR<3>:数据实际写入次数

FLGD_t:旗标信号

INV1~INV18:反相闸

LTCSTA:计数起始信号

LTNCY:延迟控制信号

MODE、MODE1:模式信号

N+1、N+2、N+3、N+4:脉冲

n01~n04、n08~n09、n19:节点

N1~N4、P1~P4:晶体管

NAND1~NAND11:反及闸

NDIN:数据输入次数

NDWR:数据实际写入次数

NOR1~NOR4:反或闸

OR1~OR4:或门

RCDRDY:延迟就绪信号

WRFLG:写入旗标信号

WRITE:写入控制信号

WRMTC:写入匹配信号

具体实施方式

请参照图1,图1是依照本发明实施例的伪静态随机存取存储器10的示意图。伪静态随机存取存储器10包括动态随机存取存储器阵列110、控制电路120、输入输出电路130。动态随机存取存储器阵列110,包括多个字线与多个存储单元(未绘示),用以储存数据,本发明并未限制动态随机处理存储器阵列的架构。控制电路120耦接至动态随机存取存储器阵列110,控制电路120包括写入数据判断电路140、时脉产生电路150与地址解码器160。地址解码器160耦接写入数据判断电路140、动态随机存取存储器阵列110与输入输出电路130,地址解码器160可产生对应执行操作的计数起始信号LTCSTA与写入旗标信号WRFLG,并将计数起始信号LTCSTA与写入旗标信号WRFLG提供给写入数据判断电路140。写入数据判断电路140接收并依据计数起始信号LTCSTA、写入旗标信号WRFLG、写入控制信号WRITE、基准时脉信号CLK与行地址选通时脉信号CASP来产生写入匹配信号WRMTC与写入计数时脉信号CLKWDC。时脉产生电路150耦接在写入数据判断电路140和输入输出电路130之间,时脉产生电路150接收并依据写入匹配信号WRMTC与写入计数时脉信号CLKWDC产生前导信号CLSYNCD,并依据该前导信号产生行地址选通时脉信号CASP与控制信号CLP。其中时脉产生电路150依据写入匹配信号WRMTC与写入计数时脉信号CLKWDC来决定是否动态延迟前导信号CLSYNCD以延迟或省略行选择线信号CSL(未绘示)的脉冲。输入输出电路130耦接至动态随机存取存储器阵列110与控制电路120,进一步说,输入输出电路130耦接在地址解码器160与时脉产生电路150之间。输入输出电路130从控制电路120接收行地址选通时脉信号CASP与控制信号CLP以产生行选择线信号CSL,并依据行选择线信号CSL将写入数据依序写入至动态随机存取存储器阵列110。

在图1中,写入数据判断电路140用以计数并比较伪静态随机存取存储器10的数据输入次数与数据实际写入次数以产生写入匹配信号WRMTC。其中数据输入次数为依据基准时脉信号CLK将数据由伪静态随机存取存储器10的外部输入至伪静态随机存取存储器10的次数,数据实际写入次数为依据行地址选通时脉信号CASP将数据由伪静态随机存取存储器10的内部写入至动态随机存取存储器阵列110的次数。写入数据判断电路140并依据伪静态随机存取存储器的数据输入次数的计数操作来产生写入计数时脉信号CLKWDC。关于写入计数时脉信号CLKWDC的产生方式,如后文所述。当写入至动态随机存取存储器阵列110的数据输入次数等于从外部输入至伪静态随机存取存储器10的数据实际写入次数时,写入匹配信号WRMTC为低逻辑电平,以表示将数据写入至动态随机存取存储器阵列110的速度已相当于数据由外部输入至输入输出电路130的速度。

时脉产生电路150配置为在当接收到低逻辑电平的写入匹配信号WRMTC时,依据低逻辑电平的写入匹配信号WRMTC与写入计数时脉信号CLKWDC来动态延迟前导信号CLSYNCD,以动态调整行地址选通时脉信号CASP与控制信号CLP的时序。时脉产生电路150并将行地址选通时脉信号CASP的周期调整为与基准时脉信号CLK的周期相同,以便写入操作可以从非同步模式转换成同步模式。

在一实施例中,当数据输入次数大于数据实际写入次数时,时脉产生电路150调整行地址选通时脉信号CASP与控制信号CLP的时序,而使伪静态随机存取存储器10以比基准时脉信号CLK更短的周期来进行非同步写入操作。当该数据输入次数小于等于数据实际写入次数时,时脉产生电路150调整行地址选通时脉信号CASP与控制信号CLP的时序,而使伪静态随机存取存储器10以相同于基准时脉信号CLK的周期进行同步写入操作。

图2是依照本发明实施例的写入数据判断电路140的示意图。请参照图2,写入判断电路140包括计数器210、计数器220与比较器230。

计数器210接收写入控制信号WRITE、计数起始信号LTCSTA与基准时脉信号CLK。在写入操作中,计数器210依据写入控制信号WRITE、计数起始信号LTCSTA与基准时脉信号CLK而计数“将数据由伪静态随机存取存储器10的外部输入至伪静态随机存取存储器10的次数”,以产生数据输入次数NDIN。

计数器220接收写入旗标信号WRFLG与行地址选通时脉信号CASP。在写入操作中,计数器220依据写入旗标信号WRFLG与行地址选通时脉信号CASP而计数“将数据由伪静态随机存取存储器10的内部写入至动态随机存取存储器阵列110的次数”,以产生数据实际写入次数NDWR。

比较器230耦接计数器210与计数器220,比较器230用以比较数据输入次数NDIN与数据实际写入次数NDWR。当数据输入次数NDIN等于数据实际写入次数NDWR时,写入匹配信号WRMTC为低逻辑电平。当数据输入次数NDIN大于数据实际写入次数NDWR时,写入匹配信号WRMTC为高逻辑电平。在一实施例中,计数器210还依据写入控制信号WRITE、计数起始信号LTCSTA与基准时脉信号CLK而产生写入计数时脉信号CLKWDC并提供至时脉产生电路150,以作为时脉产生电路150进行非同步控制的前导控制信号。

图3是本发明实施例的时脉产生电路150示意图。请参照图3,时脉产生电路150包括同步与非同步控制器310、延迟计数器320、同步行地址选通时脉控制器330、非同步行地址选通时脉控制器340、单发脉冲产生器350与时脉调整器360。其中延迟计数器320与时脉调整器360可分别是传统计数器与传统延迟电路,本发明不限于此。

同步与非同步控制器310耦接至写入数据判断电路140,同步与非同步控制器310具有同步控制电路370与非同步控制电路380。同步与非同步控制器310接收写入计数时脉信号CLKWDC、写入匹配信号WRMTC、基准时脉信号CLK、行地址选通时脉信号CASP与对应执行操作模式的模式信号MODE,同步与非同步控制器310依据写入匹配信号WRMTC来判断是否同步以及进行同步控制以产生同步决定信号CLSYNC与前导信号CLSYNCD,并依据该写入计数时脉信号CLKWDC、同步决定信号CLSYNC与该前导信号CLSYNCD来进行非同步控制以产生同步基础禁止生成信号CASSPMASK与反相前导信号CLSYNCDB。

延迟计数器320接收基准时脉信号CLK、延迟控制信号LTNCY、计数起始信号LTCSTA与模式信号MODE,延迟计数器320依据延迟控制信号LTNCY、计数起始信号LTCSTA与模式信号MODE来计数以产生触发状态信号CLPTRIG,并提供至同步行地址选通时脉控制器330与非同步行地址选通时脉控制器340。当依据计数起始信号LTCSTA在开始计数经过预定延迟时间后,延迟计数器320产生具高逻辑电平的触发状态信号CLPTRIG。

同步行地址选通时脉控制器330耦接同步与非同步控制器310以及延迟计数器320,同步行地址选通时脉控制器330接收同步决定信号CLSYNC、基准时脉信号CLK与触发状态信号CLPTRIG。当同步决定信号CLSYNC与触发状态信号CLPTRIG皆为高逻辑电平时,表示已转换为同步模式,同步行地址选通时脉控制器330可依据基准时脉信号CLK而对应产生同步基础信号CASSP2。

非同步行地址选通时脉控制器340耦接同步与非同步控制器310、同步行地址选通时脉控制器330与单发脉冲产生器350,接收同步基础禁止生成信号CASSPMASK、触发控制信号CLPTRIGSL_t、延迟就绪信号RCDRDY与行地址选通时脉信号CASP。当延迟就绪信号RCDRDY为高逻辑电平且同步决定信号CLSYNC为低逻辑电平时,表示目前为非同步模式,因此非同步行地址选通时脉控制器340可对应产生非同步基础信号CASASP。进一步说,在非同步模式下,非同步行地址选通时脉控制器340可依据同步基础禁止生成信号CASSPMASK、触发控制信号CLPTRIGSL_t、延迟就绪信号RCDRDY与行地址选通时脉信号CASP而对应产生非同步基础信号CASASP并提供至单发脉冲产生器350。其中当延迟就绪信号RCDRDY为高逻辑电平时,即表示列地址的系统操作如字线和感应放大器已驱动就绪完成,行地址的系统操作可准备开始。也就是说,在写入操作时,可开始将数据由输入输出电路130中的缓冲器写入至动态随机存取存储器阵列110的存储单元中。其中延迟就绪信号RCDRDY是一种状态信号,当内部经过列控制器至行控制器传输延时间tRCD(未绘示)且行选择线信号CSL的产生就绪时,延迟就绪信号RCDRDY转态为高逻辑电平。必须注意的是,当启动状态完成后,控制电路120会重置(reset)延迟就绪信号RCDRDY。

单发脉冲产生器350耦接同步与非同步控制器310、同步行地址选通时脉控制器330与非同步行地址选通时脉控制器340,单发脉冲产生器350并接收同步基础禁止生成信号CASSPMASK、延迟就绪信号RCDRDY、反相前导信号CLSYNCDB、同步基础信号CASSP2、同步决定信号CLSYNC与非同步基础信号CASASP。在一实施例中,单发脉冲产生器350在非同步模式时依据非同步基础信号CASASP而对应产生行地址选通时脉信号CASP,在同步模式时依据同步基础信号CASSP2而对应产生行地址选通时脉信号CASP。在一实施例中,在单发脉冲产生器350中可例如将非同步基础信号CASASP与同步基础信号CASSP2通过或运算(ORoperation)来进行选择,并根据所选择的信号,在延迟就绪信号RCDRDY为高逻辑电平后产生预定脉宽的单发脉冲以形成行地址选通时脉信号CASP。行地址选通时脉信号CASP还被回授至非同步行地址选通时脉控制器340,以对后续的非同步基础信号CASASP进行调整。

时脉调整器360耦接单发脉冲产生器350,时脉调整器360接收行地址选通时脉信号CASP,并依据行地址选通时脉信号CASP在经预定延迟时间后产生控制信号CLP。

图4A~图4C是本发明实施例的切换非同步模式与同步模式的控制信号时序图。请同时参照图1、图3与图4A~图4C,控制电路120通过行地址选通时脉信号CASP、同步决定信号CLSYNC和前导信号CLSYNCD的操作波形,以在非同步模式和同步模式之间改变操作模式。具体来说,在行地址选通时脉信号CASP转态为高逻辑电平时,同步决定信号CLSYNC转态为高逻辑电平。前导信号CLSYNCD的转态条件例如是在同步决定信号CLSYNC转态为高逻辑电平后,当基准时脉信号CLK为低逻辑电平时,前导信号CLSYNCD会被转态为高逻辑电平。举例来说,在图4A的情境中,当同步决定信号CLSYNC转态为高逻辑电平时,由于此时基准时脉信号CLK为低逻辑电平,控制电路120经运算后将前导信号CLSYNCD转态为高逻辑电平,接着同步基础信号CASSP2的脉冲N+1和脉冲N+2将在前导信号CLSYNCD被转态为高逻辑电平后依序产生,并分别成为行地址选通时脉信号CASP的脉冲N+1和脉冲N+2的产生基准。行选择线信号CSL的脉冲N、脉冲N+1和脉冲N+2分别与行地址选通时脉信号CASP的脉冲N、脉冲N+1和脉冲N+2同步。在图4B的情境中,当同步决定信号CLSYNC转态为高逻辑电平时,由于此时基准时脉信号CLK为高逻辑电平,控制电路120在经运算后,在基准时脉信号CLK转态为低逻辑电平时将前导信号CLSYNCD转态为高逻辑电平。接着同步基础信号CASSP2的脉冲N+1将在前导信号CLSYNCD被转态为高逻辑电平后产生,并成为行地址选通时脉信号CASP的脉冲N+1的产生基准。行选择线信号CSL的脉冲N、脉冲N+1分别与行地址选通时脉信号CASP的脉冲N、脉冲N+1同步因此,在图4B的情境中,基于同步基础信号CASSP2的脉冲N+1产生的行选择线信号CSL的脉冲N+1被延迟,以避免脉冲N+1的脉冲宽度过短而使得伪静态随机存取存储器10故障。在图4C的情境中,当同步决定信号CLSYNC转态为高逻辑电平时,此时基准时脉信号CLK为高逻辑电平。接着在基准时脉信号CLK转态为低逻辑电平时,行地址选通时脉信号CASP为低逻辑电平。因此控制电路120经运算后,在行地址选通时脉信号CASP转态为高逻辑电平时,将前导信号CLSYNCD转态为高逻辑电平。接着同步基础信号CASSP2的脉冲N+2将在前导信号CLSYNCD被转态为高逻辑电平后产生,并成为行地址选通时脉信号CASP的脉冲N+2的产生基准。因此,在图4C的情境中,基于同步基础信号CASSP2的脉冲N+1产生的行选择线信号CSL的脉冲N+1被省略,以避免脉冲N+1的脉冲宽度过短,而使得伪静态随机存取存储器10故障。

图5A是本发明实施例的比较器230的电路图。请同时参照图2与图5A,比较器230用以比较数据输入次数NDIN与数据实际写入次数NDWR。当数据输入次数NDIN等于数据实际写入次数NDWR时,写入匹配信号WRMTC被转态为高逻辑电平。

逻辑电路510耦接计数器210与计数器220,逻辑电路510接收数据输入次数NDIN与数据实际写入次数NDWR,经逻辑运算以产生控制信号PWRMTC_c。具体而言,逻辑电路510包括或门OR1~OR4、反或闸NOR1~NOR2与反及闸NAND1。数据输入次数NDIN包括数据输入次数CNTDIN<3:0>,数据实际写入次数NDWR包括数据实际写入次数CNTDWR<3:0>。或门OR1接收数据输入次数CNTDIN<0>与数据实际写入次数CNTDWR<0>,或门OR2接收数据输入次数CNTDIN<1>与数据实际写入次数CNTDWR<1>,或门OR3接收数据输入次数CNTDIN<2>与数据实际写入次数CNTDWR<2>,或门OR4接收数据输入次数CNTDIN<3>与数据实际写入次数CNTDWR<3>。逻辑电路510通过或门OR1~OR4、反或闸NOR1~NOR2与反及闸NAND1而进行逻辑运算后,由反及闸NAND1产生控制信号PWRMTC_c。

逻辑电路520耦接逻辑电路510,逻辑电路520接收控制信号EN_t与控制信号PWRMTC_c,经逻辑运算后产生旗标信号FLGD_t与控制信号CON1。具体而言,逻辑电路520包括晶体管P1~P2、晶体管N1~N2、反相闸INV1~INV5、反或闸NOR3与反及闸NAND2。晶体管P1的栅极端接收控制信号CASPDB_c,反相闸INV1与反相闸INV2的输入端接收控制信号EN_t,晶体管N1的栅极端接收控制信号CASPD_t。晶体管P2的栅极端接收控制信号CASPD_t,反相闸INV4的输入端接收控制信号PWRMTC_c,晶体管N2的栅极端接收控制信号CASPDB_c。逻辑电路520通过晶体管P1~P2、晶体管N1~N2、反相闸INV1~INV5、反或闸NOR3与反及闸NAND2进行逻辑运算后,由反或闸NOR3与反及闸NAND2产生旗标信号FLGD_t与控制信号CON1。

逻辑电路530耦接逻辑电路520,逻辑电路530接收旗标信号FLGD_t与控制信号CON1,经逻辑运算后产生写入匹配信号WRMTC。具体而言,逻辑电路530包括反及闸NAND3~NAND5与反相闸INV6。反及闸NAND3的一输入端接收控制信号CON1,反及闸NAND4的一输入端接收旗标信号FLGD_t、控制信号EN_t与芯片上电完成确认信号CHRDY_t。逻辑电路530通过反及闸NAND3~NAND5与反相闸INV6进行逻辑运算后,由反及闸NAND5产生写入匹配信号WRMTC。

参照图5A,数据输入次数CNTDIN<3:0>与数据实际写入次数CNTDWR<3:0>被比较,而比较结果基于控制信号CASPD_t与控制信号CASPDB_c的时序被闩锁,其中控制信号CASPD_t与控制信号CASPDB_c通过延迟行地址选通时脉信号CASP而产生。值得一提的是,为了产生用以判断数据输入次数NDIN是否相等于数据实际写入次数NDWR的写入匹配信号WRMTC,比较器230具有数字滤波器结构以转换判断结果的脉冲,其中脉冲的宽度足够在写入匹配信号WRMTC稳定后执行操作。控制信号EN_t是状态信号,当芯片致能信号(未绘示)变为高逻辑电平时,控制信号EN_t变为高逻辑电平。当伪静态随机存取存储器10完成启动状态且转移至预充电状态时,控制信号EN_t变为低逻辑电平。

图5B是本发明实施例用于比较器230的信号产生电路540的电路图。参照图5B,信号产生电路540包括反相器INV7~INV8与延迟电路550。信号产生电路540用以接收行地址选通时脉信号CASP与模式信号MODE1以产生反相行地址选通时脉信号CASP_t、控制信号CASPD_t与控制信号CASPDB_c。具体而言,反相器INV7接收行地址选通时脉信号CASP,经反相以产生反相行地址选通时脉信号CASP_t。延迟电路550接收反相行地址选通时脉信号CASP_t与模式信号MODE1,延迟电路550依据模式信号MODE1决定所选模式例如是测试模式或者熔丝模式以决定延迟时间,并延迟反相行地址选通时脉信号CASP_t,以产生控制信号CASPD_t。反相器INV8接收控制信号CASPD_t,经反相以产生控制信号CASPDB_c。

图6A是本发明实施例的同步控制电路370的电路图。参照图3与图6A,同步控制电路370接收写入匹配信号WRMTC、写入旗标信号WRFLG与行地址选通时脉信号CASP,用以依据写入匹配信号WRMTC来判断以外部时脉(基准时脉信号CLK)写入与以内部时脉(行地址选通时脉信号CASP)写入是否同步,并进行同步控制以产生同步决定信号CLSYNC与前导信号CLSYNCD。具体而言,同步控制电路370包括逻辑电路610~630。

逻辑电路610包括反及闸NAND6,反及闸NAND6接收写入匹配信号WRMTC、写入旗标信号WRFLG,经反及运算后产生同步决定信号CLSYNC。

逻辑电路620耦接逻辑电路610,逻辑电路620接收同步决定信号CLSYNC,经逻辑运算以产生控制信号IND_t。逻辑电路620包括晶体管P3、晶体管N3、反相闸INV9~INV10与反及闸NAND7。晶体管P3的栅极接收控制信号CLKD_t,反相闸INV9的输入端接收同步决定信号CLSYNC,晶体管N3的栅极接收控制信号CLKD_c。反及闸NAND7的一输入端接收控制信号EN_t,反及闸NAND7的输出端提供控制信号IND_t。反相闸INV10的输入端接收控制信号IND_t。

逻辑电路630耦接逻辑电路620,逻辑电路630接收控制信号IND_t,经逻辑运算以产生前导信号CLSYNCD。逻辑电路630包括晶体管P4、晶体管N4、反相闸INV11~INV13与反或闸NOR4。晶体管P4的栅极接收反相行地址选通时脉信号CASP_t,反相闸INV11的输入端接收控制信号IND_t,晶体管N4的栅极接收行地址选通时脉信号CASP。反相闸INV12的输入端接收同步决定信号CLSYNC,反或闸的输出端提供前导信号CLSYNCD。反相闸INV13的输入端接收前导信号CLSYNCD。

参照图6A,在写入操作中,写入旗标信号WRFLG为高逻辑电平,且写入匹配信号WRMTC在写入操作的起始也为高逻辑电平,因此经反及闸NAND6进行反及运算后,产生低逻辑电平的同步决定信号CLSYNC。接着,当写入匹配信号WRMTC变为低逻辑电平时,同步决定信号CLSYNC即转态为高逻辑电平,其中同步决定信号CLSYNC被转态为高逻辑电平的时点落于控制信号CLKD_t、控制信号CLKD_c和控制信号IND_t被产生的时点,且同步决定信号CLSYNC在行地址选通时脉信号CASP为高逻辑电平的时期被转态。

图6B是本发明实施例的同步控制电路370的信号产生电路640的电路图。参照图6B,信号产生电路640包括延迟电路650、反相器INV14~INV15与延迟电路660。信号产生电路640用以接收基准时脉信号CLK与模式信号MODE1以产生控制信号CLKD_t、控制信号CLKD_c与控制信号CLKD2_t。具体而言,延迟电路650接收基准时脉信号CLK与模式信号MODE1,延迟电路650依据模式信号MODE1决定所选模式例如是测试模式或者熔丝模式以决定延迟时间,并延迟基准时脉信号CLK,以产生控制信号CLKD_t。反相器INV14接收控制信号CLKD_t,经反相以产生控制信号CLKD_c。反相器INV15的输入端接收控制信号CLKD_c。延迟电路660耦接反相器INV15的输出端,延迟电路660依据模式信号MODE1决定所选模式例如是测试模式或者熔丝模式以决定延迟时间,并进行延迟操作以产生控制信号CLKD2_t。

图7是本发明实施例的非同步控制电路380的电路图。参照图7,非同步控制电路380用以依据写入计数时脉信号CLKWDC、同步决定信号CLSYNC与前导信号CLSYNCD来产生同步基础禁止生成信号CASSPMASK与反相前导信号CLSYNCDB。非同步控制电路380包括逻辑电路710~730。

逻辑电路710耦接写入数据判断电路140中的计数器210以接收写入计数时脉信号CLKWDC。逻辑电路710依据写入计数时脉信号CLKWDC、行地址选通时脉信号CASP、反相行地址选通时脉信号CASP_t与前导信号CLSYNCD,来产生控制信号CLKWDC3_t。

逻辑电路720耦接逻辑电路710以接收控制信号CLKWDC3_t,并耦接逻辑电路730以接收控制信号CASPRP_c。逻辑电路720依据控制信号CLKWDC3_t、控制信号CASPRP_c、控制信号CLKD_t、芯片上电完成确认信号CHRDY_t、同步决定信号CLSYNC与控制信号CLKD2_t,以提供同步基础禁止生成信号CASSPMASK至单发脉冲产生器350。其中,当芯片上电仍未结束时,芯片上电完成确认信号CHRDY_t为低逻辑电平,当芯片上电结束时,芯片上电完成确认信号CHRDY_t为高逻辑电平。

逻辑电路730耦接逻辑电路720,用以依据控制信号PCASP_c、同步决定信号CLSYNC、控制信号CLKD_t、芯片上电完成确认信号CHRDY_t、前导信号CLSYNCD、前导信号CLSYNCD2_t,以提供反相前导信号CLSYNCDB至单发脉冲产生器350。

图8是本发明实施例的同步行地址选通时脉控制器330的电路图。参照图8,同步行地址选通时脉控制器330接收基准时脉信号CLK、该同步决定信号CLSYNC与触发状态信号CLPTRIG以产生对应的同步基础信号CASSP2。同步行地址选通时脉控制器330包括逻辑电路810与逻辑电路820。

逻辑电路810接收触发状态信号CLPTRIG、同步决定信号CLSYNC与基准时脉信号CLK。逻辑电路810依据触发状态信号CLPTRIG、控制信号CLPSTP_t、旗标信号FLG_t、基准时脉信号CLK、同步决定信号CLSYNC、芯片上电完成确认信号CHRDY_t、与同步基础禁止生成信号CASSPMASK_t,以产生控制信号CASSP_t。其中触发控制信号CLPTRIGSL_t为逻辑电路810中产生的信号。节点n01~n02为逻辑电路810中的电压节点。控制信号CLPSTP_t是脉冲信号,当完成启动状态时,控制信号CLPSTP_t变为高逻辑电平并转移至预充电状态。旗标信号FLG_t是一种状态信号,旗标信号FLG_t在开始进行延迟时间的计数时变为高逻辑电平,在完成启动状态时变为低逻辑电平并转移到预充电状态。

逻辑电路820耦接逻辑电路810,逻辑电路820接收控制信号CASSP_t、控制信号CLCLWAIT_c、芯片上电完成确认信号CHRDY_t、非同步基础信号CASASP以提供同步基础信号CASSP2至单发脉冲产生器350。其中信号CASSPL_t为逻辑电路820中产生的信号。节点n03~n04为逻辑电路820中的电压节点。

必须注意的是,当启动状态完成后,控制电路120会重置(reset)芯片上电完成确认信号CHRDY_t、控制信号CLPSTP_t、旗标信号FLG_t、同步基础禁止生成信号CASSPMASK与触发状态信号CLPTRIG等信号。

图9是本发明实施例的非同步行地址选通时脉控制器340的电路图。参照图9,非同步行地址选通时脉控制器340接收行地址选通时脉信号CASP、同步基础禁止生成信号CASSPMASK、延迟就绪信号RCDRDY与触发控制信号CLPTRIGSL_t以产生对应的非同步基础信号CASASP。非同步行地址选通时脉控制器340包括逻辑电路910与逻辑电路920。

逻辑电路910依据行地址选通时脉信号CASP、模式信号MODE1、控制信号CHRDY_t以提供控制信号CLCLWAIT_c至同步行地址选通时脉控制器330中的逻辑电路820。其中节点n05~n07为逻辑电路910中的电压节点,且延迟电路930接收模式信号MODE1以决定延迟时间。

逻辑电路920耦接逻辑电路910,用以依据延迟就绪信号RCDRDY、触发控制信号CLPTRIGSL_t、芯片上电完成确认信号CHRDY_t、同步基础禁止生成信号CASSPMASK、控制信号CLPSTP_t来提供非同步基础信号CASASP至单发脉冲产生器350。其中节点n08~n10为逻辑电路920中的电压节点。

图10是本发明实施例的单发脉冲产生器350的电路图。参照图10,单发脉冲产生器350接收同步基础禁止生成信号CASSPMASK、延迟就绪信号RCDRDY、反相前导信号CLSYNCDB、同步基础信号CASSP2、前导信号CLSYNCD与非同步基础信号CASASP。单发脉冲产生器350在非同步模式时根据非同步基础信号CASASP而产生对应的行地址选通时脉信号CASP,并在同步模式时根据同步基础信号CASSP2而产生对应的行地址选通时脉信号CASP。

单发脉冲产生器350包括反及闸NAND8~NAND11、反相闸INV16~INV18与延迟电路1010。反及闸NAND8的输入端接收非同步基础信号CASASP、反相前导信号CLSYNCDB与延迟就绪信号RCDRDY。反及闸NAND9的输入端接收同步基础信号CASSP2、前导信号CLSYNCD与延迟就绪信号RCDRDY。反及闸NAND10耦接反及闸NAND8与反及闸NAND9的输出端。当非同步基础信号CASASP、反相前导信号CLSYNCDB与延迟就绪信号RCDRDY皆为高逻辑电平,或同步基础信号CASSP2、前导信号CLSYNCD与延迟就绪信号RCDRDY皆为高逻辑电平时,反及闸NAND10会输出高逻辑电平至反及闸NAND11。反相闸INV16接收同步基础禁止生成信号CASSPMASK,延迟电路1010接收模式信号MODE1。反及闸NAND11耦接反相闸INV16、反及闸NAND10与延迟电路1010以产生控制信号PCASP_c。控制信号PCASP_c经反相器INV17~INV18缓冲而产生行地址选通时脉信号CASP。

承上所述,行地址选通时脉信号CASP是单发脉冲产生器350通过“基于非同步基础信号CASASP的非同步产生”与“基于同步基础信号CASSP2的同步产生”的“或运算”(ORoperation)而产生。并且,针对“基于非同步基础信号CASASP的非同步产生”与“基于同步基础信号CASSP2的同步产生”这两种情况,还需要高逻辑电平的延迟就绪信号RCDRDY以产生行地址选通时脉信号CASP。行地址选通时脉信号CASP的脉冲宽度由图10中的延迟电路1010所决定。其中,较佳实施例是将图2中计数器220接收行地址选通时脉信号CASP后所进行的延迟(未绘示)、图5B中延迟电路550对信号产生电路540接收的行地址选通时脉信号CASP所进行的延迟以及图9中延迟电路930对非同步行地址选通时脉控制器340所进行的延迟等三个延迟设计为由同种类的延迟元件所产生。因此可以在芯片制程、电压和温度方面具有相同的制程偏移(process variation),并得以在所有制程偏移都能获得足够的时间裕度(timing margin)。

回头参照图4A与图4B,当数据输入次数NDIN等于数据实际写入次数NDWR之后第一个同步模式的行选择线信号CSL被致能时,前导信号CLSYNCD可能在基准时脉信号CLK上升之前(图4A)或基准时脉信号CLK上升之后(图4B)被转态为高逻辑电平。然而,这可能导致行选择线信号CSL无法维持足够的区间(interval)或高逻辑电平时间。因此,本发明提供额外解决方案如下文所述。

图11是本发明另一实施例的控制信号时序图。参照图11,非同步基础信号CASASP在前导信号CLSYNCD变为高逻辑电平时,通过同步基础信号CASSP2和控制信号CLCLWAIT_c而进行延迟。从外部时脉(基准时脉信号CLK)为高逻辑电平和内部时脉(非同步基础信号CASASP)变为高逻辑电平后,行地址选通时脉信号CASP开始产生。并且,在行地址选通时脉信号CASP中必要脉冲宽度的延迟时间结束后,完成行地址选通时脉信号CASP的产生动作。接着,重置(reset)同步基础信号CASSP2与非同步基础信号CASASP。此外,行地址选通时脉信号CASP的当前脉冲与下一个脉冲之间的间隔可以通过控制信号CLCLWAIT_c为低逻辑电平的时间所维持。通过这种方法,即使当非同步基础信号CASASP被延迟到基准时脉信号CLK转态为高逻辑电平之前,或延迟到基准时脉信号CLK为高逻辑电平期间,行选择线信号CSL仍可以维持必要的脉冲宽度和间隔。

如图11所示,在非同步模式下,行地址选通时脉信号CASP的周期比基准时脉信号CLK周期短。因此,即使前导信号CLSYNCD被用于延迟行选择线信号CSL中的第一个同步脉冲,随着行选择线信号CSL的脉冲继续产生,基准时脉信号CLK和行选择线信号CSL之间的延迟会跟着减小,并且延迟会在行选择线信号CSL产生的几个周期之后被完全吸收。接着,行选择线信号CSL与基准时脉信号CLK的产生将会完全同步。

回头参照图4A~图4C和图11,当基准时脉信号CLK频率较低或芯片的制程偏移是快速角(fast corner)的情况下时,会产生比所需数量更多的行选择线信号CSL脉冲。针对该情况,本发明提供额外的实现方法如下。

图12A~图12C是本发明再一实施例的控制信号时序图。图12A~图12C示出了本发明通过行地址选通时脉信号CASP、同步决定信号CLSYNC、前导信号CLSYNCD、反相前导信号CLSYNCDB与同步基础禁止生成信号CASSPMASK来进行模式改变的另一种方法。当数据输入次数NDIN相等于数据实际写入次数NDWR(此时同步决定信号CLSYNC为高逻辑电平)并产生一个行选择线信号CSL脉冲之后,停止下一个行选择线信号CSL脉冲的产生直到基准时脉信号CLK(external CLK)变为低逻辑电平。以下陈述三种情况。

参照图12A,图12A为行地址选通时脉信号CASP并未被停止的示例。在基准时脉信号CLK变为高逻辑电平且同步决定信号CLSYNC变为高逻辑电平后,行地址选通时脉信号CASP变为低逻辑电平,接着基准时脉信号CLK变为低逻辑电平,行地址选通时脉信号CASP变为高逻辑电平,因此行地址选通时脉信号CASP并未被停止。

参照图12B,图12B为一种停止行地址选通时脉信号CASP的示例。在基准时脉信号CLK变为高逻辑电平且同步决定信号CLSYNC变为高逻辑电平后,行地址选通时脉信号CASP变为低逻辑电平(接着行地址选通时脉信号CASP变为高逻辑电平),因此可以透过前导信号CLSYNCD来停止非同步地产生行地址选通时脉信号CASP,直到基准时脉信号CLK转态为低逻辑电平。

参照图12C,图12C为另一种停止产生行地址选通时脉信号CASP的示例。在基准时脉信号CLK转态为高逻辑电平且行地址选通时脉信号CASP转态为低逻辑电平后(接着行地址选通时脉信号CASP变为高逻辑电平),同步决定信号CLSYNC转态为高逻辑电平且基准时脉信号CLK转态为低逻辑电平。因此可以透过同步基础禁止生成信号CASSPMASK转变为高逻辑电平来停止同步地产生行地址选通时脉信号CASP。

图13是本发明一实施例的控制方法的流程图。参照图13,于步骤1310,控制电路计数并比较伪静态随机存取存储器的数据输入次数与数据实际写入次数以产生写入匹配信号,并依据计数伪静态随机存取存储器的数据输入次数来产生写入计数时脉信号。接着,于步骤1320,控制电路依据该写入匹配信号与写入计数时脉信号以产生前导信号,并依据前导信号产生行地址选通时脉信号与控制信号,其中控制电路依据该写入匹配信号与该写入计数时脉信号决定是否动态延迟前导信号以延迟或省略伪静态随机存取存储器的行选择线信号的脉冲。

综上所述,本发明的控制电路与控制方法调整前导信号的时序来生成具有适当时序的行选择线信号,以避免伪静态随机存取存储器故障或不稳定操作。本发明通过计数与比较伪静态随机存取存储器的数据输入次数与实际写入次数来产生前导信号,并以决定是否动态延迟前导信号以延迟或省略行选择线信号的脉冲,以避免行选择线信号的脉冲宽度过短,因此可以避免故障或不稳定的操作,并生成必要数量的行选择线信号。通过本发明,伪静态随机存取存储器可实现更高的操作频率,并在制程偏移中具可靠性。

虽然本发明已以实施例揭示如上,然其并非用以限定本发明,任何所属技术领域中技术人员,在不脱离本发明的精神和范围内,当可作些许的更改与润饰,故本发明的保护范围当视权利要求所界定者为准。

- 应用于伪静态随机存取存储器的控制电路及其控制方法

- 用于伪静态随机存取存储器的控制电路以及控制方法