一种基于FPGA+DSP的软件化雷达在线可重构平台及实现方法

文献发布时间:2023-06-19 11:32:36

技术领域

本发明属于雷达技术领域,具体涉及一种软件化雷达在线可重构平台及实现方法。

背景技术

道路交通雷达很早就已经应用在辅助驾驶系统中,而新兴的自动驾驶,雷达也在其中扮演重要角色。目前在自动驾驶领域通过雷达与视频的结合应用,为智能交通的发展贡献了更大的力量。雷达设备的应用与传统的设备相比具有更多的优势,如道闸雷达的安装维护方便、精度高,如车辆检测更准确,无论是停车位还是行车中,都为车主提供了很大的便利。最为重要的是,雷达的实时全天候、高分辨多目标、抗干扰性强、可测速测距、不受恶劣天气影响等特点,是实现智能交通的利器,软件化雷达在线重构技术面向实际需求,智能交通系统紧密契合,让交通系统的智能化、全面化、准确化、实时化的实现具有了更多的可行性。

在军事需求方面,目前雷达种类繁多,不同用途、不同功能的雷达对信号参数(载频、脉宽等)有不同的要求。目前,设计研制的雷达往往无法适应在不同的环境下对不同属性的目标进行智能化跟踪检测的需要。从实战角度出发,现代战争中为了夺取战争初期制空权、打赢电磁战,雷达已成为导弹和各国空军的首批重点战术打击对象。正是由于这个原因,软件化雷达的概念应运而生,软件化雷达(Software Defined Radar)是指由宽带智能天线和射频前端,配上通用的高速DSP/CPU系统构成一种标准接口的探测与跟踪的通用硬件平台,由软件来完成具体功能,具有标准化、模块化和数字化技术特点的新型雷达系统,具有开放式体系架构,可以适应“面向实际需求,以软件技术为核心”的开发理念,以软件化开发模式灵活地实现系统扩展、更新和升级。即通过搭建一个通用的硬件平台,用软件实现各种不同体制雷达的设计,从而缩短研发时间、降低研发成本和开发风险。提高雷达的生存能力是现代雷达研制中不得不考虑的关键指标,而软件化雷达在线可重构技术为现在雷达的研究提供了一种新的思路。通过对核心算法组件的标准化设计,雷达系统的功能可由组件搭建定义,具有服务组件模块化、动态加载应用等优点,软件化雷达在线可重构技术通过下载新程序和发布新参数就可以很容易地改变雷达信号体制,快速响应任务需求。另一方面,使用高性能的数字化器件,采用嵌入式系统的体系结构的是软件化雷达在线重构技术的实现更加快捷便利。

发明内容

为了克服现有技术的不足,本发明提供了一种基于FPGA+DSP的软件化雷达在线可重构平台及实现方法,首先信号处理硬件平台上电运行,引导程序加载主控核程序;上位机进行雷达系统搭建配置,将配置信息发送到主控核;主控核根据配置信息,分配算法组件程序到算法核;DSP通信核接收到数据,按照线程优先级顺序发送数据到算法核进行处理,处理完成后返回给通信核;上位机重构雷达系统,发送在线重构指令,将重构后的配置信息发送到主控核,将原始配置信息覆盖;主控核收到重构指令,重新解析配置信息;根据新的配置信息,重构算法核的配置和优先级,完成重构。本发明可以根据不同的任务需求对雷达系统进行实时动态重构,降低了雷达系统软硬件之间的耦合性,缩短雷达研发周期。

本发明解决其技术问题所采用的技术方案如下:

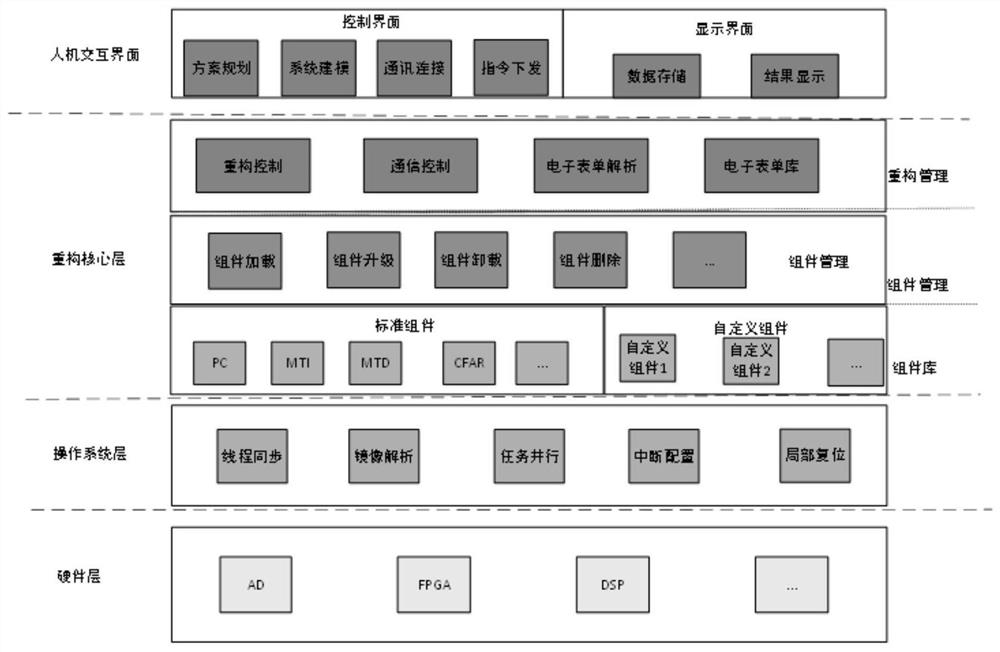

一种基于FPGA+DSP的软件化雷达在线可重构平台,所述在线可重构平台为四层结构,从上向下依次为人机交互模块、重构核心层、操作系统层和硬件层;

所述人机交互模块包括控制界面和显示界面;所述控制界面负责方案规划、系统建模、参数配置和指令下发;所述显示界面负责对雷达信号的处理结果进行保存和显示;

所述重构核心层包括组件库、组件管理和重构管理;所述组件库包含完备的雷达算法组件库,或根据雷达功能需求基于组件标准化模型进行自定义组件研发;

所述操作系统层基于SYS/BIOS实时操作系统,负责动态管理DSP内部的任务、线程、中断以及硬件资源的管理配置;

所述硬件层为软件化雷达硬件处理平台,括AD、FPGA、DSP、前端设备,负责执行计算、存储、通信任务。

优选地,所述雷达算法组件库包括PC、MTI、MTD、CFAR算法组件。

优选地,所述组件库采用XML电子表单对组件的参数进行描述。

一种基于FPGA+DSP的软件化雷达在线可重构实现方法,包括以下步骤:

步骤1:建立软件化雷达组件标准化模型;

步骤2:设计软件化雷达系统方案,根据软件化雷达系统方案搭建硬件处理平台;

步骤3:配置软件化雷达系统方案及参数,分配硬件处理平台DSP各个核的任务;

步骤4:硬件处理平台上电运行,引导程序加载DSP主控核程序;

步骤5:上位机进行软件化雷达系统搭建配置,将配置信息发送到DSP主控核;

步骤6:DSP主控核根据配置信息,分配算法组件到DSP算法核,设置DSP每个算法核任务线程的优先级;

步骤7:通过硬件处理平台前端设备采集雷达信号数据;

步骤8:FPGA接收到雷达信号数据,发送中断通知DSP,数据通信线程开始运行;

步骤9:DSP通信核接收到雷达信号数据后,按照线程优先级顺序发送雷达信号数据到优先级最高的DSP算法核,

步骤10:DSP算法核对接收到的雷达信号数据进行处理,处理完成后返回给DSP通信核,DSP通信核接收到DSP算法核返回的处理数据后,把处理数据发送给次优先级的DSP算法核,以此类推;

步骤11:DSP通信核将所有DSP算法核的处理结果分别保存上传;

步骤12:上位机重构软件化雷达系统,发送在线重构指令,将重构后的配置信息发送到DSP主控核,将原始配置信息覆盖;

步骤13:DSP主控核收到重构指令,重新解析配置信息;根据新的配置信息,加载、卸载或升级算法核,重新分配DSP算法核的任务及任务优先级;

步骤14:重构后的DSP算法核重新运行新的处理程序;完成重构。

本发明的有益效果如下:

1、本发明方法可以根据雷达战场需求进行实时动态重构,保证系统基本运行能力,提高了稳定性;

2、本发明基于算法组件技术对雷达系统进行软硬件解耦,大大提高了可扩展性,降低了升级维护成本。

附图说明

图1为本发明基于FPGA+DSP的软件化雷达在线可重构平台的结构图。

图2为本发明实施例信号处理仿真系统流程图。

图3为本发明实施例的雷达系统方案图。

图4为本发明实施例的系统整体软件设计框图。

图5为本发明实施例的脉冲多普勒雷达仿真处理系统多核工作流程图。

图6为本发明实施例的重构后的脉冲多普勒雷达仿真处理系统多核工作流程图。

具体实施方式

下面结合附图和实施例对本发明进一步说明。

如图1所示,一种基于FPGA+DSP的软件化雷达在线可重构平台,所述在线可重构平台为四层结构,从上向下依次为人机交互模块、重构核心层、操作系统层和硬件层;

所述人机交互模块包括控制界面和显示界面;所述控制界面负责方案规划、系统建模、参数配置和指令下发;所述显示界面负责对雷达信号的处理结果进行保存和显示;

所述重构核心层包括组件库、组件管理和重构管理;所述组件库包含完备的雷达算法组件库,包括PC、MTI、MTD、CFAR等算法组件,或根据雷达功能需求基于组件标准化模型进行自定义组件研发;组件库采用XML电子表单对组件的参数进行描述;

所述操作系统层基于SYS/BIOS实时操作系统,负责动态管理DSP内部的任务、线程、中断以及硬件资源的管理配置;

所述硬件层为软件化雷达硬件处理平台,括AD、FPGA、DSP、前端设备,负责执行计算、存储、通信任务。

一种基于FPGA+DSP的软件化雷达在线可重构实现方法,包括以下步骤:

步骤1:建立软件化雷达组件标准化模型;

步骤2:设计软件化雷达系统方案,根据软件化雷达系统方案搭建硬件处理平台;

步骤3:配置软件化雷达系统方案及参数,分配硬件处理平台DSP各个核的任务;

步骤4:硬件处理平台上电运行,引导程序加载DSP主控核程序;

步骤5:上位机进行软件化雷达系统搭建配置,将配置信息发送到DSP主控核;

步骤6:DSP主控核根据配置信息,分配算法组件到DSP算法核,设置DSP每个算法核任务线程的优先级;

步骤7:通过硬件处理平台前端设备采集雷达信号数据;

步骤8:FPGA接收到雷达信号数据,发送中断通知DSP,数据通信线程开始运行;

步骤9:DSP通信核接收到雷达信号数据后,按照线程优先级顺序发送雷达信号数据到优先级最高的DSP算法核,

步骤10:DSP算法核对接收到的雷达信号数据进行处理,处理完成后返回给DSP通信核,DSP通信核接收到DSP算法核返回的处理数据后,把处理数据发送给次优先级的DSP算法核,以此类推;

步骤11:DSP通信核将所有DSP算法核的处理结果分别保存上传;

步骤12:上位机重构软件化雷达系统,发送在线重构指令,将重构后的配置信息发送到DSP主控核,将原始配置信息覆盖;

步骤13:DSP主控核收到重构指令,重新解析配置信息;根据新的配置信息,加载、卸载或升级算法核,重新分配DSP算法核的任务及任务优先级;

步骤14:重构后的DSP算法核重新运行新的处理程序;完成重构。

具体实施例:

为了验证本发明设计的软件化雷达在线可重构技术方案,使用可视化建模软件搭建脉冲多普勒雷达信号处理仿真系统,该仿真系统由雷达信号处理系统的典型处理模块组成,包含脉冲压缩、动目标检测和恒虚警检测等基本算法组件。信号处理仿真系统流程如图2。图2中输入数据为雷达回波模拟信号,主要包括目标回波、环境杂波、系统噪声以及各种干扰。

根据仿真系统的数据流,在雷达系统图形化开发界面调用算法组件并连接组件接口的输入输出关系,形成雷达系统方案如图3所示。在此页面中搭建脉冲多普勒雷达信号系统,在系统中双击组件,即可弹出参数配置界面。通过对组件参数的修改,即可重构雷达系统,系统重构后下发重构指令到硬件处理平台,硬件处理平台接收到重构指令即可通过重构流程对指定核上运行的组件进行重构。经过修改后的参数生成新的XML描述文件,并且对组件中对原有的参数进行更新。

形成雷达系统后,点击生成按钮,即可生成组件的任务配置参数文件,将配置文件下发到硬件平台的主控核核0进行任务解析,匹配算法组件对应多核的映射关系。将算法组件制作成可执行镜像文件加载到DSP的FLASH中,即可将各个算法组件加载到各个核上分别运行。

多核重构功能划分,多核DSP的优势在于能够多个核并行处理,软件开发人员将应用程序合理地分配能够拥有更高的处理效率。多核软件设计中最关键的是将多个任务明确的划分到不同的核上,基于主从模型将多核的功能划分如下:

1)核0作为主控核,与外部上位机进行交互,根据上位机的指令对其他核进行管理调度。同时核0搭载网络通信任务线程,可以从外部服务器获取系统需要加载的算法镜像。

2)核1作为通信核,负责通过SRIO接收FPGA采集到的数据,并对数据格式进行解析,然后根据主控核的任务规划将数据分发给不同算法核进行处理。并将数据处理结果通过以太网接口发送到显控终端进行结果分析。

3)其余核皆为从核,作为算法核,负责运行特定的算法对数据进行处理,并将接收到的数据处理后发送给通信核。算法核受主控核管理调度,能够在线升级算法核上运行的算法组件。

由于DSP默认上电启动时由核0来完成多核应用程序的加载以及其他核的启动,因此采用核0作为主控核心来负责整个系统的初始化管理。DSP在上电后核0先启动,完成系统硬件的初始化,然后加载核1的镜像启动核1,其他核处于休眠状态,核0根据上位机的命令决定其余数据处理核的启动顺序。系统整体软件设计框图如图4所示。

核1作为通信核启动后首先初始化SRIO硬件,然后运行硬件中断线程监听SRIO门铃包事件,再建立核间通信线程用于与6个算法核进行数据交互。接着,当收到门铃包中断时,表示有外部数据到来,主线程对数据进行解析和分类,将不同的数据分发给对应的算法核去处理。其他从核在启动后建立核间通信线程,并监听通信核的数据,在数据到来后通过特定的算法进行处理。

核0启动后建立外部中断线程,用于监听上位机的控制命令。并建以太网通信线程,在收到在线重构命令后触发网络通信任务,向远程服务器发起连接请求,从核服务器读取所需的软件镜像,然后替换掉对应核上的软件。

由于设备限制,本发明采用上位机生成回波模拟数据,通过以太网接口发送给FPGA,模拟回波信号的采集。FPGA将采集到的回波数据通过SRIO接口发送给DSP进行处理,上位机通过外部硬件中断给DSP发送重构指令以及其他通知信号。在DSP收到外部硬件中断后,通过匹配中断源的ID解析控制命令。DSP将收到的雷达信号处理完成后,将处理结果打包通过以太网接口发送回上位机,上位机调用MATLAB显示处理结果。

主控核核0的调度下,算法核2运行脉冲压缩(PC)算法组件程序;算法核3运行动目标检测(MTD)算法组件程序(采用FFT实现);算法核4运行恒虚警检测程序(采用单元平均恒虚警检测实现,每侧各3个保护单元,8个参考单元),核5~7保留备用。脉冲多普勒雷达仿真处理系统多核工作流程如图5。

1)主控核核0在其软件框架的控制下依次启动核1~4的运行,核5~7仍处于休眠状态;

2)通信核核1运行后,等待FPGA通过SRIO传输模拟回波数据;在接收到雷达信号数据后对雷达信号数据进行解析,去掉格式信息,将数据地址发给算法核2~4;

3)3个算法核分别通过核间通信接收到数据地址,依次对数据进行脉冲压缩、动目标检测和平均单元恒虚警处理,每一个算法核处理完成后将结果地址返还给通信核;

4)通信核核1在每一个算法核处理完成后,都将处理结果通过以太网结果发送到上位机进行保存,以便进行分析比较。

在脉冲多普勒雷达实现的基础上,设计重构方案进行重构技术验证。在原有系统的基础上,核5加载动目标显示算法组件加入系统重构成新的信号处理系统。即重构方案在原有系统运行时,增加动目标显示算法组件,在脉冲压缩算法组件完成对原始数据的处理后,将数据发送给动目标显示算法组件进行处理,在动目标显示算法处理的结果上再依次进行动目标显示和恒虚警检测处理。加入动目标显示模块是为了滤除净值目标杂波,重构方案的多核映射如图6所示。

将重构前后的系统分别载入到硬件平台,根据重构方法步骤进行实例验证,实验结果验证了重构的准确性。

- 一种基于FPGA+DSP的软件化雷达在线可重构平台及实现方法

- 一种基于软件化雷达的快速重构方法