影像二值化方法与电子装置

文献发布时间:2023-06-19 11:35:49

技术领域

本发明是有关于一种二值化方法,且特别是有关于一种影像二值化方法与使用所述方法的电子装置。

背景技术

快速响应矩阵图码(QR code)是目前主流的二维条码,使用者可以用手持装置或专用的条码扫描器透过相机撷取包含QR Code的影像后,以解码出对应的资讯。

一般来说,手持装置或专用的条码扫描器先撷取包含QR Code的影像,再通过分析整张影像而取得最佳的二值化参数。由于现有的算法的二值化操作需要分析整张影像,以取得相应于整个影像的最佳的二值化临界值,进而经由比较所述影像的所有像素各自的亮度值(色彩位值)与所述最佳的二值化临界值以决定所述影像的所有像素的二元值。

因此,手持装置或专用的条码扫描器需要将整张影像预先储存至存储器中。以一张640×680的单色图片为例子,需要至少425(640*680*8/1024/8)KB的储存空间。此大小的主存储器对于手机或高端处理器并不是问题,但多数的微控制器因为有限的存储器(通常为64KB左右),而无法处理QR Code的相关应用/解码。

有鉴于此,本领域的技术人员致力发展另外的方法来使仅具有较小储存空间的存储器的电子装置/处理器可有效率地撷取且处理影像的二值化操作,进而拓展具有较小储存空间的存储器的电子装置/处理器的功能。

“现有技术”段落只是用来帮助了解本发明内容,因此在“现有技术”段落所揭露的内容可能包含一些没有构成所属技术领域中具有通常知识者所知道的现有技术。在“现有技术”段落所揭露的内容,不代表该内容或者本发明一个或多个实施例所要解决的问题,在本发明申请前已被所属技术领域中具有通常知识者所知晓或认知。

发明内容

本发明提供影像二值化方法与电子装置,可在将所述影像转换为较小的二值化影像后,储存所述二值化影像至存储器,以拓展具有较小储存空间的存储器的电子装置/处理器的功能。

本发明的一实施例提供适用于具有小容量的主存储器的电子装置的一种影像二值化方法,其中所述电子装置更包括影像撷取装置与二值化电路。所述方法包括:经由所述影像撷取装置撷取影像,其中所述影像包括为M×N矩阵的多个像素,其中M与N为正整数,其中所述主存储器的大小为Y×M×N位,其中Y为对应所述主存储器的预设正整数;根据一列顺序,经由所述二值化电路从所述影像的M个像素列中尚未被选择的一或多个第一像素列选择排列在最前的目标像素列;经由二值化电路对所述目标像素列执行二值化操作,以获得二值化像素列;经由二值化电路,储存所述二值化像素列至所述主存储器;经由二值化电路,判断所述M个像素列是否皆已被选择;反应于所述M个像素列非皆已被选择,再次执行根据所述列顺序,经由所述二值化电路从所述影像的所述M个像素列中尚未被选择的所述一或多个第一像素列选择排列在最前的所述目标像素列的步骤;反应于所述M个像素列皆已被选择,完成对所述影像的二值化操作。

本发明的又一实施例提供一种电子装置,包括一影像撷取装置;一主存储器;以及一二值化电路。所述二值化电路电连接至所述影像撷取装置与所述主存储器。所述影像撷取装置用以撷取影像,其中所述影像包括为M×N矩阵的多个像素,其中M与N为正整数,其中所述主存储器的大小为Y×M×N位,其中Y为对应所述主存储器的预设正整数。此外,所述二值化电路用以根据一列顺序从所述影像的M个像素列中尚未被选择的一或多个第一像素列选择排列在最前的目标像素列,其中所述二值化电路更用以对所述目标像素列执行二值化操作,以获得二值化像素列,并且储存所述二值化像素列至所述主存储器。所述二值化电路更用以判断所述M个像素列是否皆已被选择,其中反应于所述M个像素列非皆已被选择,所述二值化电路更用以再次执行根据所述列顺序,经由所述二值化电路从所述影像的所述M个像素列中尚未被选择的所述一或多个第一像素列选择排列在最前的所述目标像素列的步骤,其中反应于所述M个像素列皆已被选择,所述二值化电路更用以完成对所述影像的二值化操作。

基于上述,本发明的多个实施例所提供影像二值化方法与电子装置,可仅具有较小储存空间的存储器的电子装置/处理器/微控制器可有效率地撷取且处理影像的二值化操作,以将所述影像转换为较小的二值化影像,以使转换后的二值化影像可被储存至较小储存空间的所述存储器并且可被进一步地解码,进而可拓展具有较小储存空间的存储器的电子装置/处理器的功能。如此一来,具有较小的存储器的电子装置/处理器/微控制器也可服务于二维条码(或其他影像处理)的应用领域,进而增强了电子装置/处理器/微控制器的工作效率与节省了原本用以添购具有较大的存储器的电子装置/处理器/微控制器的成本。

为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附图式作详细说明如下。

附图说明

图1是根据本发明的一实施例所绘示的电子装置的方块示意图;

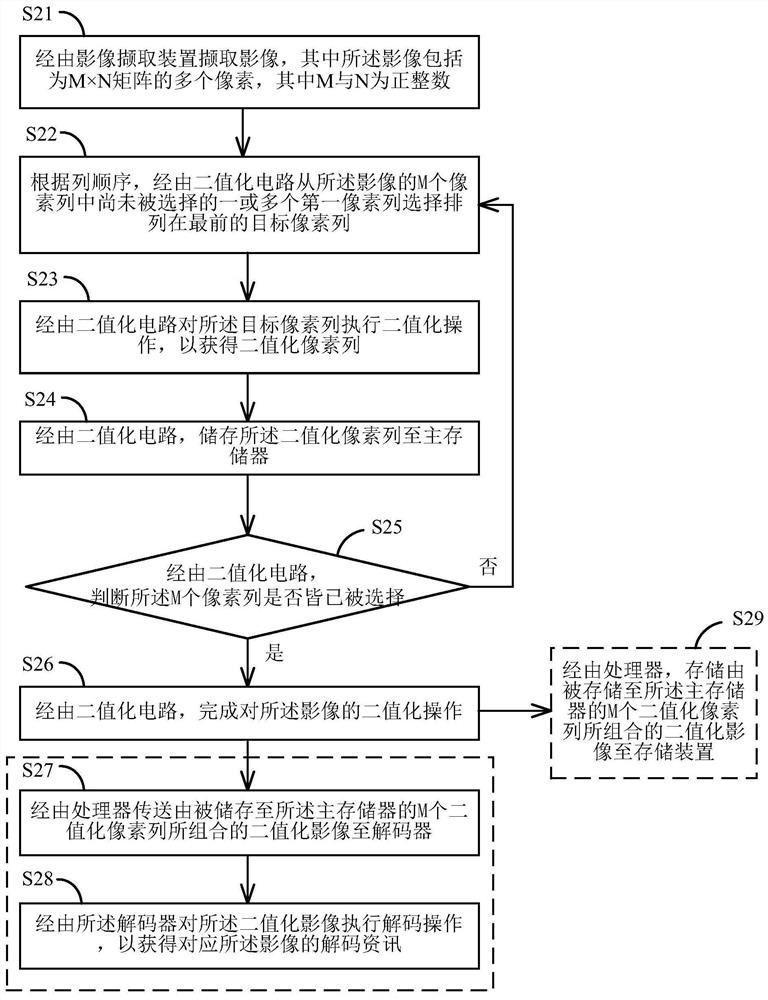

图2是根据本发明的一实施例所绘示的影像二值化方法的流程图;

图3是根据本发明的一实施例所绘示的对所述目标像素列所执行的二值化操作的流程图;

图4是根据本发明的一实施例所绘示的异色判断操作的流程图;

图5是根据本发明的一实施例所绘示的累积偏离判断操作的流程图;

图6是根据本发明的一实施例所绘示的转换所述目标像素列为二值化像素列的示意图;

图7是根据本发明的一实施例所绘示的影像与对应的二值化影像的对照图。

10:电子装置;

20:媒体内容;

110:处理器;

120:储存装置;

130:解码器;

140:影像撷取装置;

150:二值化电路;

160:主存储器;

S21、S22、S23、S24、S25、S26、S27、S28、S29:影像二值化方法的流程步骤;

S31、S32、S33、S34、S35、S36、S37、S38、S39、S40、S41:目标像素列的二值化操作的流程步骤;

S42、S43:二值化操作中的异色判断操作的流程步骤;

S51、S52:二值化操作中的累积偏离判断操作的流程步骤;

A~F:节点;

P(i)、P(1)~P(18):像素;

600:表;

具体实施方式

图1是根据本发明的一实施例所绘示的电子装置的方块示意图。请参照图1,在本实施例中,所述电子装置10包括处理器110、储存单元120、解码器330、影像撷取装置140、二值化电路150以及主存储器160。在本实施例中,所述电子装置10用以经由所述影像撷取装置140对媒体内容20进行影像撷取,以最终获得对应于所撷取影像所包含的媒体内容的资讯。所述媒体内容20例如是一维条码、二维条码或其他适合的编码影像。所述媒体内容可被印刷于各种材质的表面上或经由显示装置而显示。

在本实施例中,处理器110为具备运算能力的硬件。处理器110用以执行一或多个程式码,以管理电子装置10的整体运作。在本实施例中,处理器110例如是一核心或多核心的中央处理单元(Central Processing Unit,CPU)、可编程的微处理器(微处理器(Micro-processor))、数字信号处理器(Digital Signal Processor,DSP)、可编程的控制器、特殊应用集成电路(Application Specific Integrated Circuits,ASIC)、可编程的逻辑装置(Programmable Logic Device,PLD)、微控制器或其他类似装置。

储存装置120用以经由处理器110的指示来记录一些需要长时间储存的资料。例如,储存装置120记录用以管理电子装置10的固件或是软件。储存装置120可以是任何型态的配置有非挥发性存储器模组(如,NAND型快闪存储器模组)的储存电路模组。在一实施例中,储存装置120例如是具有存储卡插槽的储存电路模组,并且可存取储存在存储卡插槽中的存储卡中的资料。

解码器130用以对二值化影像或所撷取的影像进行解码操作,以获得包含于所述影像的解码资讯(例如,相应于所述媒体内容的解码资讯)。在一实施例中,所述解码器130可整合至所述处理器110中。在一实施例中,解码器130可经由软体的方式来实现为具有所述解码器130的功能的解码应用程序,并且述处理器110可执行所述解码应用程序,以执行进行所述解码操作。

影像撷取装置140包括一镜头与影像感测元件,其中影像感测元件可例如是一感光耦合元件(Charge-Coupled Device,CCD)或一互补式金属氧化物半导体(CMOS)影像感测器。所述影像撷取装置140例如是单镜头或多镜头的相机。所述影像撷取装置140用以对所述媒体内容20进行拍照或摄影,以撷取相应于媒体内容的影像或视讯。所撷取的所述影像包括为M×N矩阵的多个像素,其中M与N为正整数。每个像素具有位值(亦称,亮度值、灰阶值或色彩值)。每个像素的位值的大小可大于1个位。例如,假设每个像素的位值为8个位大小的亮度值,则所述亮度值的范围可为0(纯黑色)至255(纯白色)。

二值化电路150电连接至所述影像撷取装置140,用以对所撷取的所述影像执行二值化操作,以获得二值化影像。应注意的是,在本实施例中,经由所述影像撷取装置140所撷取的所述影像在未被暂存/储存至主存储器160之前,所述二值化电路150便会对所述影像执行二值化操作。在获得二值化影像后,所述二值化电路150更用以将所述二值化影像储存至主存储器160中。应注意的是,在一实施例中,所述二值化电路150亦可整合至影像撷取装置140中,以让整合后的影像撷取装置140可反应于所撷取的影像,直接输出对应的二值化影像。如此一来,可在一些仅需要二值化影像的应用中,大量节省用以储存影像的存储器空间。值得一提的是,本发明并不限定于利用影像撷取装置140来获得欲执行二值化操作的影像。例如,在其他实施例中,电子装置可具有连接介面电路单元(如,UART,I2C,SPI,USB等)并且欲执行二值化操作的影像可经由所述连接介面电路单元其他电子装置所接收。又例如,执行二值化操作的影像可从储存装置120来获取。又例如,电子装置10可具有通讯电路单元(如,Wifi,Bluetooth电路模组等),并且执行二值化操作的影像可经由通讯电路单元所接收。

在本实施例中,主存储器160用以暂存资料。主存储器160例如是动态随机存取存储器或静态随机存取存储器。此外,所述主存储器160的大小为Y×M×N位,其中Y为对应所述主存储器的预设正整数。所述主存储器的所述大小被预先设定于小于128千位组(KB)。在本实施例中,Y的具体数值可根据主存储器160的规格大小而决定,所述M与N是欲执行所述二值化操作的影像的规格而决定(如,所述影像包括为M×N矩阵的多个像素)。应注意的是,在一实施例中,电子装置10并不具备主存储器160,但处理器110本身具有空间小的一个存储器(如,此存储器的储存空间小于100KB),用以暂存指令或资料。在此实施例中,此整合至处理器110中的存储器可提供主存储器160的功能。

图2是根据本发明的一实施例所绘示的影像二值化方法的流程图。请参照图2,在步骤S21中,经由影像撷取装置140撷取影像,其中所述影像包括为M×N矩阵的多个像素,其中M与N为正整数。

接着,在步骤S22中,根据列顺序,经由二值化电路150从所述影像的M个像素列中尚未被选择的多个第一像素列选择排列在最前的目标像素列。接着,在步骤S23中,经由二值化电路150对所述目标像素列执行二值化操作,以获得二值化像素列。具体来说,二值化电路150可从排列在最前方的像素列(如,第1个像素列)或排列在最后方的像素列(如,第M个像素列)开始来选择用以执行二值化操作的目标像素列。

更详细来说,对目标像素列所执行的二值化操作包括:根据一初始像素门槛值判断所述目标像素列的N个像素中的第1个像素的位值为二元值(Binary value)中的第一数值(如,1)或第二数值(如,0),其中初始像素门槛值为预设值或对应排列在所述目标像素列之前的像素列的亮度平均值。当所述目标像素列为第1个像素列时,所述初始像素门槛值为预设值。所述预设值被设定为每个像素的位值的大小范围的中间值。例如,假设每个像素的位值为8个位大小,所述预设值可被设定为128(即,2

接着,针对所述目标像素列的N个像素中的所述第2至第N个像素中的尚未被选择的一或多个第一像素,选择在所述一或多个第一像素中排列在最前方的一目标像素来执行对应所述目标像素的二元值判断操作。

在本实施例中,所述二元值判断操作包括:根据所述目标像素的位值与对应排列在所述目标像素之前的一比较像素的位值来计算所述目标像素与所述比较像素之间的绝对差值为对应所述目标像素的一像素绝对差值,其中对应所述第1个像素的所述像素绝对差值预设为0;根据比较对应所述目标像素的所述像素绝对差值与对应所述比较像素的所述动态门槛值来判断所述目标像素是否与所述比较像素同色。

反应于判定所述目标像素与所述比较像素同色,设定所述目标像素的所述位值相等于所述比较像素的二元值,辨识连续排列于所述目标像素之前的一或多个同色像素,根据对应所述一或多个同色像素的与所述目标像素的所述多个像素绝对差值来计算平均值为对应所述目标像素的所述像素绝对差值平均,根据对应所述目标像素的所述像素绝对差值平均来计算对应所述目标像素的所述动态门槛值,其中对应所述第1个像素的所述像素绝对差值平均为预设像素绝对差值平均(如,10),并且对应所述第1个像素的所述动态门槛值是根据对应所述第1个像素的所述像素绝对差值平均所计算的。

此外,反应于判定所述目标像素与所述比较像素非同色,设定所述目标像素的所述位值不相等于所述比较像素的所述二元值,将对应所述目标像素的所述像素绝对差值平均设定为所述预设像素绝对差值平均。

接着,判断所述目标像素是否为所述目标像素列的最后一个像素。反应于所述目标像素为所述目标像素列的所述最后一个像素,完成对所述目标像素列所执行的所述二值化操作;反应于所述目标像素不为所述目标像素列的所述最后一个像素,选择排列在所述目标像素后的另一第一像素作为新的所述目标像素,以执行对应所述新的目标像素的所述二元值判断操作。

更详细来说,在本实施例中,上述根据对应所述目标像素的所述像素绝对差值平均来计算对应所述目标像素的所述动态门槛值的步骤包括:将对应所述目标像素的所述像素绝对差值平均乘以第一参数且再加上第二参数所获得的总和作为对应所述目标像素的所述动态门槛值,其中所述第一参数与第二参数皆为正整数。应注意的是,所述第一参数可被预设为3、所述第二参数可被预设为5,但本发明不限于此。第一参数与第二参数可依据需求而设定成其他正整数。

此外,所述第一参数与所述第二参数更可动态地根据所述像素绝对差值平均来调整。也就是说,本发明的动态门槛值的设定原理为:(1)相同颜色若数值分布均匀(即,光干扰较少),所获得的像素绝对差值平均会逐渐缩小,导致动态门槛值会逐渐缩小。因此颜色数值变化时(如,像素绝对差值大于动态门槛值时),会被判定为需要变色;(2)相同颜色若数值分布不均匀(即,光干扰较大),所获得的像素绝对差值平均会逐渐增加,导致动态门槛值会逐渐增加。因此颜色数值需要有更大的变化时(如,像素绝对差值需大于较大的动态门槛值时),才会被判定为需要变色。如此一来,基于像素绝对差值平均的动态门槛值的设定方式可具有抗光干扰的效用。

另一方面,在其他实施例中,对应所述目标像素的所述动态门槛值也可被直接设定为一个参数,此参数会依据目标像素与比较像素之间的像素绝对差值而有不同。所述像素绝对差值越大,所述动态门槛值会被设定成越大的所述参数,反之亦然。

以下更藉由图3来说明对所述目标像素列所执行的二值化操作的详细流程。

图3是根据本发明的一实施例所绘示的对所述目标像素列所执行的二值化操作的流程图。具体来说,二值化电路150会从所述目标像素列的第1个像素开始执行二元值判断操作。步骤S31~S34主要针对的是对所述目标像素列的第1个像素的二元值判断操作。步骤S35~S40主要针对的是所述目标像素列的第2~第N个像素的二元值判断操作。请参照图3,在步骤S31中,二值化电路150选择目标像素列的N个像素中的第i个像素为目标像素,其中i的初始值为1,并且为小于或等于N的正整数。

接着,在步骤S32中,二值化电路150判断所述目标像素的位值是否大于初始像素门槛值。如上述,所述初始像素门槛值为预设值或对应排列在所述目标像素列之前的像素列的亮度平均值。例如,假设所述目标像素列为所述影像的第2个像素列,二值化电路150会计算所述影像的第1个像素列的所有像素的位值的平均,以作为对应所述目标像素列的初始像素门槛值。

反应于判定所述目标像素的位值大于初始像素门槛值,执行步骤S33;反应于判定所述目标像素的位值非大于初始像素门槛值,执行步骤S34。

在步骤S33中,二值化电路150将所述目标像素的所述位值设定为二元值中的第一数值(如,1)。在步骤S34中,二值化电路150将所述目标像素的所述位值设定为二元值中的第二数值(如,0)。

接着,在步骤S35中,反应于i小于N,二值化电路150将i加上1。接着,在步骤S36中,二值化电路150选择所述目标像素列的所述N个像素中的第i个像素为所述目标像素,计算所述目标像素与第i-1个像素之间的像素绝对差值,以及计算对应所述目标像素的像素绝对差值平均与动态门槛值。

具体来说,二值化电路150会判断所述目标像素是否为所述目标像素列的最后一个像素(当i等于N)。若所述目标像素不为所述目标像素列的最后一个像素(i小于N),二值化电路150会选择下一个像素(将i加上1)以作为新的目标像素(S35)。

在本实施例中,二值化电路150会计算所述目标像素的位值与排列在所述目标像素(第i个像素)之前的像素(即,第i-1个像素;亦称,比较像素)的位值之间的绝对差值(亦称,像素绝对差值)。举例来说,假设目标像素的位值为150,并且比较像素的位值为160。所述目标像素与所述比较像素之间的像素绝对差值为10(|150-160|=10)。所述像素绝对差值对应所述目标像素。

接着,在步骤S37中,二值化电路150判断所述像素绝对差值是否大于对应所述第i-1个像素的动态门槛值。具体来说,在本实施例中,二值化电路150藉由比较对应目标像素的所述像素绝对差值与对应所述比较像素的所述动态门槛值来判断所述目标像素是否与所述比较像素同色。换句话说,若所述目标像素与前一个像素(即,比较像素)的差异太大(如,大于所述动态门槛值),二值化电路150会判定所述目标像素的颜色不同于所述比较像素。

反应于判定所述像素绝对差值不大于对应所述第i-1个像素的所述动态门槛值(即,二值化电路150判定所述目标像素与所述比较像素同色),二值化电路150执行步骤S38;反应于判定所述像素绝对差值大于对应所述第i-1个像素的所述动态门槛值(即,二值化电路150判定所述目标像素与所述比较像素不同色),二值化电路150执行步骤S40。

在步骤S38中,二值化电路150将所述目标像素的所述位值设定为相等于所述第i-1个像素的位值的二元值。即,二值化电路150将所述目标像素设定为所述比较像素的颜色。

接着,在步骤S39中,二值化电路150计算对应所述目标像素的像素绝对差值平均与动态门槛值。计算对应所述目标像素的像素绝对差值平均与动态门槛值的方式已经说明如上,不赘述于此。接着,流程接续至步骤S35。

另一方面,在步骤S40中,二值化电路150将所述目标像素的所述位值设定为不相等于所述第i-1个像素的位值的二元值。即,二值化电路150将所述目标像素设定为不相同于所述比较像素的另一颜色。

接着,在步骤S41中,二值化电路150初始化对应所述目标像素的像素绝对差值平均与动态门槛值。具体来说,由于所述目标像素改变了颜色,二值化电路150将对应所述目标像素的像素绝对差值平均设定为预设像素绝对差值平均,并且根据所述预设像素绝对差值平均计算对应所述目标像素的动态门槛值。接着,流程接续至步骤S35。

值得一提的是,在一实施例中,反应于判定所述目标像素与所述比较像素不同色,在执行步骤S40之前,二值化电路150会先执行异色判断操作(经由节点A)。

图4是根据本发明的一实施例所绘示的异色判断操作的流程图。请参照图4,在步骤S42中,二值化电路150计算排列于所述目标像素后的Q个异色判断像素与第i-1个像素之间的Q像素绝对差值。所述Q为正整数,亦称,异色判断长度(如,3)。

接着,在步骤S43中,二值化电路150判断所述Q个像素绝对差值是否皆大于对应所述第i-1个像素的动态门槛值。

反应于判定所述Q个像素绝对差值非皆大于对应所述第i-1个像素的动态门槛值,二值化电路150判定所述目标像素为被干扰像素。即,二值化电路150判定所述目标像素与所述比较像素为不同色的判断结果是被干扰后的结果,是无效的(不正确的)。因此,二值化电路150会接续执行步骤S38(经由节点B)。

此外,反应于判定所述Q个像素绝对差值皆大于对应所述第i-1个像素的动态门槛值,二值化电路150判定所述目标像素与所述比较像素为同色的判断结果是有效的(正确的)。因此,二值化电路150会接续执行步骤S40(经由节点C)。

具体来说,因为二维条码的设计原理不会让一个像素列中的一个像素的颜色相异于相邻的多个像素的颜色。在判定所述目标像素需要改变颜色时,二值化电路150会先判断在所述目标像素后的Q个异色判断像素与所述比较像素之间的绝对差值是否皆大于对应所述比较像素的所述动态门槛值。即,二值化电路150会预先判断需要变色的所述目标像素之后的Q个异色判断像素是否也需设定为所述目标像素的颜色/二元值。若所述Q个异色判断像素的颜色/二元值与所述目标像素相同,则二值化电路150会判断所述目标像素应变色,并且二值化电路150也会直接设定所述Q个异色判断像素的二元值为所述目标像素的二元值。

值得一提的是,在一实施例中,反应于判定所述目标像素与所述比较像素同色,在执行步骤S38之前,二值化电路150会先执行累积偏离判断操作(经由节点D)。

图5是根据本发明的一实施例所绘示的累积偏离判断操作的流程图。请参照图5,在步骤S51中,二值化电路150将所述目标像素列的所述位值减所述第i-1个像素的所述位值所获得的差值加入至当前的累积偏离值,以更新累积偏离值。在步骤S52中,二值化电路150判断所述更新后的累积偏离值小于第一偏离门槛值或大于第二偏离门槛值。所述第一偏离门槛值例如是-100;所述第二偏离门槛值例如是+100,但本发明不限于此,所述第一偏离门槛值与所述第二偏离门槛值可根据需求而被预先设定。

反应于判定所述更新后的累积偏离值小于所述第一偏离门槛值,二值化电路150将所述目标像素的所述位值设定为所述二元值中的所述第一数值。即,执行步骤S33(经由节点E)。

另一方面,反应于判定所述更新后的累积偏离值大于所述第二偏离门槛值,二值化电路150将所述目标像素的所述位值设定为所述二元值中的所述第二数值。即,执行步骤S34(经由节点F)。值得一提的是,所述累积偏离值的功能是为了校正在累积性的多个小于动态门槛值的像素皆被判定不变色,但实际上所述多个像素的位值已经越来越接近纯黑色或纯白色的情境发生所导致的二元值的判定错误。

接着,在执行所述累积偏离判断操作以决定是否直接设定所述目标像素为所述第一数值或所述第二数值后,二值化电路150会根据设定后的所述目标像素的二元值是否与所述比较像素的二元值相同来判断执行步骤S39或步骤S41。

例如,在本实施例中,反应于所述目标像素的所述二元值不相等于所述比较像素的所述二元值,所述二值化电路150重置所述累积偏离值为所述初始值,设定对应所述目标像素的所述像素绝对差值平均为所述预设像素绝对差值平均,并且根据所述预设像素绝对差值平均来计算对应所述目标像素的所述动态门槛值(S41)。所述初始值例如为0。

此外,反应于所述目标像素的所述二元值相等于所述比较像素的所述二元值,所述二值化电路150计算对应所述目标像素的所述像素绝对差值平均,并且根据对应所述目标像素的所述像素绝对差值平均来计算对应所述目标像素的所述动态门槛值(S39)。

图6是根据本发明的一实施例所绘示的转换所述目标像素列为二值化像素列的示意图。请参照图6,举例来说,假设目标像素列具有18个像素(N=18)P(1)~P(18)。对应所述像素P(1)~P(18)的位值如表600所示。

首先,i等于1(第一个像素),针对像素P(1):二元值电路150设定对应像素P(1)的像素绝对差值为“0”;设定对应像素P(1)的像素绝对差值平均为预设像素绝对差值平均(即,10);计算对应像素P(1)的动态门槛值为“35”;设定对应像素P(1)的累积偏离值为“0”;根据像素P(1)的位值与初始像素门槛值判定所述像素P(1)的二元值为“0”。

接着,针对像素P(2):二元值电路150根据像素P(2)的位值“10”与像素P(1)的位值“13”来计算像素P(2)与像素P(1)之间的像素绝对差值为“3”与累积偏离值为“-3”(即,-3+0=-3);由于判定对应像素P(2)的像素绝对差值“3”小于对应像素P(1)的动态门槛值“35”,判定像素P(2)与像素P(1)同色,并且设定像素P(2)的二元值为“0”;计算对应像素P(2)的像素绝对差值平均为“6.5”(即,(10+3)/2=6.5)与计算对应像素P(2)的动态门槛值为“24.5”(即,6.5*3+5=24.5)。

接着,针对像素P(3):二元值电路150根据像素P(3)的位值“17”与像素P(2)的位值“10”来计算像素P(3)与像素P(2)之间的像素绝对差值为“7”与累积偏离值为“+4”(即,-3+7=+4);由于判定对应像素P(3)的像素绝对差值“7”小于对应像素P(2)的动态门槛值“24.5”,判定像素P(3)与像素P(2)同色,并且设定像素P(3)的二元值为“0”;计算对应像素P(3)的像素绝对差值平均为“6.67”(即,(10+3+7)/3=6.67)与计算对应像素P(3)的动态门槛值为“25”。

接着,针对像素P(4):二元值电路150根据像素P(4)的位值“33”与像素P(3)的位值“17”来计算像素P(4)与像素P(3)之间的像素绝对差值为“16”与累积偏离值为“+20”(即,+16+4=+20);由于判定对应像素P(4)的像素绝对差值“16”小于对应像素P(3)的动态门槛值“25”,判定像素P(4)与像素P(3)同色,并且设定像素P(4)的二元值为“0”;计算对应像素P(4)的像素绝对差值平均为“9”(即,(10+3+7+16)/4=9)与计算对应像素P(4)的动态门槛值为“32”。

接着,针对像素P(5):二元值电路150根据像素P(5)的位值“181”与像素P(4)的位值“33”来计算像素P(5)与像素P(4)之间的像素绝对差值为“148”与累积偏离值为“+168”(即,+148+20=+168);由于判定对应像素P(5)的像素绝对差值“148”大于对应像素P(4)的动态门槛值“32”,判定像素P(5)与像素P(4)不同色;进行异色判断操作(异色判断长度为3),判定像素P(6)-P(7)各自与像素P(4)之间的像素绝对差值(如,160、149、157)皆大于对应像素P(4)的动态门槛值“32”,并且确认像素P(5)与像素P(4)不同色且设定像素P(5)~P(8)的二元值设定为“1”;重置对应像素P(5)的像素绝对差值平均为“10”、重置对应像素P(5)的累积偏离值为“0”与计算对应像素P(5)的动态门槛值为“35”。

接着,针对像素P(6):二元值电路150根据像素P(6)的位值“193”与像素P(5)的位值“181”来计算像素P(6)与像素P(5)之间的像素绝对差值为“12”与累积偏离值为“+12”(即,+12+0=+12);计算对应像素P(6)的像素绝对差值平均为“11”(即,(10+12)/2=11)与计算对应像素P(6)的动态门槛值为“38”(像素P(6)的二元值已经被设定为“1”)。针对像素P(7)、P(8)的过程相似于像素P(6),不赘述于此。

接着,针对像素P(9):二元值电路150根据像素P(9)的位值“191”与像素P(8)的位值“190”来计算像素P(9)与像素P(8)之间的像素绝对差值为“1”与累积偏离值为“+12”;由于判定对应像素P(9)的像素绝对差值“1”小于对应像素P(8)的动态门槛值“34.25”,判定像素P(9)与像素P(8)同色,并且设定像素P(9)的二元值为“1”;计算对应像素P(9)的像素绝对差值平均为“8”与计算对应像素P(9)的动态门槛值为“29”。

接着,针对像素P(10):二元值电路150根据像素P(10)的位值“189”与像素P(9)的位值“191”来计算像素P(10)与像素P(9)之间的像素绝对差值为“2”与累积偏离值为“+10”;由于判定对应像素P(10)的像素绝对差值“2”小于对应像素P(8)的动态门槛值“29”,判定像素P(10)与像素P(9)同色,并且设定像素P(10)的二元值为“1”;计算对应像素P(10)的像素绝对差值平均为“7”与计算对应像素P(9)的动态门槛值为“26”。

接着,针对像素P(11):二元值电路150根据像素P(11)的位值“158”与像素P(10)的位值“189”来计算像素P(11)与像素P(10)之间的像素绝对差值为“31”与累积偏离值为“-22”;由于判定对应像素P(11)的像素绝对差值“31”大于对应像素P(10)的动态门槛值“26”,判定像素P(11)与像素P(10)不同色;进行异色判断操作,判定像素P(12)~P(14)各自与像素P(4)之间的像素绝对差值(如,10、9、25)非皆大于对应像素P(10)的动态门槛值“26”,并且确认像素P(11)为被干扰像素,并且确认像素P(11)与像素P(10)为同色;设定像素P(11)的二元值设定为“1”;计算对应像素P(11)的像素绝对差值平均为“11.75”与计算对应像素P(11)的动态门槛值为“32.375”。针对像素P(12)~P(16)的过程相似于像素P(10),不赘述于此。

值得一提的是,经由上述的异色判断操作,可判断出像素P(11)为被干扰像素,而避免了错误的变色判断(改变二元值的判断)。

接着,针对像素P(17):二元值电路150根据像素P(17)的位值“78”与像素P(16)的位值“110”来计算像素P(17)与像素P(16)之间的像素绝对差值为“32”与累积偏离值为“-102”;由于判定对应像素P(17)的像素绝对差值“32”不大于对应像素P(16)的动态门槛值“46.25”,判定像素P(17)与像素P(16)同色,设定像素P(17)的二元值为“1”。

如上所述,判定对应像素P(17)的像素绝对差值“32”不大于对应像素P(16)的动态门槛值“46.25”时,可进行累积偏离判断操作。此时,反应于判定累积偏离值小于第一偏离门槛值(-100),设定像素P(17)的二元值为“0”;重置对应像素P(17)的像素绝对差值平均为“10”、重置对应像素P(17)的累积偏离值为“0”与计算对应像素P(17)的动态门槛值为“35”。也就是说,在此例子中,虽然对应多个像素的多个像素绝对差值皆不会导致变色,但由于像素所累积的偏离已经低于一定程度(如,低于第一偏离门槛值),二值化电路150直接将像素设定为二元值中的第一数值(如,0,(黑色))。如此一来,可避免累积性的像素之间的差值导致变色判断的错误。

接着,针对像素P(18):二元值电路150根据像素P(18)的位值“60”与像素P(17)的位值“78”来计算像素P(18)与像素P(17)之间的像素绝对差值为“18”与累积偏离值为“-18”;由于判定对应像素P(18)的像素绝对差值“18”小于对应像素P(17)的动态门槛值“35”,判定像素P(18)与像素P(17)同色,并且设定像素P(18)的二元值为“0”;计算对应像素P(18)的像素绝对差值平均为“14”与计算对应像素P(18)的动态门槛值为“47”。

完成对目标像素列所执行的二值化操作后,二值化电路150可将位值已经皆被设定为二元值的目标像素列的所有像素视为一个二值化像素列。即,目标像素列会被转换为二值化像素列。请再回到图2,接着,在步骤S25中,经由二值化电路150,判断所述M个像素列是否皆已被选择。反应于判定所述M个像素列皆已被选择(即,获得M个二值化像素列),执行步骤S26;反应于判定所述M个像素列皆已被选择(即,尚有未被选择的一或多个像素列需要被执行二值化操作),执行步骤S22。

在步骤S26中,经由二值化电路150,完成对所述影像的二值化操作。具体来说,此时,二值化电路150已经将M个像素列二值化为M个二值化像素列,并且二值化电路150会判定整个影像的二值化操作已经完成。

接着,在步骤S27中,经由处理器110传送由被储存至所述主存储器的M个二值化像素列所组合的二值化影像至解码器130。在步骤S28中,经由所述解码器130对所述二值化影像执行解码操作,以获得对应所述影像的解码资讯。

具体来说,处理器110会将所述M个二值化像素列组合为对应所述影像的二值化影像,并且将所述二值化影像传送至解码器130,以尝试获得所述影像所包含的资讯(亦称,解码资讯)。例如,获得所述影像的QR Code所包含的文字资讯。所述解码器130解码所述二值化影像的解码操作并非本发明的主要技术特征,细节不赘述于此。

应注意的是,在一实施例中,步骤S27、S28并不会被执行,但步骤S26接续至步骤S29。在步骤S29中,经由处理器110,储存由被储存至所述主存储器160的M个二值化像素列所组合的二值化影像至储存装置120。具体来说,处理器110会进一步将所组合成的二值化影像储存至储存装置120,以利之后对所述二值化影像的相关应用。所述相关应用包括但不限于上述的解码操作。

图7是根据本发明的一实施例所绘示的影像与对应的二值化影像的对照图。请参照图7,本发明的多个实施例所提供的影像二值化方法与电子装置,可在所撷取的影像被光照干扰的情况下(如,图7所示的左方QR Code),利用局部的像素绝对差值与对应的动态门槛值的比对结果,依然可正确地获得对应的二值化影像(如,图7所示的右方QR Code)。相较于传统方法,传统方法可能会因为所撷取的影像被光照干扰的情况下(如,图7所示的左方QR Code)计算出过高的二值化临界值,进而导致后续所获得的二值化影像失真,以及对应的解码操作的失败。

此外,本发明的实施例所提供的二值化影像的大小也会在二值化后被大量减少。例如,如上述,传统上以一张640×680的单色图片为例子,需要至少425KB的储存空间。但,经由本发明的实施例所获得的640×680的二值化影像的大小可缩减成53.125KB,所述二值化影像恰好可被储存至一般市面上的微控制器的存储器中(通常为64KB左右)。如此一来,经由实施本发明的实施利所提供的影像二值化方法,市面上的微控制器便有能力来执行相应于二元值影像的影像解码操作或相关应用(如,二维条码的解码操作),增强了微控制器的功能,进而可减少添置大容量存储器的硬体成本。

综上所述,本发明的多个实施例所提供影像二值化方法与电子装置,可仅具有较小储存空间的存储器的电子装置/处理器/微控制器可有效率地撷取且处理影像的二值化操作,以将所述影像转换为较小的二值化影像,以使转换后的二值化影像可被储存至较小储存空间的所述存储器并且可被进一步地解码,进而可拓展具有较小储存空间的存储器的电子装置/处理器的功能。如此一来,具有较小的存储器的电子装置/处理器/微控制器也可服务于二维条码(或其他影像处理)的应用领域,进而增强了电子装置/处理器/微控制器的工作效率与节省了原本用以添购具有较大的存储器的电子装置/处理器/微控制器的成本。

虽然本发明已以实施例揭露如上,然其并非用以限定本发明,任何所属技术领域中具有通常知识者,在不脱离本发明的精神和范围内,当可作些许的更动与润饰,故本发明的保护范围当视后附的申请专利范围所界定者为准。

- 影像二值化方法与电子装置

- 基于矩阵二值化的遥感影像去除彩线和残缺影像拼接方法