双电压阈电路及其掉电防护电路

文献发布时间:2023-06-19 11:49:09

【技术领域】

本发明涉及电路设计技术领域,特别涉及一种双电压阈电路及其掉电防护电路。

【背景技术】

请参考图1所示,其为现有技术中的一种多电压阈电路的电路示意图,该电路中有两个及以上的电压阈,其中,高压电路110的电源端与高电压源VDD

因此,有必要提出一种改进的技术方案来克服上述问题。

【发明内容】

本发明的目的之一在于提供一种双电压阈电路及其掉电防护电路,其可以在低压电路掉电时保护高压电路。

根据本发明的一个方面,本发明提供一种双电压阈电路的掉电防护电路,其包括:高阈值复位电路,其输入端与低电压源VDD

根据本发明的另一个方面,本发明提供一种双电压阈电路,其包括:高压电路;低压电路;掉电防护电路。所述掉电防护电路包括:高阈值复位电路,其输入端与低电压源VDD

与现有技术相比,本发明通过对高压和低压域设计不同阈值电压的复位电路,从而控制不同电压域的掉电复位顺序,来确保电路不会因为掉电顺序不确定而造成损坏或异常,进而在低压电路掉电时保护高压电路。。

【附图说明】

为了更清楚地说明本发明实施例的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其它的附图。其中:

图1为现有技术中的一种多电压阈电路的电路示意图;

图2为本发明在一个实施例中的双电压阈电路的电路示意图。

【具体实施方式】

为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合附图和具体实施方式对本发明作进一步详细的说明。

此处所称的“一个实施例”或“实施例”是指可包含于本发明至少一个实现方式中的特定特征、结构或特性。在本说明书中不同地方出现的“在一个实施例中”并非均指同一个实施例,也不是单独的或选择性的与其他实施例互相排斥的实施例。除非特别说明,本文中的连接、相连、相接的表示电性连接的词均表示直接或间接电性相连。

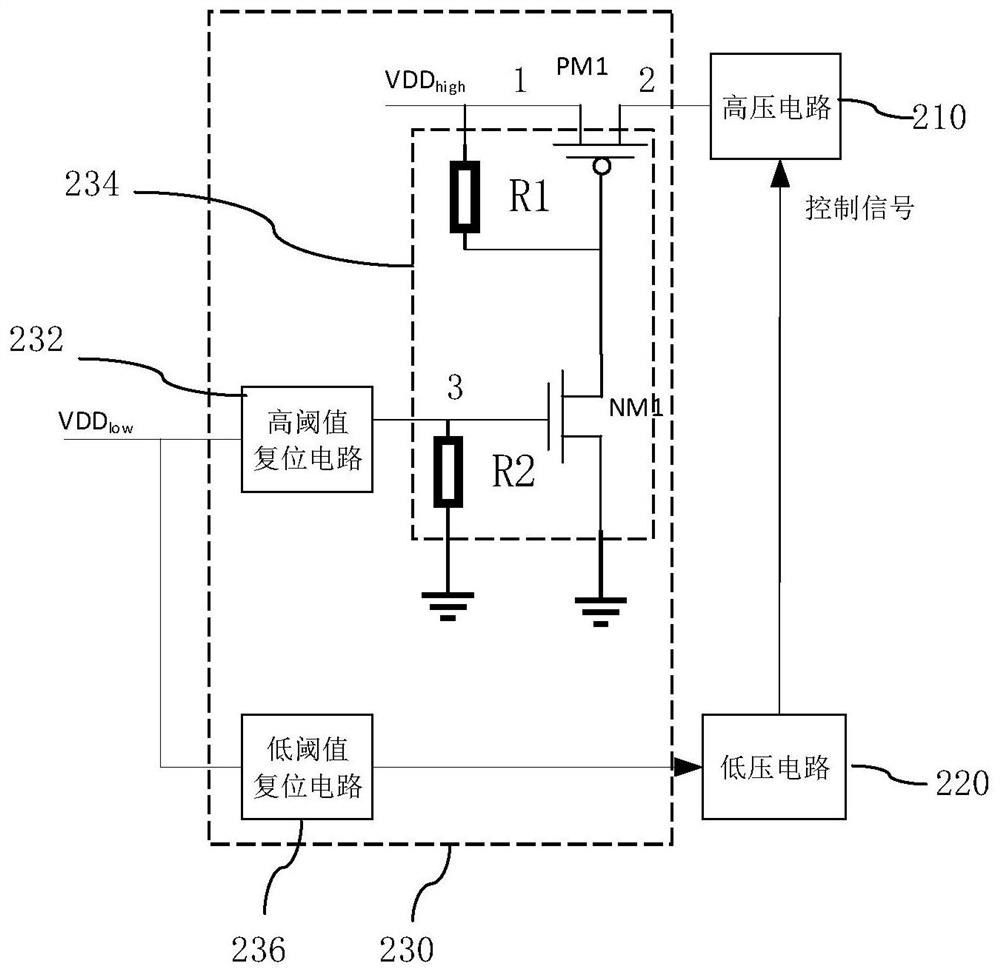

请参考图2所示,其为本发明在一个实施例中的双电压阈电路的电路示意图。图2所示的双电压阈电路包括高压电路(或第一电路)210、低压电路(或第二电路)220和掉电防护电路230。

掉电防护电路230包括高阈值复位电路(或第一阈值复位电路)232、开关电路234和低阈值复位电路(或第二阈值复位电路)236。

高阈值复位电路232的输入端与低电压源(或第二电压源)VDD

开关电路234的第一连接端1与高电压源(或第一电压源)VDD

低阈值复位电路236的输入端与低电压源VDD

其中,高电压源VDD

此外,低压电路220的输出端与高压电路210的控制端相连,低压电路220通过其输出端输出控制信号给高压电路210的控制端,以控制所述高压电路210。高电压源VDD

在图2所示的实施例中,开关电路234包括第一电阻R1、第二电阻R2、第一MOS管PM1和第二MOS管NM1。其中,第一MOS管PM1的第一连接端与开关电路234的第一连接端1相连,其第二连接端与开关电路234的第二连接端2相连,其控制端经第一电阻R1与高电压源VDD

在图2所示的具体实施例中,第一MOS管PM1为PMOS晶体管,第一MOS管MP1的第一连接端、第二连接端和控制端分别为PMOS晶体管的源极、漏极和栅极;第二MOS管NM1为NMOS晶体管,第二MOS管NM1的第一连接端、第二连接端和控制端分别为NMOS晶体管的漏极、源极和栅极;高阈值复位电路232输出的第一电平为高电平,其输出的第二电平为低电平。

在图2所示的具体实施例中,当低电压源VDD

需要特别说明的是,在另一个实施例中,可以将图2中的电阻R2去除,并且其与图2所示的实施例不同的是,当低电压源VDD

如果高电压源VDD

此外,搭载图2所示的设置有掉电防护电路230的双电压阈电路的产品已证明本方案简单可靠且成本低廉。

在本发明中,“连接”、“相连”、“连”、“接”等表示电性连接的词语,如无特别说明,则表示直接或间接的电性连接。

需要指出的是,熟悉该领域的技术人员对本发明的具体实施方式所做的任何改动均不脱离本发明的权利要求书的范围。相应地,本发明的权利要求的范围也并不仅仅局限于前述具体实施方式。

- 双电压阈电路及其掉电防护电路

- 能与阈电压无关地稳定产生中间电位的电压发生电路