一种基于FPGA多通道自适应合成模块及其实现方法

文献发布时间:2023-06-19 18:29:06

技术领域

本发明涉及FPGA的模块设计,特别是一种基于FPGA多通道自适应合成模块及其实现方法。

背景技术

在FPGA做数据加速计算处理时,通常会在处理的部分环节将数据进行多通道合成处理。然后不同的应用场景下,并行通道的数量、通道分组合成组数等场景往往也不同,按照传统的FPGA处理方法,不同场景下需要定制不同的模块方案。定制化方案一方面增加了设计师的工作量,另一方面新研的定制模块也降低了程序整体的可靠性。同时多通道合成处理如果要支持多种场景,也可能造成FPGA资源浪费的问题。因此如何设计通用化的多通道合成程序架构,在实现多通道合成通用化的同时,保持程序的资源占用最低是提升工作效率和产品质量的当务之急。

发明内容

针对现有技术中存在的问题,本发明提供了一种克服了传统通道合成模块不同场景定制化开发耗时耗力的缺点,提供通用化的多通道合成模块,同时解决代码通用化和程序资源最优化之间的矛盾,满足并行通道合成处理的多种场景需求的基于FPGA多通道自适应合成模块及其实现方法。

本发明的目的通过以下技术方案实现。

一种基于FPGA多通道自适应合成模块,包括:

参数管理模块,用于系统参数的配置和管理,包括通道数、通道分组加组数、通道累加拍数,多通道加模块复用时,通过配置参数管理部分,实现复用与资源优化;

通道折叠加模块,通道折叠加模块是多通道加的核心模块,用于将总通道数对半相加,通过通道折叠加模块的迭代得到最后的加结果,同时中间折叠加的结果作为分组加结果输出;

通道累加模块,区别于折叠加累加模块通过配置累加拍数对通道的时域上进行累加;

位宽管理模块,针对不同的通道数和不同的分组数,在折叠加和累加的过程中,计算结果的位宽会发生变化,通过位宽管理预先配置好加结果位宽。

分组选择模块,将全部通道按照不同的分组进行并行加计算,分组选择则通过配置的动静态参数完成分组加结果选择输出。

时钟模块,产生各模块的工作时钟。

一种基于FPGA多通道自适应合成实现方法,步骤包括:

a.配置参数管理模块的参数,参数管理通过计算,将其他各模块的动态和静态参数计算准备完成;

b.根据参数管理模块配置号的折叠加次数,折叠加模块将全部通道进行迭代折叠加,折叠加时会根据这叠加通道数是否是偶数进行通道数补足;

c.根据参数管理模块配置的分组数,选择折叠加模块相应迭代次数结果作为分组选择模块输出;

d.根据参数管理模块配置号的累加次数,通道累加模块将折叠加结果进行累加,作为最终输出。

相比于现有技术,本发明的优点在于:1.多通道加采用了通用化的设计方案,通过配置顶层静态参数,支持多种合成场景,节约了产品复用的时间和人力成本80%以上

2.与定制化的通道加相比,资源使用上基本持平,最小化的资源使用保证了产品的可靠性和可扩展性。

3.通用化的模块设计通过不断的应用迭代,能够提升代码的可靠性,大大减少新研产品通道加模块的故障率。

附图说明

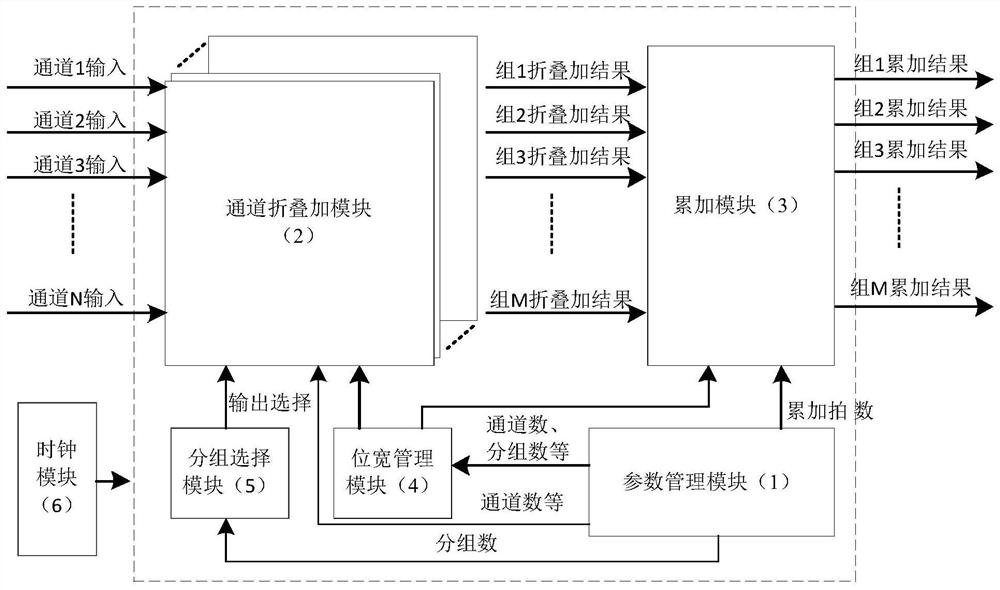

图1基于FPGA的多通道自适应合成模块框图。

图2多通道自适应加流程图。

具体实施方式

下面结合说明书附图和具体的实施例,对本发明作详细描述。

如图1所示,一种基于FPGA的多通道自适应合成模块,包括:

参数管理模块1,用于系统参数的配置和管理,包含通道数、通道分组加组数、通道累加拍数等,多通道加模块复用时,通过配置参数管理部分,实现复用与资源优化;

通道折叠加模块2,通道折叠加模块是多通道加的核心模块,其主要功能时将总通道数对半相加,通过通道折叠加模块的迭代便可以得到最后的加结果,同时中间折叠加的结果也可以作为分组加结果输出;

通道累加模块3,区别于折叠加累加模块通过配置累加拍数对通道的时域上进行累加;

位宽管理模块4,针对不同的通道数和不同的分组数,在折叠加和累加的过程中,计算结果的位宽也会发生变化,因此需要通过位宽管理预先配置好加结果位宽。

分组选择模块5,在某些场景中,需要将全部通道按照不同的分组进行并行加计算,分组选择则通过配置的动静态参数完成分组加结果选择输出。

时钟模块6,产生各模块的工作时钟,在应用系统中,可与其他模块共用一个时钟模块。

本模块的实现方法和步骤如下所示:

a.配置参数管理模块1的参数,参数管理通过计算,将其他各模块的动态和静态参数计算准备好。

b.根据参数管理模块1配置号的折叠加次数,折叠加模块2将全部通道进行迭代折叠加,折叠加时会根据这叠加通道数是否是偶数进行通道数补足。

c.根据参数管理模块1配置的分组数,选择折叠加模块2相应迭代次数结果作为分组选择模块5输出。

d.根据参数管理模块1配置号的累加次数,通道加模块3将折叠加结果进行累加,作为最终输出。

为实现该模块,结合图1、图2对本发明做进一步详细描述:

本模块具体的工作流程如图2,首先是参数管理模块1根据配置的通道总数和最大分组数确定通道加需要折叠的次数A,再将总通道数按照折叠次数A进行A次的折叠加,每次加之前需要进行两个操作,一是对加通道补足至偶数,而是对通道位宽进行补足。同时将上次折叠加的结果作为下次折叠加的输入。

- 一种基于FPGA的OTL协议多通道数据对齐的实现方法

- 一种多通道数据源DDR缓存的FPGA实现方法

- 一种基于FPGA多通道基带数据幅相补偿的实现方法

- 一种基于FPGA的多通道耦合输出实现电路及方法