硬件自动加载器

文献发布时间:2023-06-19 18:32:25

技术领域

本公开涉及向集成电路的多个处理器提供应用。

背景技术

当执行大规模并行操作时,可以在单个集成电路(即,芯片)上提供包括多个处理器的处理单元。每个处理器被配置为通过使用应用数据(例如,应用的输入变量)的集合执行可执行应用指令的集合来执行应用的操作。

包括多个处理器的处理单元的使用的一个示例在机器学习算法的上下文中找到,例如,在深度神经网络的上下文中。如机器智能领域的技术人员所熟悉的那样,机器智能算法基于“知识模型”,该“知识模型”可以由多个互连的节点的图表示。每个节点表示其输入的函数。一些节点接收图的输入,并且一些节点接收来自一个或多个其他节点的输入,而一些节点的输出形成其他节点的输入,并且一些节点的输出提供图的输出(并且在一些情况下给定节点甚至可以具有所有这些:图的输入、图的输出以及与其他节点的连接)。另外,每个节点处的函数由一个或多个相应参数(即,权重和偏置)参数化。

通常,每个节点的处理中的至少一些可以独立于图中的一些或所有其他节点执行,因此大图为并发和/或并行性提供了大的机会。计算机中的每个处理器可以被用于执行与不同节点相关联的处理。以这种方式,多个处理器可以被共同用于训练或操作单个神经网络。

与机器学习模型相关的处理可以被划分为操作阶段和训练阶段。在训练阶段期间,使用定义机器学习模型的状态的数据来处理输入数据的集合以产生用于机器学习模型的输出值。定义机器学习模型的状态的数据包括指示模型的哪些节点已连接的信息,以及附加地在训练期间变化的模型参数(包括例如权重和偏置)。将训练期间获得的输出值的集合与标签的集合进行比较,并更新模型参数,以便调谐模型以更准确地从输入值的集合再现标签。一旦训练了机器学习模型,就在操作阶段期间处理输入数据的集合以使用训练期间获得的经调谐的参数产生输出值。

在用于机器学习模型的操作和训练阶段使用的数据的不同集合(即,输入数据、定义节点之间连接的信息、模型参数和标签)构成应用数据,其由一个或多个处理器处理以执行机器学习模型的训练和/或操作。必须将可执行指令的集合加载到多处理器系统中才能使用这个应用数据执行操作。将可执行指令的集合加载到多处理器系统中,虽然是机器学习上下文中出现的要求,但不限于这个上下文并且可以出现在其他类型的应用的上下文中。

发明内容

当将可执行指令的集合加载到多处理器集成电路中时,一个挑战是要防止不受信任的指令和数据被加载到每个处理器中。如果恶意的第三方要访问每个处理器的存储装置,其可能能够将软件安装到处理器中,从而允许他们访问由租户提供给处理器的真实应用数据。在许多情况下,真实应用指令和数据是机密的并且应当对恶意第三方保密。因此,需要确保只有受信任的应用指令才从外部存储器移入到每个处理器的存储器中。

根据第一方面,提供了一种包括多个处理器的集成电路,多个处理器中的每个处理器包括:至少一个存储器,用于存储应用数据和可执行应用指令的集合;以及至少一个执行单元,其中该集成电路包括硬件模块,该硬件模块包括包含可执行引导指令的集合的存储器,其中该硬件模块包括处理电路,该处理电路被配置为使得可执行引导指令的集合经由集成电路的互连而被分派到多个处理器中的至少一些处理器,其中对于多个处理器中的至少一些处理器中的每个处理器,相应的至少一个执行单元被配置为:执行接收到的可执行引导指令的集合以使得读请求被发出到集成电路外部的至少一个存储器,以获取可执行应用指令的集合;以及执行可执行应用指令的集合以使用应用数据执行操作。

多处理器集成电路设有硬件模块,该硬件模块由受信任的软件配置以向处理器的集合中的每个处理器提供引导加载器(bootloader)。通过这样做,每个处理器都安全地设有受信任的引导加载器。受信任的引导加载器被用于确保每个处理器向存储正确应用指令的外部存储器位置发出读请求。从而防止处理器读取不正确的指令,这些指令可能是由恶意第三方提供的软件。因此,提高了集成电路的安全性。此外,这种技术具有实现应用的快速引导的优点。

在一些实施例中,对于多个处理器中的至少一些处理器中的每个处理器:执行接收到的可执行引导指令的集合包括根据集成电路中相应的处理器的标识符计算外部存储器的地址,使得读请求被发出包括使得读请求被发出以从外部存储器中的计算出的地址获取可执行应用指令的集合。

在一些实施例中,硬件模块包括处理电路,该处理电路被配置为使得一个或多个写请求被分派到多个处理器中的至少一些处理器中的每个处理器,以使得未被可执行引导指令的集合占用的存储器空间被清除。

在一些实施例中,对于多个处理器中的至少一些处理器中的每个处理器:相应的至少一个执行单元被布置为使得在相应的可执行指令的集合的执行期间生成的检查点数据在写请求中被分派到集成电路外部的存储装置。

在一些实施例中,硬件模块的处理电路被配置为,在使得生成的检查点数据被分派之后,使得可执行引导指令的集合再次经由集成电路的互连而被分派到多个处理器中的至少一些,其中对于多个处理器中的至少一些处理器中的每个处理器,相应的至少一个执行单元被配置为随后:执行接收到的可执行引导指令的集合以使得读请求被发出到集成电路外部的存储器,以获取可执行应用指令的集合和包括检查点数据的应用数据的另一个集合;以及执行可执行应用指令的集合以使用检查点数据的值来执行操作。

在一些实施例中,应用数据的另一个集合包括不变数据的集合,其中不变数据是在分派检查点数据之前获取的应用数据的一部分,其中应用数据的另一个集合包括代替可变数据的检查点数据,其中可变数据是在分派检查点数据之前获取的应用数据的一部分。

在一些实施例中,对于多个处理器中的至少一些处理器中的每个处理器,相应的至少一个执行单元被配置为执行可执行应用指令的相应集合以从集成电路外部的至少一个存储器加载应用数据的至少一部分。

在一些实施例中,对于多个处理器中的至少一些处理器中的每个处理器,相应的至少一个执行单元被配置为执行接收到的可执行引导指令的集合以使得读请求被发出到集成电路外部的至少一个存储器以获取应用数据的至少一部分。

在一些实施例中,硬件模块包括被配置为存储可执行引导指令的集合的易失性存储器,其中硬件模块的处理电路被配置为,在集成电路的重置之后:从集成电路外部的设备接收可执行引导指令的集合;以及将接收到的可执行引导指令的集合存储在易失性存储器中。

在一些实施例中,从集成电路外部的设备接收可执行引导指令的集合包括经由JTAG接口接收可执行引导指令的集合。

在一些实施例中,硬件模块包括被配置为存储可执行引导指令的集合的非易失性存储器。

在一些实施例中,硬件模块的存储器被配置为存储可执行引导指令的多个集合,其中处理电路被配置为使得可执行引导指令的多个集合中的每个集合被分派到集成电路的处理器的子集。

根据第二方面,提供了一种数据处理系统,包括:根据第一方面的集成电路;以及数据提供系统,其包括集成电路外部的存储器。

在一些实施例中,数据提供系统包括至少一个处理器,该处理器被配置为响应于在数据提供系统处接收到来自集成电路的同步请求而使得用于一组处理器的应用数据被加载到集成电路外部的存储器中。

在一些实施例中,数据提供系统的至少一个处理器被配置为根据从集成电路接收到的处理器组的标识符而将应用数据布置在集成电路外部的存储器中。

根据第三方面,提供了一种在包括多个处理器的集成电路中实现的方法,在集成电路的硬件模块中存储可执行引导指令的集合,使得可执行引导指令的集合经由集成电路的互连而被分派到多个处理器中的至少一些处理器,在多个处理器中的至少一些处理器中的每个处理器上,执行接收到的可执行引导指令的集合以使得读请求被发出到集成电路外部的存储器,以获取可执行应用指令的集合;以及执行可执行应用指令的集合以使用应用数据执行操作。

根据第四方面,提供了一种包括计算机可执行指令的计算机程序,该计算机可执行指令在由包括多个处理器的集成电路的硬件模块的处理电路执行时使得执行一种方法,该方法包括:在集成电路的硬件模块中存储可执行引导指令的集合,使得可执行引导指令的集合经由集成电路的互连而被分派到多个处理器中的至少一些处理器,在多个处理器中的至少一些处理器中的每个处理器上,执行接收到的可执行引导指令的集合以使得读请求被发出到集成电路外部的存储器,以获取可执行应用指令的集合;以及执行可执行应用指令的集合以使用应用数据执行操作。

根据第五方面,提供了一种存储根据第四方面的计算机程序的非暂态计算机可读介质。

附图说明

为了更好地理解本发明并示出如何实现本发明,现在将通过示例的方式参考附图,其中:

图1是多芯块处理器的示意图;

图2是图示多芯块处理器内的计算和交换阶段的示意图,

图3图示了海量同步并行系统中的数据的交换,

图4图示了用于将数据分组从芯块发送到芯片外的布置,

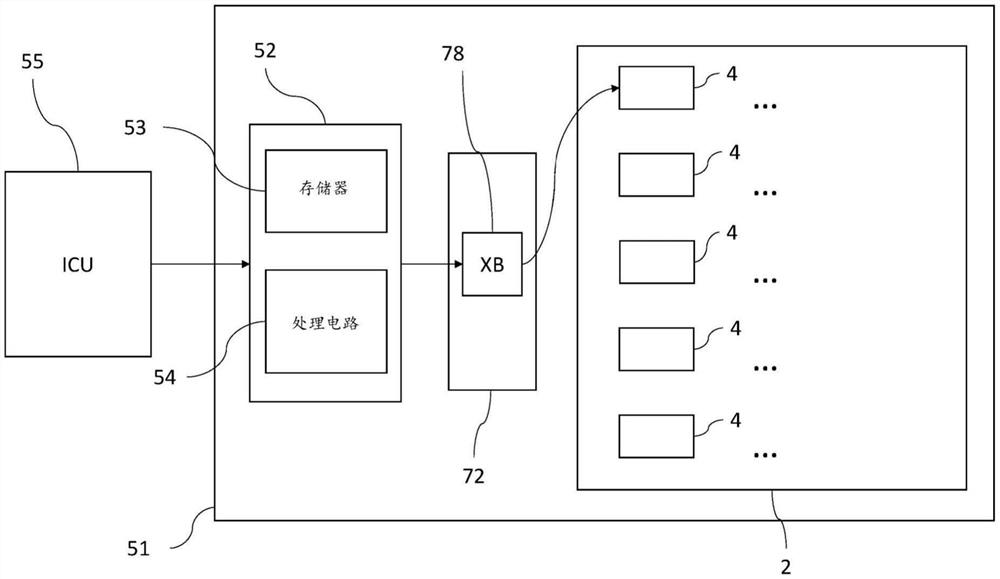

图5A图示了根据实施例的将次级引导加载器代码分发到芯片的芯块,

图5B图示了根据又一个实施例的将次级引导加载器代码分发到芯片的芯块,

图6图示了处理器存储器中数据的布局的示例,

图7图示了同步请求和确认的传播,

图8图示了由芯块从外部存储器读取应用数据,

图9图示了由芯块对应用数据的检查点设定,以及

图10是示例处理器的示意性框图。

具体实施方式

本申请的实施例涉及一种用于将应用指令安全地分发到处理单元的处理器的新装置和方法。处理单元被形成为集成电路的一部分并且包括多个处理器(称为芯块(tile)),每个处理器具有它们自己的执行单元和用于存储应用数据和可执行应用指令的存储器。集成电路包括硬件模块(本文中称为自动加载器(autoloader)),其被配置为将引导加载器指令的集合(本文称为次级引导加载器)分发到至少一些芯块中的每个芯块。然后每个芯块执行接收到的次级引导加载器的指令,这使得每个芯块发出读请求以从集成电路外部的存储器读取应用指令。然后每个芯块使用接收到的应用指令对应用数据执行操作以执行应用。应用数据包括可以通过执行次级引导加载器来加载或者可以通过执行应用指令本身来加载的变量。

次级引导加载器指令和用于配置自动加载器的处理电路以将次级引导加载器指令传送到芯块的软件都是受信任的。这意味着可以依赖它们来执行安全策略,在这种情况下是对将恶意代码加载到芯块中的防范。从中加载应用指令的系统(在所描述的实施例中是主机)是不受信任的,并且在不使用受信任的次级引导加载器的情况下不能依赖它来向芯块提供正确的应用指令。

本申请的实施例可以使用我们更早的美国申请号15/886315中描述的智能处理单元(IPU)来实现,其内容通过引用并入。这些IPU中的每一个都在单个集成电路上形成。但是,本发明不限于IPU并且可以在其他类型的处理单元中实现。

图1进一步图示了示例处理单元2,图1图示了多芯块处理单元2的示例。处理单元2包括多个处理器芯块4的阵列6以及在芯块4之间连接的互连34。处理单元2可以被单独实现为包装在同一IC包装中的多个晶粒(die)之一。互连34在本文中也可以被称为“交换架构”34,因为它使芯块4能够彼此交换数据。每个芯块4包括执行单元和存储器的相应实例。例如,作为说明,处理单元2可以包括数百个或甚至超过一千个的芯块4的数量级。为完整起见,还注意的是,本文所提到的“阵列”不一定暗示芯块4的任何特定数量的维度或物理布局。

在实施例中,每个处理单元2还包括一个或多个外部链路8,使得处理单元2能够连接到一个或多个其他处理单元(例如,同一处理单元2的一个或多个其他实例)。这些外部链路8可以包括以下任何一项或多项:用于将处理单元2连接到主机系统的一个或多个处理器到主机链路,和/或一个或多个处理器到处理器链路,用于将同一IC包装或卡上或不同卡上的处理单元2的一个或多个实例连接在一起。处理单元2的多个实例可以通过处理单元到处理单元链路一起连接到卡中。处理单元2以要由处理单元2处理的应用数据的形式从连接到处理单元2的外部存储器接收工作。

互连34被配置为使阵列6中的不同芯块4能够彼此通信。但是,除了在同一个芯块4上的线程之间可能存在依赖关系之外,在阵列6中的不同芯块4上运行的程序的部分之间也可以存在依赖关系。因此,需要一种技术来防止一个芯块4上的一段代码在它所依赖的数据通过另一个芯块4上的另一段代码变得可用之前运行。

处理单元2上的芯块4之间的通信以时间确定性方式发生。但是,其他形式的芯块间交换也是可能的。在阵列6中的不同芯块4上运行的程序的部分之间可以存在依赖关系。即,在一个芯块4上处理数据可以取决于来自另一个芯块4的结果,例如,可以提供另一个芯块所依赖的结果。因此,需要一种技术来防止一个芯块4上的一段代码在它所依赖的数据通过另一个芯块4上的另一段代码变得可用之前运行。

用于AI和数据科学的并行编程模型通常遵循3阶段迭代执行模型:计算、屏障和交换。这意味着进出处理器的数据传送通常依赖于屏障,以提供处理器之间以及每个处理器与外部存储装置之间的数据一致性。通常使用的数据一致性模型是海量同步并行(BSP)、陈旧同步并行(SSP)和异步。本文描述的实施例使用BSP模型,但是显然可以使用其他同步模型作为替代。

参考图2和图3,它们图示了BSP交换方案的实施方式,其中每个芯块4在交替的周期中执行计算阶段33和交换阶段32,通过芯块之间的屏障同步30彼此分开。在图2和3所示的情况下,在每个计算阶段33和随后的交换阶段32之间放置屏障同步。在计算阶段33期间,每个芯块4在芯块上本地执行一个或多个计算任务,但不与芯块4中的任何其他芯块交流这些计算的任何结果。在交换阶段32中,每个芯块4被允许将来自先前计算阶段的计算的一个或多个结果交换给一个或多个其他芯块4和/或从其交换,但不执行任何新的计算,直到它从其他芯块4接收到其(一个或多个)任务具有依赖关系的任何数据。除了在先前计算阶段中计算出的数据之外,它也不会将任何数据发送到任何其他芯块4。不排除在交换阶段32中可以执行诸如内部控制相关操作之类的其他操作。芯块组外部的通信可以可选地使用BSP机构,但可替代地可以不使用BSP并且可以替代地使用它自己的某种其他同步机构。

根据BSP原理,屏障同步30被放置在从计算阶段33过渡到交换阶段32的接合点处,或从交换阶段32过渡到计算阶段33的接合点处,或两者。即,或者:(a)在允许组中的任何芯块前进到接下来的交换阶段32之前,所有芯块4都要求完成它们相应的计算阶段33,或者(b)在允许组中的任何芯块进行到接下来的计算阶段33之前,该组中的所有芯块4都要求完成它们相应的交换阶段32,或者(c)这两个条件都被强制执行。在所有三个变体中,是各个芯块在阶段之间交替,并且整个组件同步。交换和计算阶段的序列然后可以重复多次。在BSP术语中,交换阶段和计算阶段的每次重复有时被称为“超级步骤”(但注意的是,在文献中该术语并不总是一致地被使用:有时每个个体交换阶段和计算阶段单独称为超级步骤,而在其他地方,如本文采用的术语中,交换和计算阶段一起被称为超级步骤)。

还要注意的是,不排除同一处理单元2或不同处理单元上芯块4的多个不同的独立组可以各自形成彼此异步操作的单独的相应BSP组,其中计算、同步和交换的BSP周期只在每个给定的组内强加,但每个组都独立于其他组这样做。即,多芯块阵列6可以包括多个内部同步组,每个组独立操作并且与其他这样的组异步操作(稍后更详细地讨论)。在一些实施例中,存在同步和交换的分层分组,如稍后将更详细地讨论。

图3图示了在强加:(a)从计算阶段33到交换阶段32的屏障同步(参见以上)的情况下在阵列6中一些或所有芯块的组4i、4ii、4iii当中实现的BSP原理。注意的是,在这种布置中,一些芯块4被允许开始计算33,而其他一些芯块仍在交换。

处理单元2的芯块4之间的通信以时间确定性方式发生,其中数据分组在没有报头的情况下被传输。这在我们更早的美国专利申请号15/886315中进行了解释。

图4图示了用于将数据分组从芯块发送到处理单元2外部的目的地的示例性机构。这种机构是非时间确定性的。该机构在外部互连72中的专用硬件逻辑中实现。数据以分组的形式通过外部互连72发送。与通过内部互连34发送的分组不同,这些分组具有报头:由于传输的次序可以改变,它们要求在分组报头中呈现目的地地址。外部互连72包括路由表,用于根据数据分组的报头在不同处理器之间静态地路由数据分组。

在物理层处,互连机构是有损的,但在业务层处,由于链路层的体系架构,该机构不是有损的:如果分组没有得到确认,那么它将被互连72中的硬件自动重新发送。但是,在数据链路层丢失和重新发送的可能性意味着通过外部互连72的数据分组的递送不是时间确定性的。另外,给定交换的所有分组可以在时间上以任何次序一起到达或分开到达,因此外部互连要求流量控制和排队。另外,互连可以使用时钟数据恢复(CDR)技术从具有足够数据信号过渡的接收到的数据流推断时钟以维持位锁定。这个推断的时钟与发送时钟的相位关系未知,因此表示非确定性的附加源。

如图所示,外部互连72包括外部交换块(XB)78。编译器指定芯块4之一向交换块78发送外部交换请求(XREQ)(操作S1)。XREQ是包括一个或多个控制分组的消息,指示芯块4中的哪些具有要发送的数据分组(内容)。这在图4中通过勾号和叉号示意性地图示:作为示例场景,标有勾号的那些具有要向外部发送的数据分组,而标有叉号的那些则没有。在操作S2中,交换块78将交换开启(XON)控制分组发送到具有要向外部发送的数据的芯块4中的第一个。这使得第一芯块4开始经由外部互连72将其分组发送到相关目的地(操作S3)。使用外部互连72中的路由表将在外部互连处从第一芯块接收到的数据分组静态地路由到目的地。如果在任何时候XB 78无法继续向互连发送分组(例如,由于先前的分组丢失和互连中的重新传输,或由于许多其他XB和芯块对外部互连过度订阅),那么XB 78将在XB 78队列溢出之前向那个芯块4发送交换关闭(XOFF)。一旦拥塞被清除并且XB 78在其队列中再次具有足够的空间,它就将向芯块4发送XON,从而允许它继续传输其内容。一旦这个芯块4发送了它的最后一个数据分组,在操作S4中,交换块78就向这个芯块4发送交换关闭(XOFF)控制分组,然后在操作S5中向下一个芯块4发送另一个XON以及要发送的数据分组,等等。XON和XOFF的信令在外部交换块78形式的专用硬件逻辑中被实现为硬件机构。

虽然在图4中仅示出了单个交换块78,但是可以存在多个不同的交换块,其中每个交换块服务于处理单元2中的芯块4的子集。在实施方式中,例如,其中形成处理单元2的集成电路包括八个交换块,每个交换块对处理单元中八分之一的芯块4执行图4中所示的功能。

每个处理器芯块4包括处理电路和存储器。在一些示例实施例中,处理电路是多线程处理器10。图10图示了根据本公开的实施例的处理器芯块4的示例。处理器芯块4包括桶线程处理器10形式的多线程处理器10和本地存储器11(即,在多芯块阵列的情况下在同一芯块上,或者在单处理器芯片的情况下在同一芯片上)。桶线程处理器10是一种类型的多线程处理器10,其中管线的执行时间被划分为交织时隙的重复序列,每个时隙可以由给定线程拥有。稍后将对此进行更详细的讨论。存储器11包括指令存储器12和数据存储器22(其可以在不同的可寻址存储单元或同一可寻址存储单元的不同区域中实现)。指令存储器12存储将由处理单元10执行的机器代码,而数据存储器22存储将由被执行代码操作的数据和由被执行代码输出的数据(例如,作为此类操作的结果)。

存储器12存储程序的各种不同线程,每个线程包括用于执行一个或多个特定任务的相应指令序列。注意的是,如本文提到的指令是指机器代码指令,即,处理器的指令集的基本指令之一的实例,由单个操作码和零个或多个操作数组成。

在处理器10内,来自指令存储器12的线程中的多个不同线程可以通过单个执行管线13交织(虽然通常只有存储在指令存储器中的所有线程的子集可以在整个程序中的任何给定点被交织)。多线程处理器10包括:多个上下文寄存器文件26,每个上下文寄存器文件被布置为表示要被并发执行的线程中不同相应线程的状态(上下文);共享执行管线13,其对于并发执行线程是共用的;以及调度器24,用于调度并发线程以供以交织方式,优选地以循环方式,通过共享管线执行。处理器10连接到多个线程共用的共享指令存储器12,以及多个线程也共用的共享数据存储器22。

执行管线13包括获取级14、解码级16和执行级18,执行级18包括可以执行算术和逻辑运算、地址计算、加载和存储操作以及由指令集体系架构定义的其他操作的执行单元。上下文寄存器文件26中的每一个包括用于表示相应线程的程序状态的相应寄存器集合。

参考图5A,其图示了集成电路51,其中次级引导加载器代码被分发到集成电路51的多个芯块4。集成电路51包括上面讨论的处理单元2。集成电路51还包括硬件模块52,其在本文中被称为自动加载器52。自动加载器52被定义为用于集成电路51的主引导加载器。自动加载器52执行向多个芯块4提供次级引导加载器并擦除芯块存储器的剩余区域的功能。

自动加载器52包括存储指令的一个或多个集合的存储器53,这些指令可由芯块4执行以从外部存储装置获取应用指令。引导指令的一个或多个集合中的每个引导指令被称为次级引导加载器或次级引导加载器映像。相同的次级引导加载器被加载到多个不同的芯块4中。在一些情况下,相同的次级引导加载器可以被加载到处理单元2中的所有芯块4中。在其他情况下,第一次级引导加载器可以被加载到芯块4的第一集合中,同时一个或多个另外的引导加载器被加载到处理单元2中的其他芯块4。在一些情况下,一些芯块4不接收任何次级引导加载器。不接收任何次级引导加载器的芯块4将不会从外部存储器获取应用指令。

为了将次级引导加载器递送到芯块4之一,自动加载器52的处理电路54从存储器53加载次级引导加载器并处理次级引导加载器以产生一个或多个数据分组。一个或多个数据分组在一个或多个数据分组的(一个或多个)有效载荷中包含次级引导加载器代码。一个或多个数据分组中的每个数据分组都在分组的报头中包含次级引导加载器将被分派到的相关芯块4的标识符。报头还包括块存储器中的地址,其指示在识别出的芯块的存储器中要写入次级引导加载器的位置。处理电路54使相关的一个或多个数据分组通过集成电路51的互连被分派到交换块78。交换块78将分组转换成适当的格式以便通过处理单元2的互连传输到相关芯块4。交换块78使一个或多个数据分组被分派到在(一个或多个)报头的地址中指示的芯块4。在接收到一个或多个数据分组后,芯块4的处理电路处理数据分组以提取次级引导加载器代码并将次级引导加载器代码存储在存储器中。

自动加载器52可被配置为将次级引导加载器代码写入集成电路51中芯块4的不同子集。例如,芯块4可以被划分为32个不同的子集,自动加载器52被编程在具有向其提供次级引导加载器的子集的配置寄存器中。当将次级引导加载器分派到芯块的子集时,自动加载器52可以向次级引导加载器的第一部分的子集中的每个芯块4发出写入到该子集中每个芯块4在存储器中的位置。自动加载器52然后再次循环通过芯块的子集,这次是通过写入递增的芯块地址。自动加载器52将次级引导加载器的第二部分写入子集中每个芯块4在存储器中的下一个空闲位置。自动加载器52以这种方式继续,直到引导加载器被写入子集中的所有芯块4。

参考图6,其图示了被提取到存储器11中的数据和指令在芯块存储器11中的布局的示例。存储器11不需要是物理上连续的存储器空间。存储器11的第一部分是保留区域。次级引导加载器占用保留区域的一部分,保留区域的剩余部分不包含任何数据或代码,即,为空白。在实施例中,保留区域为16KB,次级引导加载器占用大约1KB的保留区域。除了保留区域,存储器11还包括可以被用于存储从外部存储器检索到的应用指令和数据的存储器空间。

在将次级引导加载器写入芯块4之后,自动加载器52然后被配置为清除剩余的芯块存储器11。通过以这种方式重置复芯块存储器11,在重置或电力周期之后持久化的属于处理单元2的前一租户的任何数据将被移除。自动加载器52通过分派写分组以写入除次级引导加载器代码占用的所有块存储器空间以外的所有芯块存储器空间来执行这种清除。分派的分组与自动加载器52分派以将次级引导加载器写入芯块存储器的分组类型相同,但不是包括要写入芯块存储器11的次级引导加载器的代码,分组包括要被写入分组报头中指示的芯块存储器11中的位置的一系列零。因此,对于向其写入次级引导加载器代码的多个芯块4中的每个芯块,自动加载器52分派一系列分组以将零写入芯块存储器11中不包括次级引导加载器的其他位置。

如所指出的,次级引导加载器可以不被写入处理单元2中的每个芯块4。因此,对于次级引导加载器未被写入的那些芯块4,自动加载器52将零写入所有块存储器11。其整个存储器11是空白的这些芯块4在应用的处理期间将不被使用。

由自动加载器52执行的芯块存储器11的清除使得接收到次级引导加载器的芯块4中的每个芯块开始执行该次级引导加载器。

在图5A中所示的实施例中,自动加载器52从集成电路51外部的设备55接收一个或多个次级引导加载器。设备55在本文中被称为智能密码单元(ICU)。ICU 55包括非易失性存储器(诸如闪存)或与其相关联。另一方面,自动加载器存储器53是易失性存储器,诸如SRAM。因此,与ICU 55相关联的非易失性存储器存储一个或多个次级引导加载器,使得(一个或多个)次级引导加载器可以在集成电路51断电和重启之后对芯块4可用。在集成电路51重启后,ICU 55向集成电路51的自动加载器52提供一个或多个次级引导加载器。ICU 55通过接口进行相继写入以向集成电路51提供一个或多个次级引导加载器。ICU 55经由集成电路51的JTAG接口向自动加载器52提供一个或多个次级引导加载器。然后在将一个或多个次级引导加载器提供给芯块4之前将其存储在自动加载器52的易失性存储器53中。

与自动加载器52能够写入芯块4的存储器的片上互连相比,ICU 55提供第二引导加载器代码到存储器53的写入的接口具有高时延。因此ICU 55本身将引导加载器代码单独写入每个芯块4的速度将慢。通过ICU 55将引导加载器代码写入自动加载器52,然后自动加载器将那个引导加载器代码通过高速片上互连提供给多个不同的芯块4,这实现了显著的效率增益。

参考图5B,其图示了集成电路51a的替代实例。在这种情况下,集成电路51a包括CCU 56。CCU 56用作自动加载器并且包括存储器53a和处理电路54a。存储器53a执行上文针对存储器53讨论的相同功能,即,存储器53a存储要分发给多个芯块4的次级引导加载器。处理电路54a执行上文针对处理电路54讨论的相同功能,包括执行使次级引导加载器被分发到多个芯块4的指令并清除芯块存储器。处理电路54a由受信任的软件配置以发出将次级引导加载器写入芯块4的存储器的写请求。存储器53a包括被配置为存储第二引导加载器的非易失性存储器53a,使得当集成电路51a断电时,次级引导加载器不会从存储器53a中丢失。因此,在这个实施例中,不要求诸如ICU 55之类的外部设备来存储次级引导加载器代码并将其提供给集成电路51a。

图5B中所示的其他元件以与图5A中所示的对应元件相同的方式操作。

参考图7和8,其图示了一旦次级引导加载器已被写入多个芯块4,应用指令如何从外部存储器70中检索。

在这个示例中,外部存储器70被示为主机系统71的一部分。但是,在其他示例中,系统71可以是将集成电路51与主机系统接口的网关。系统71可以是另一种类型的包括外部存储器70的系统。

系统71包括用于从存储器70加载应用指令的至少一个处理器711。该至少一个处理器711可以是被配置为执行计算可读指令的处理器。

包括次级引导加载器的芯块4被划分为不同的同步组,每个同步组将在单独的交换阶段期间检索它们的应用指令。对于集成电路51中的所有芯块4,可以存在四个不同的同步组。存在芯块4可以识别它所属的同步组的不同方式。在一些情况下,不同的次级引导加载器代码可以被分派到属于不同同步组的芯块4。在其他情况下,可以将相同的次级引导加载器代码分派到属于不同同步组的芯块,但是当在每个芯块4上执行时次级引导加载器代码使用芯块4的芯块ID来确定芯块4属于哪个同步组。

芯块4的第一同步组的芯块4各自向交换块78发出同步请求73。每个同步请求73包括向其发出请求的芯块4所属的同步组的指示或以该指示为先导。交换块78存储对那个同步组预期的同步请求73的数量的指示。交换块78接收同步请求73并确定它何时已经接收到针对那个同步组的该数量的预期同步请求73。一旦它已经接收到该数量的预期同步请求73,交换块就将这些同步请求聚合成经由接口75发送的同步请求74。接口75将接收到的同步请求(以分组形式用于通过集成电路51的互连进行传输)转换成PCIe分组以供传输到系统71。

在接收到同步请求74后,系统71将应用指令加载到存储器70中以供递送到属于发出同步请求73的同步组的芯块4。同步请求74包含与其相关的同步组的指示。系统71根据同步组的指示将那个同步组的芯块4所需的应用指令加载到存储器70中。指令从存储装置710加载到存储器70中。存储装置710可以是数据提供系统71或者可以与系统71分开。因此,存储器70可以被理解为数据传送存储器,指令在被相关芯块4获取之前被预加载到其中。

存储器70被布置到多个不同地址空间或缓冲器中,由芯块从这些地址空间或缓冲器读取数据。这些地址空间中的每一个与由芯块读取的不同数据流对应。地址空间不需要是连续的存储器空间,但可以是虚拟缓冲区。

一旦将用于传送到芯块4的应用指令加载到存储器70中完成,系统71就发出同步确认76,该确认被返回到交换块78。交换块78响应于接收到同步确认76而向同步组中的所有芯块4分派同步确认79。

参考图8,其图示了在同步确认79返回到处理单元2的芯块4之后发生的步骤。在接收到同步确认后,每个芯块4等待接收来自交换块78的控制以便发送读请求分组。这根据上面关于图4给出的描述发生。同步组中的每个芯块4向交换块78分派读请求81。为了说明的简单性,在图8中,只示出源自一个芯块4的一个读请求81。交换块78将读请求81传递到接口75。读请求81由接口75转换成PCIe读请求。接口75将读请求81传递给系统71。每个读请求81包括其所针对的存储器70中的地址的指示。响应于读请求81,系统71的处理器产生一个或多个数据分组82,其包括在读请求81中指示的位置处从存储器70读取的数据。这一个或多个生成的数据分组82被称为读完成。系统71将一个或多个读完成82返回给集成电路51。在交换块78处接收一个或多个读完成82,交换块78将读完成提供给读请求81源自的芯块4。然后控制传递到同步组中的下一个芯块4,其发出其从存储器70中的特定位置进行读取的读请求并且然后作为响应接收一个或多个完成。

在同步组中的每个芯块4从存储器70读取其应用指令之后,另一个同步组的芯块4将发出同步请求,这些同步请求由交换块聚合并提供给系统71。系统71响应于接收到这下一个同步请求而将相关应用指令加载到存储器70中以递送到对应同步组的芯块4。然后系统71向集成电路51返回同步确认,这使得同步组的芯块4发出从存储器70进行读取的读请求。

同步请求/确认和从存储器70读取的过程一直持续到具有次级引导加载器的所有芯块4都已从存储器70加载了它们的应用指令。

从存储器70加载应用指令的芯块4中的每个芯块使用存储在芯块4中的存储装置(不同于存储器11)中的芯块4的芯块标识符(芯块ID)确定要从其读取的地址。由于多个芯块4接收相同的次级引导加载器,因此次级引导加载器被配置为从存储器70中取决于芯块ID的位置加载指令。次级引导加载器根据它在其上运行的芯块的ID计算从中读取存储器70的地址。

如上所述,应用指令由芯块执行以使用应用数据(例如,变量)执行操作。这个应用数据可以与应用指令同时并以相同方式加载到芯块4中,即,通过执行次级引导加载器指令以发出从主机71的存储器70加载数据的读请求。附加地或可替代地,应用数据可以由芯块4加载,它们执行应用指令本身以发出从主机71的存储器70加载应用数据的读请求。特别地,次级引导加载器指令可以用于发出加载不变应用数据的一部分(例如,用于机器学习模型的超参数)的读请求,而应用指令可以被用于发出加载数据的可变部分(例如,用于机器学习模型的训练数据)的读请求。

在应用的运行时期间,如果在处理单元2上运行的应用失败并且需要从某个点重启,那么可能期望对可以读回到芯块4中的某些数据进行检查点设定。次级引导加载器可以被用于加载检查点数据。

当应用在处理单元2上运行时,保持在芯块存储器11中的应用数据中的一些被修改。保持在芯块存储器11中的应用数据被划分为可变数据和不变数据。可变数据包括在应用的运行时期间被修改的变量,诸如神经网络的权重。不变数据包括在应用的运行时期间不改变的数据,诸如定义神经网络中哪些节点连接的数据。

为了执行应用的检查点,芯块的组在发出将数据写入系统51的写入之前以类似于图7中所示的方式发出同步请求。处理单元2的芯块4发出包含在执行期间生成的可变数据的写入。

参考图9,其图示了由集成电路51的芯块4将检查点数据写入到系统71可访问的存储器70。写入91包括由芯块4发出的一个或多个数据分组91。一个或多个数据分组91包含要写入存储装置710的检查点数据。写入被提供给系统71。系统71的至少一个处理器711使检查点数据被写入存储装置710。检查点数据被识别为与从其接收到写入的芯块4相关联。集成电路51的其他芯块4将同样提供它们的可变数据的写入,这些可变数据被写入存储装置710。

稍后,当集成电路51的芯块4要求加载检查点数据时(例如,由于运行应用失败),次级引导加载器由自动加载器加载到那些芯块4,如上文关于图5A/5B所讨论的。如所讨论的,芯块存储器的剩余区域被擦除。芯块4然后发出同步请求,这些请求被聚合并提供给系统71。响应于同步请求的接收,系统71使应用数据从存储装置710加载到存储器70。与最初起动应用时不同,在这种情况下,从存储装置710加载应用数据包括加载由芯块4写入的检查点数据。加载到存储器70中的应用数据包括检查点数据,这是由芯块4写到存储装置710的可变数据,并且附加地包括先前加载的不变数据。系统71使应用数据以与用于加载到存储器70中的初始应用数据相同的布局布置在存储器70中。因此,由芯块4用来加载初始应用数据的相同的次级引导加载器也可以被用于加载应用数据,包括检查点数据。在一些情况下,如果需要,那么用于加载检查点设定的应用数据的次级引导加载器可以不同于用于初始加载应用指令的次级引导加载器。

一旦系统71已经将包括检查点数据的应用数据加载到存储器70中,系统71就发送确认,该确认被发送到发出同步请求的芯块4。然后芯块4向存储器70发出读请求,以从存储器70读取包括检查点数据的应用数据。包括检查点数据的应用数据的这种读取使用与上面关于图8讨论的应用指令的初始读取相同的机制来执行。一旦芯块4已经读入包括检查点数据的数据,它们就再次从取得检查点的点开始执行应用。

应该认识到的是,仅通过示例的方式描述了上述实施例。

权利要求书(按照条约第19条的修改)

1.一种包括多个处理器的集成电路,所述多个处理器中的每个处理器包括:

至少一个存储器,用于存储应用数据和可执行应用指令的集合;以及

至少一个执行单元,

其中所述集成电路包括硬件模块,所述硬件模块包括包含可执行引导指令的集合的存储器,其中所述硬件模块包括处理电路,所述处理电路在运行时由受信任的软件配置为使得可执行引导指令的集合经由所述集成电路的互连而被分派到所述多个处理器中的至少一些处理器,

其中对于所述多个处理器中的至少一些处理器中的每个处理器,相应的至少一个执行单元被配置为:

执行接收到的可执行引导指令的集合以使得读请求被发出到所述集成电路外部的至少一个存储器,以获取可执行应用指令的集合;以及

执行可执行应用指令的集合以使用所述应用数据执行操作。

2.如权利要求1所述的集成电路,其中对于所述多个处理器中的至少一些处理器中的每个处理器:

执行接收到的可执行引导指令的集合包括根据所述集成电路中相应的处理器的标识符计算外部存储器的地址,

使得读请求被发出包括使得读请求被发出以从外部存储器中的计算出的地址获取可执行应用指令的集合。

3.如前述权利要求中的任一项所述的集成电路,其中所述硬件模块包括处理电路,所述处理电路被配置为使得一个或多个写请求被分派到所述多个处理器中的至少一些处理器中的每个处理器,以使得未被可执行引导指令的集合占用的存储器空间被清除。

4.如前述权利要求中的任一项所述的集成电路,其中对于所述多个处理器中的至少一些处理器中的每个处理器:

所述相应的至少一个执行单元被布置为使得在相应的可执行指令的集合的执行期间生成的检查点数据在写请求中被分派到所述集成电路外部的存储装置。

5.如权利要求4所述的集成电路,其中所述硬件模块的处理电路被配置为,在使得生成的检查点数据被分派之后,使得可执行引导指令的集合再次经由所述集成电路的互连而被分派到所述多个处理器中的至少一些处理器,

其中对于所述多个处理器中的至少一些处理器中的每个处理器,所述相应的至少一个执行单元被配置为随后:

执行接收到的可执行引导指令的集合以使得读请求被发出到所述集成电路外部的存储器,以获取可执行应用指令的集合和包括所述检查点数据的应用数据的另一个集合;以及

执行可执行应用指令的集合以使用所述检查点数据的值来执行操作。

6.如权利要求5所述的集成电路,其中应用数据的所述另一个集合包括不变数据的集合,其中所述不变数据是在分派所述检查点数据之前获取的所述应用数据的一部分,

其中应用数据的所述另一个集合包括代替可变数据的检查点数据,其中所述可变数据是在分派所述检查点数据之前获取的所述应用数据的一部分。

7.如前述权利要求中的任一项所述的集成电路,其中对于所述多个处理器中的至少一些处理器中的每个处理器,所述相应的至少一个执行单元被配置为执行可执行应用指令的相应集合以从所述集成电路外部的所述至少一个存储器加载所述应用数据的至少一部分。

8.如前述权利要求中的任一项所述的集成电路,其中对于所述多个处理器中的至少一些处理器中的每个处理器,所述相应的至少一个执行单元被配置为执行接收到的可执行引导指令的集合以使得读请求被发出到所述集成电路外部的至少一个存储器,以获取所述应用数据的至少一部分。

9.如前述权利要求中的任一项所述的集成电路,其中所述硬件模块包括被配置为存储可执行引导指令的集合的易失性存储器,其中所述硬件模块的处理电路被配置为,在所述集成电路的重置之后:

从所述集成电路外部的设备接收可执行引导指令的集合;以及

将接收到的可执行引导指令的集合存储在所述易失性存储器中。

10.如权利要求9所述的集成电路,其中从所述集成电路外部的设备接收可执行引导指令的集合包括经由JTAG接口接收可执行引导指令的集合。

11.如权利要求1至7中的任一项所述的集成电路,其中所述硬件模块包括被配置为存储可执行引导指令的集合的非易失性存储器。

12.如前述权利要求中的任一项所述的集成电路,其中所述硬件模块的存储器被配置为存储可执行引导指令的多个集合,其中所述处理电路被配置为使得可执行引导指令的所述多个集合中的每个集合被分派到所述集成电路的处理器的子集。

13.一种数据处理系统,包括:

如前述权利要求中的任一项所述的集成电路;以及

数据提供系统,其包括所述集成电路外部的存储器。

14.如权利要求13所述的数据处理系统,其中所述数据提供系统包括至少一个处理器,所述处理器被配置为响应于在数据提供系统处接收到来自所述集成电路的同步请求而使得用于一组处理器的应用数据被加载到所述集成电路外部的存储器中。

15.如权利要求13所述的数据处理系统,其中所述数据提供系统的所述至少一个处理器被配置为根据从所述集成电路接收到的该组处理器的标识符而将所述应用数据布置在所述集成电路外部的存储器中。

16.一种在包括多个处理器的集成电路中实现的方法,所述方法包括:

在所述集成电路的硬件模块中存储可执行引导指令的集合,

在运行时由受信任的软件将所述硬件模块的处理电路配置为使得可执行引导指令的集合经由所述集成电路的互连而被分派到所述多个处理器中的至少一些处理器;

在所述多个处理器中的至少一些处理器中的每个处理器上,执行接收到的可执行引导指令的集合以使得读请求被发出到所述集成电路外部的存储器,以获取可执行应用指令的集合;以及

执行可执行应用指令的集合以使用应用数据执行操作。

17.一种包括计算机可执行指令的计算机程序,所述计算机可执行指令在由包括多个处理器的集成电路的硬件模块的处理电路执行时使得一方法被执行,所述方法包括:

在所述集成电路的硬件模块中存储可执行引导指令的集合,以及

在运行时由受信任的软件将所述硬件模块的处理电路配置为使得可执行引导指令的集合经由所述集成电路的互连而被分派到所述多个处理器中的至少一些处理器,

其中可执行引导指令被配置为,当在所述多个处理器中的至少一些处理器中的每个处理器上被执行时,使得读请求被发出到所述集成电路外部的存储器,以获取可执行应用指令的集合,以供在所述多个处理器中的至少一些处理器中的每个处理器上执行,以使用应用数据执行操作。

- 一种快速气液复合自动补偿加载的方法及自动补偿加载器

- 一种快速气液复合自动补偿加载的方法及自动补偿加载器