半导体器件

文献发布时间:2023-06-19 09:32:16

技术领域

本申请涉及半导体领域,具体地,涉及一种半导体器件。

背景技术

在诸如手机和无线系统的无线电传输装置中,其天线开关是用于通过传输路径路由高频信号的重要部件。天线开关通常与功率放大器结合,并且两个功能都集成在同一集成电路中。在一些方式中,所传输的信号通过衬底从一个节点连接至另一个节点。可以将易受衬底噪声耦合影响的衬底描述为具有低插入损耗,其中插入损耗是传输信号的减小。在用于混合信号和片上系统(SOC)设计的低噪声电路中,迹线插入损耗对于半导体器件的设计和制造变得更具挑战性。

发明内容

在一些实施例中,本申请公开了一种半导体器件,包括:衬底;金属氧化物半导体器件,设置在衬底中;以及部件,设置成邻近金属氧化物半导体器件。所述部件以第一深度延伸至衬底中,金属氧化物半导体器件以小于第一深度的第二深度延伸至衬底中。

本申请还公开了一种半导体器件,包括:衬底;第一阱至第三阱,设置在衬底中;第一掺杂区和第二掺杂区,设置在位于第一阱之上的第四阱中,其中第二阱插入第三阱和第四阱之间;以及第三掺杂区,设置在第三阱中。第三掺杂区构造成浮置。

本申请还公开了一种半导体器件,包括:衬底,包括非掺杂区;金属氧化物半导体器件,延伸至衬底中,其中金属氧化物半导体器件邻近非掺杂区;以及至少一个电阻器,设置在非掺杂区的正上方,并且布置成沿着一定的方向与金属氧化物半导体器件排列成一排。

本申请的实施例公开了用于低损耗天线开关的半导体器件。

附图说明

当结合附图进行阅读时,从以下详细描述可最佳理解本发明的各个方面。应该指出,根据工业中的标准实践,各个部件未按比例绘制。实际上,为了清楚的讨论,各个部件的尺寸可以任意地增大或减小。

图1是根据一些实施例的半导体器件的一部分的俯视图;

图2是根据一些实施例的半导体器件的一部分的俯视图;

图3是根据一些实施例的半导体器件的一部分的俯视图;

图4是根据一些实施例的半导体器件的一部分的截面图;

图5是根据一些实施例的图4中的半导体器件的一部分的俯视图;

图6是根据一些实施例的图5中的半导体器件的一部分的截面图;

图7是根据一些实施例的与图5中的半导体器件相对应的半导体器件的一部分的截面图;

图8是根据一些实施例的与图5中的半导体器件相对应的半导体器件的一部分的截面图;

图9是根据一些实施例的半导体器件的一部分的截面图;

图10是根据一些实施例的半导体器件的一部分的截面图;

图11是根据一些实施例的半导体器件的一部分的俯视图;

图12是根据一些实施例的半导体器件的一部分的俯视图;

图13是根据本发明的一些实施例的制造半导体器件的方法的流程图;

图14是根据本发明的一些实施例的用于设计集成电路布局设计的系统的框图;

图15是根据一些实施例的集成电路制造系统以及与其相关的集成电路制造流程的框图。

具体实施方式

以下公开内容提供了许多用于实现本发明的不同特征的不同实施例或实例。下面描述了组件和布置的具体实例以简化本发明。当然,这些仅仅是实例,而不旨在限制本发明。例如,以下描述中,在第二部件上方或者上形成第一部件可以包括第一部件和第二部件直接接触形成的实施例,并且也可以包括在第一部件和第二部件之间可以形成额外的部件,从而使得第一部件和第二部件可以不直接接触的实施例。另外,本发明可以在各种实例中重复参考数字和/或字母。该重复是出于简化和清楚的目的,其本身并不指示所讨论的各种实施例和/或结构之间的关系。

在本说明书中使用的术语通常具有本领域和在使用每个术语的特定上下文中的普通含义。在本说明书中示例的使用,包括在此讨论的任何术语的示例,仅是说明性的,绝不限制本公开或者任何示例性术语的范围和含义。同样,本公开不限于本说明书中给出的各种实施例。

如本文所使用的术语“包括”、“包括”、“具有”、“包含”、“涉及”等应理解为开放式的,即意指包括但不限于。

在整个说明书中对“一个实施例”、“实施例”或者“一些实施例”的引用意指结合(一些)实施例描述的特定特征、结构、实施、或者特性包括在本发明的至少一个实施例中。因此,在整个说明书中的各个地方使用短语“在一个实施例中”或者“在实施例中”或者“在一些实施例中”不一定全部指的是同一实施例。另外,可以以任何合适的方式在一个或者多个实施例中对特定的特征、结构、实施、或者特性进行组合。

而且,为便于描述,在此可以使用诸如“在…之下”、“在…下方”、“下部”、“在…之上”、“上部”等空间相对术语,以容易地描述如图所示的一个元件或部件与另一个(或另一些)元件或部件的关系。除了图中所示的方位外,空间相对术语旨在包括器件在使用或操作中的不同方位。装置可以以其他方式定向(旋转90度或在其他方位上),而本文使用的空间相对描述符可以同样地作出相应的解释。如本文所使用的术语“和/或”包括一个或者多个相关的所列条目的任何和所有组合。

如本文所使用的“大约”、“约”、“近似”或者“基本上”通常是指给定的值或者范围的任何近似值,其中该给定的值或者范围的近似值根据其所属领域的不同而变化,并且其范围应与本领域技术人员所理解的最广泛的解释相一致,因而包括所有如此的修改和类似的结构。在一些实施例中,其通常意指给定的值或者范围的百分之二十以内,优选为百分之十以内,更优选为百分之五以内。这里给出的数值量是近似的,意味着如果没有明确说明或者意味着其他近似值,则可以对术语“大约”、“约”、“近似”或者“基本上”进行推断。

在一些实施例中,本发明提供了一些实施,用以在不改变天线开关的电路设计的情况下减小天线开关的插入损耗(IL)。在一些实施例中,隔离件设置成在衬底上邻近金属氧化物半导体(MOS)器件。换句话说,将较少的类金属元件设置成邻近接收和发送信号的器件,可以进一步改善IL性能。在一个实施例中,未植入的半导体结构布置成邻近MOS。在另一个实施例中,诸如伪栅极或者伪有源区的半导体结构布置成邻近MOS。在硅化物形成工艺之前,在半导体结构之上形成抗蚀剂保护氧化物(RPO)层,以防止RPO层下面的结构发生硅化。在又一个实施例中,与衬底相对应的MOS的一个端子设置成浮置或者连接至电阻器。在又一个实施例中,多个MOS以预定间隔彼此间隔开。连接至MOS的电阻器具有预定的宽度,并且电阻器以另一预定的间隔彼此间隔开。在又一个实施例中,衬底包括非掺杂区。(一些)电阻器设置在非掺杂区之上的金属层中。在又一个实施例中,浅沟槽隔离件和MOS延伸至衬底中,而浅沟槽隔离件的深度大于MOS的深度。在又一个实施例中,衬底具有高电阻率。在另一个实施例中,MOS在其栅极结构之间具有增大的间距,并且构造成MOS的漏极/源极端子的导电段具有增大的宽度。

每个上述的实施例可以在不改变天线开关的电路设计的情况下,基于工艺技术来改善天线开关的IL性能。可以独立地或者以任何组合来应用上述实施例。其提高了IL性能,却不会产生任何额外的成本或者任何额外的工艺复杂性或者芯片面积损失。本发明适用于用于天线开关的任何半导体工艺技术,包括但不限于鳍式场效应晶体管(FinFET),该鳍式场效应晶体管是用于28GHz5G蜂窝网络的下一个技术。

现在参考图1。图1是根据一些实施例的半导体器件100的一部分的俯视图。在一些实施例中,半导体器件100形成为用作天线开关。为了进行说明,半导体器件100包括衬底110、金属氧化物半导体器件(MOS)120、和邻近MOS120设置的部件130。在一些实施例中,部件130的电导率小于衬底110的电导率。在各种实施例中,部件130以第一深度延伸至衬底110中,并且金属氧化物半导体器件120以小于第一深度的第二深度延伸至衬底110中。

在一些实施例中,衬底110是纯硅结构。在各种实施例中,衬底110包括其他元素半导体,例如锗。衬底110包括化合物半导体,例如碳化硅、砷化镓、砷化铟、和磷化铟。衬底110的各种实施包括在本发明的预期范围内。例如,在一些实施例中,衬底110包括合金半导体,例如硅锗、碳化硅锗、磷化砷化镓、和磷化铟镓。

现在参考图2。图2是根据一些实施例的与图1的半导体器件100相对应的半导体器件200的一部分的俯视图。为了便于理解,对应于图1的实施例,用相同的附图标记标注图2中相同的元件。

如图2所示。为了进行说明,半导体器件200在衬底110上包括多个伪结构230。在一些实施例中,伪结构230构造成对应于例如图1的部件130。伪结构230布置成与MOS间隔开距离S1。在一些实施例中,距离S1在约1微米至约100微米的范围内。

在一些实施例中,伪结构230包括例如纯硅结构。伪结构230沿着y方向以阵列的形式布置。在一些实施例中,伪结构230成对地放置,如图2所示。例如,与另一对中的另外两个伪结构230相比,一对中的两个伪结构230彼此更靠近。

在一些方式中,一些伪结构设置成邻近MOS,用以在MOS上进行进一步的化学机械抛光(CMP)工艺。然而,那些伪结构是P型掺杂的或/和N型掺杂的,并且通过自动放置实用程序来布置。在这样的布置中,基于一些实验结果,具有掺杂的伪结构的天线开关引起约1.00dB的插入损耗(IL)。利用图2所示的本发明的构造,半导体器件200将IL减小至约0.97dB。因此,与某些方式中的天线开关相比,IL性能提高了约0.03ddB。

出于说明目的给出了图2的构造。各种实施都在本发明的预期范围内。例如,在一些实施例中,伪结构230布置成沿着x方向邻近MOS120,并且与MOS120间隔开距离S1。在各种实施例中,所有伪结构230沿着x方向和y方向都通过均匀的间隔彼此间隔开。

现在参考图3。图3是根据一些实施例的与图1的半导体器件100相对应的半导体器件300的一部分的俯视图。为了便于理解,对应于图1至图2的实施例,用相同的附图标记标注图3中相同的元件。

如图3示意性地所示,包括两个部分330a-330b的抗蚀剂保护氧化物(RPO)层形成在伪结构230上方。在一些实施例中,在图3的实施例中的伪结构230和抗蚀剂保护氧化物(RPO)层的部分330a-330b构造成对应于例如图1的部件130。部分330a沿着y方向与MOS120间隔开距离S2。部分330b沿着x方向与MOS120间隔开距离S3。在一些实施例中,距离S2-S3相同。在一些可替代的实施例中,距离S2-S3不同。在又一可替代的实施例中,距离S2-S3在约1微米至约100微米的范围内。

在一些实施例中,由RPO层的部分330a-330b覆盖的区域和结构在该工艺中未硅化。换句话说,半导体器件300的区域划分为用于电接触的需要硅化的区域和不需要硅化的其他区域。因此,在RPO层的部分330a下面的伪结构230未硅化。在一些实施例中,RPO层的部分330a-330b使用二氧化硅形成。

在一些方式中,一些伪结构设置成邻近硅化的MOS,并且还具有在其上设置的导电特征。在这样的布置中,基于一些实验结果,具有硅化的伪结构的天线开关引起大约1.1dB的插入损耗(IL)。相比之下,利用图3所示的本发明的构造,半导体器件300将IL减小至约1.0dB。因此,与某种方式的天线开关相比,IL性能提高了约0.1dB。

出于说明目的给出了图3的构造。各种实施都在本发明的预期范围内。例如,在一些实施例中,在RPO层的部分330b下面布置有伪结构230。

现在参考图4。图4是根据一些实施例的与图1的半导体器件100相对应的半导体器件400的一部分的截面图。

为了进行说明,半导体器件400包括衬底410、阱421-425、浅沟槽隔离件STI、掺杂区431-437、栅极氧化物层440、栅极结构450、和电阻器R1-R2。在一些实施例中,衬底410构造成对应于例如图1的衬底110。电阻器R1-R2构造成对应于例如图1的部件130。

如图4所示,阱421布置在衬底410之上并且延伸至衬底410中。阱422和424-425布置在衬底410之上。阱423布置在阱421之上。阱424还插入在阱423和425之间。在一些实施例中,阱421是深N掺杂阱(N阱),其中深N阱表示位于表面阱423下方的导电的亚表面阱层。阱422和424是N掺杂阱。阱423和425是P掺杂阱(P阱)。

掺杂区431设置在阱422中。掺杂区432-435设置在阱423中。掺杂区436设置在阱424中。掺杂区437设置在阱425中。掺杂区431-437通过浅沟槽隔离件STI间隔开。在一些实施例中,掺杂区431、433-434、和436为N掺杂。掺杂区432、435、和437为P掺杂。

如图4所示,栅极450设置在栅极氧化物层440之上。在一些实施例中,栅极450形成为多晶硅(或者多晶硅)层。在一些实施例中,栅极450还包括栅极介电层(未示出)和金属栅极层(未示出)。在一些实施例中,栅极450包括一个或者多个金属层代替多晶硅层。在各种实施例中,栅极氧化物层440包括介电材料,该介电材料包括例如氧化硅(SiO

在一些实施例中,掺杂区433-435、栅极氧化物层440、和栅极450包括在晶体管M1中。在一些实施例中,晶体管M1构造成对应于例如图1的MOS120。掺杂区433-435分别构造成晶体管M1的漏极端子T1、源极端子T3、和体端子T4的形式。栅极450与晶体管M1的栅极端子T2相对应。在一些实施例中,掺杂区436构造成与阱421和424相对应的端子T5的形式,掺杂区437构造成与衬底410相对应的端子T6的形式。换句话说,MOS器件包括工作中的六个端子T1-T6。

在一些实施例中,栅极端子T2、端子T4-T6、或其组合构造成电连接至(一些)电阻器或者浮置。例如,在图4的实施例中,漏极端子T1和源极端子T3连接至地。栅极端子T2连接至信号,即电压VDD。体端子T4连接至电阻器R1,并且进一步连接至地。端子T5连接至电阻器R2并且进一步连接至地。在一些实施例中,端子T6浮置。在各种实施例中,端子T6连接至构造成对应于例如电阻器R1-R2的电阻器。在一些实施例中,电阻器R1-R2具有约500ohms至约1,000,000ohms的电阻。换句话说,电阻器R1-R2是具有足够高的值以有效地使衬底浮置的电阻器。

在一些方式中,由于与端子T4-T6相对应的端子中的至少一个连接至地,因此衬底噪声耦合降低了半导体器件的性能。例如,当端子T6接地时,应该在漏极至源极之间传输的信号的一部分从阱423-425流至掺杂区437,信号的另一部分从阱423、421、阱424-425流至掺杂区437,信号的另外部分从阱423、421、衬底410、和阱425流至掺杂区437。相比之下,利用图4的构造,基于一些实验结果,与某些方式中的天线开关相比,具有端子T6浮置或者连接至电阻器的天线开关将IL降低了约1.0dB。另外,当端子T5-T6都浮置或者连接至电阻器时,相对于仅端子T6浮置,可以将IL进一步减小约1.0dB。另外,当端子T4-T6全部浮置或者连接至电阻器时,相对于端子T5-T6浮置,可以将IL进一步减小约1.0dB。因此,与某些方式中的天线开关相比,IL性能大大提高。

出于说明目的给出了图4的构造。各种实施都在本发明的预期范围内。例如,在一些实施例中,阱421-422和424是P掺杂阱。阱423和425是N掺杂阱。掺杂区431、433-434、和436为P掺杂。掺杂区432、435、和437为N掺杂。

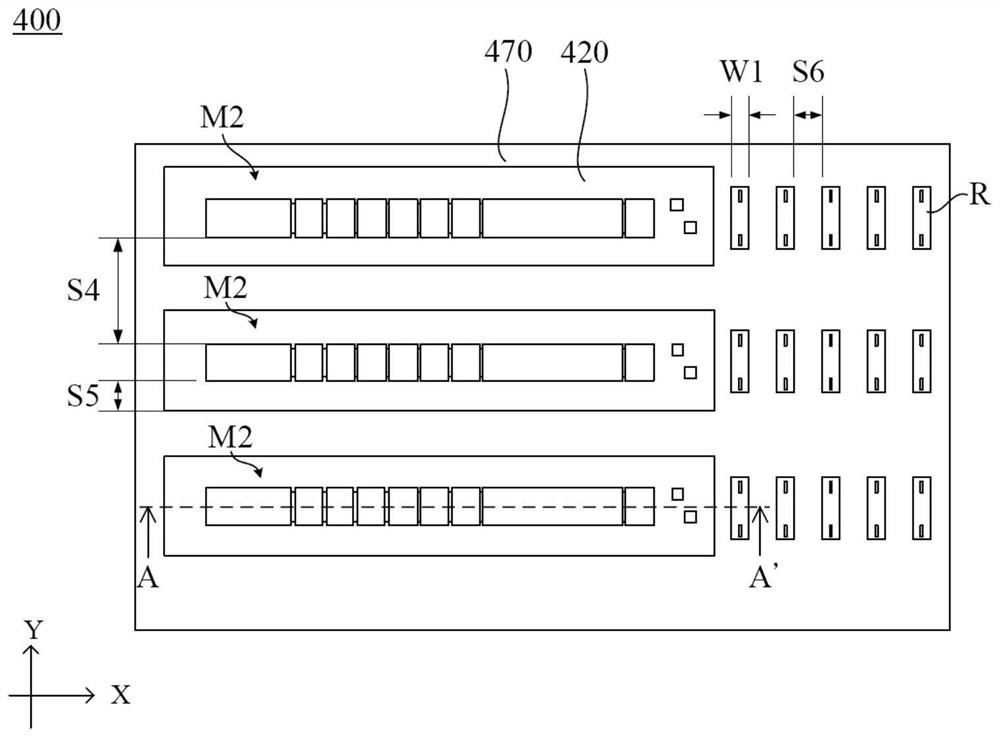

现在参考图5。图5是根据一些实施例的图4的半导体器件400的一部分的俯视图。为了便于理解,对应于图4的实施例,用相同的附图标记标注图5中相同的元件。

如图5所示,为了进行说明,半导体器件400还包括阱420、非掺杂区470、电阻器R、和晶体管M2。在一些实施例中,阱420构造成对应于例如图4的阱421-425。非掺杂区470与图4的衬底410的区域相对应。电阻器R构造成对应于例如图4的电阻器R1-R2。晶体管M2构造成对应于例如具有图4的六个端子的晶体管M1。在各种实施例中,通过并联连接多个晶体管M1来实施一个晶体管M2。

为了进行说明,晶体管M2设置在沿着x方向延伸的阱420中。在布局图中,晶体管M2彼此间隔开距离S4。在一些实施例中,距离S4在约0.001微米至约5微米的范围内。在一些实施例中,每个晶体管M2沿着y方向具有约1.5微米的MOS高度。

如图5所示,在布局图中,用非掺杂区470围绕阱420。晶体管M2与非掺杂区470间隔开距离S5。在一些实施例中,距离S5为约1微米,但是本发明不限于此。在一些实施例中,非掺杂区470称为衬底410中的非掺杂Si(NTN)区。非掺杂区470的细节将在图6中以截面图进行讨论。

电阻器R布置在非掺杂区470之上。如上所述,非掺杂区470与衬底410中的非掺杂区相对应。换句话说,在电阻器R下面没有布置P阱或者N阱。因此,在上述实施例中,由于衬底410的掺杂区与电阻器R之间由非掺杂区提供的距离,使得衬底噪声耦合对电阻器R的影响减小。IL相应地得到改善。

为了进行说明,一排中的电阻器R沿着x方向与晶体管M2对准。如图5所示,电阻器R在沿着x方向彼此间隔开距离S6,并且每个电阻器R具有宽度W1。在一些实施例中,距离S6在约0.001微米至约10微米的范围内。宽度W1在约0.001微米至约10微米的范围内。

在一些方式中,与本发明中的电阻器相比,具有更宽宽度的电阻器要承受衬底噪声耦合。相比之下,利用图5的本发明的构造,电阻器具有减小的宽度和彼此之间更靠近的间隔。因此,减小了由于衬底和电阻器之间的寄生电容引起的插入损耗。IL相应地得到改善。例如,一些实验结果,当天线开关中的电阻器的宽度从约0.36微米变为约0.06微米时,引起IL下降约0.2dB。

出于说明目的给出了图5的构造。各种实施都在本发明的预期范围内。例如,在一些实施例中,电阻器R布置在晶体管M2的两个相对侧上。

现在参考图6。图6是根据一些实施例的沿着图5中的线A-A'的半导体器件400的一部分的截面图。为了便于理解,对应于图4-图5的实施例,用相同的附图标记标注图6中相同的元件。

为了进行说明,半导体器件400还包括多个厚金属层M1-M4、M(top-1)、和Mtop、以及隔离件480。在一些实施例中,在金属层M4和M(top-1)之间存在更多的金属层。金属层M1-M4、M(top-1)、和Mtop构造成用于在半导体器件400中包括的器件之间进行金属布线。在可替代的实施例中,隔离件480例如通过浅沟槽隔离件或者伪有源区来实施,并且构造成对应于例如图1的部件130。

如图6所示,金属层M1-M4、M(top-1)、和Mtop沿着z方向布置在晶体管M2和隔离件480之上。电阻器R布置在金属层的位置中。在一些实施例中,电阻器R布置在金属层的至少一层之上。换句话说,如图6所示,电阻器R布置在线路的后端(BEOL)部分中,其中BEOL是IC制造工艺的最后部分,其中单个器件(晶体管、电容器、电阻器等)与通孔和例如金属层M1-M4、M(top-1)、和Mtop的导电迹线互连。

为了进行说明,非掺杂区470布置在隔离件480下方。如上所述,在一些实施例中,非掺杂区470是衬底410的非掺杂硅区,包括半导体材料,例如硅,其的阻抗要高于非本征半导体(例如在衬底410的其他区域中的p型半导体或者n型半导体)的阻抗。因此,与在隔离件480、电阻器R和围绕晶体管M2下面具有p型阱或者n型阱的天线开关相比,图6中的半导体器件400具有较高的衬底阻抗,这使得减小了晶体管M2的寄生损耗。这减少了穿过衬底410的RF泄漏的量,继而提高了半导体器件400的IL性能。

出于说明目的给出了图6的构造。各种实施都在本发明的预期范围内。例如,在一些实施例中,另一对隔离件480和非掺杂区470布置在图6中的晶体管M2的两个相对侧上。

现在参考图7。图7是根据一些实施例的与图5的半导体器件相对应的半导体器件700的一部分的截面图。为了便于理解,对应于图4-图6的实施例,用相同的附图标记标注图7中相同的元件。

与图6相比,图7中的隔离件480和非掺杂区470布置在晶体管M2的两个相对侧上并且邻近晶体管M2。电阻器R进一步设置在晶体管M2的两个相对侧上的非掺杂区470之上。

出于说明目的给出了图7的构造。各种实施都在本发明的预期范围内。例如,在一些实施例中,电阻器R布置在金属层M2的位置中。

图8是根据各种实施例的与图5的半导体器件相对应的半导体器件800的一部分的截面图。为了便于理解,对应于图4-图7的实施例,用相同的附图标记标注图8中相同的元件。

与图7相比,半导体器件800中的电阻器R布置在隔离件480和金属层M1之间。在一些实施例中,电阻器R设置在线路的中间端(MEOL)部分中,其中MEOL在器件的栅极和源极/漏极区之间提供接触(包括共享接触)。

现在参考图9。图9是根据一些实施例的与图1的半导体器件100相对应的半导体器件900的一部分的截面图。为了进行说明,半导体器件900包括衬底910、MOS920、和部件931-932。在一些实施例中,衬底910构造成对应于例如图1的衬底110。MOS920构造成对应于例如图1的MOS120。部件931-932构造成对应于例如图1的部件130。

为了进行说明,MOS920和部件931-932沿着z方向延伸至衬底910中,并且部件931-932设置在MOS920的相对侧。在一些实施例中,部件931-932包括浅沟槽隔离件。如图9所示,部件931-932以深度D1延伸至衬底910中,并且MOS920以深度D2延伸至衬底910中。在一些实施例中,深度D1大于深度D2。在各种实施例中,深度D1-D2在约0.5微米至约10微米的范围内。

出于说明目的给出了图9的构造。各种实施都在本发明的预期范围内。例如,在一些实施例中,部件931-932的深度由于实际设计而不同。

现在参考图10。图10是根据一些实施例的与图1的半导体器件100相对应的半导体器件1000的一部分的截面图。为了便于理解,对应于图9的实施例,用相同的附图标记标注图10中相同的元件。

与图9相比,深度D1小于深度D2。在一些实施例中,衬底910进一步具有范围从约100ohm-cm至约1,000,000ohm-cm的高电阻率。在一些实施例中,衬底910包括具有低掺杂浓度(例如,掺杂浓度小于10

在一些实施例中,由源极、漏极和沟道至衬底的电容引起的IL根据衬底电阻的有效值而变化,其中IL随着衬底电阻的增加而减小。衬底电阻取决于衬底的电阻率和布局。因此,与包括具有低电阻率衬底的天线开关的一些方式相比,具有图10的构造的天线开关将IL降低约0.5dB。

出于说明目的给出了图10的构造。各种实施都在本发明的预期范围内。例如,在一些实施例中,衬底910还包括如图8所示的区域470,以进一步改善半导体器件1000的IL性能。

现在参考图11。图11是根据一些实施例的与图1的半导体器件100相对应的半导体器件1100的一部分的俯视图。为了便于理解,对应于图4的实施例,用相同的附图标记标注图11中相同的元件。

与图4相比,可以替代具有电阻器R和晶体管M2的是,半导体器件1100包括晶体管M3。在一些实施例中,晶体管M2-M3的构造不同。在各种实施例中,晶体管M2-M3的构造相同。在各种实施例中,一个晶体管M3是并联连接在一起的30多个重复的MOSM3的结合。

为了进行说明,晶体管M3具有例如约1.5微米的MOS高度。如上所述,距离S4在约0.001微米至约5微米的范围内。

在一些方式中,由于深n阱规则,使得MOS之间的距离为约5微米。利用本发明的构造,可以在不改变天线开关的电路设计的情况下,基于处理技术缩短MOS之间的距离来改善天线开关的IL性能。

出于说明目的给出了图11的构造。各种实施都在本发明的预期范围内。例如,在一些实施例中,MOS的数量构造成相对于晶体管M3为多于三个。

现在参考图12。图12是根据一些实施例的与图1的半导体器件100相对应的半导体器件1200的一部分的俯视图。为了进行说明,半导体器件1200包括晶体管M4中的衬底1210、掺杂区1220、栅极1230、和导电段(金属至器件,MD)1240。在一些实施例中,衬底1210构造成对应于例如图1的衬底110。晶体管M4构造成对应于例如图1的MOS120。

如图12所示,掺杂区1220在衬底1210上沿着x方向延伸。栅极1230沿着y方向延伸,并且沿着x方向彼此间隔开栅极间距P。具有宽度W2的导电段1240沿着y方向延伸,并且插入栅极1230之间。在一些实施例中,栅极间距P在约100纳米至约220纳米的范围内。宽度W2约为40纳米。

利用图12的构造,由于增大的栅极间距,使得MOS的迁移率得到提高,并且减小了栅极之间产生的寄生电容。因此,包括在半导体器件1200中的天线开关的IL和隔离件均得到改善。例如,基于实验结果,天线开关的IL随着其栅极间距从约90纳米增大到130纳米而减小约1.0dB。另外,具有增大的导电段宽度也有助于IL的改善。例如,基于实验结果,天线开关的IL随着其导电段的宽度从约24纳米增大到约40纳米而减小约0.03dB。在本发明的一些实施例中,随着栅极间距增大约原始设计的30%,而使得天线开关的IL表现出显著的改善。

出于说明目的给出了图12的构造。各种实施都在本发明的预期范围内。例如,在一些实施例中,掺杂区1220实施为间隔开的掺杂区。

现在参考图13。图13是根据本发明的一些实施例的制造半导体器件100、200、300、400、700、800、900、1000、1100或者1200的方法1300的流程图。应该理解,可以在图13所示的工艺之前、之中、和之后提供附加的操作,并且对于方法1300的另外的实施例,可以对下面描述的一些操作进行替换或者删除。方法1300包括操作1301-1307。图13所示的操作顺序可以根据本发明的不同实施例进行变化。

在操作1301中,形成延伸至衬底中的至少一个MOS,如例如图6至图10的实施例所示。在一些实施例中,至少一个MOS的栅极具有增大的间距,并且至少一个MOS的导电段具有预定的宽度,如例如图12的实施例所示。

在操作1302中,形成延伸至衬底中的至少一个浅沟槽隔离件,如例如图6至图10的实施例所示。

在操作1303中,形成邻近衬底上的至少一个MOS器件的多个半导体结构,如例如图2至图3的实施例所示。

在操作1304中,形成半导体结构上方的抗蚀剂保护氧化物层,如例如图3的实施例所示。

在操作1305中,形成至少一个MOS器件的彼此间隔开预定间隔的多个MOS,如例如图5和图11的实施例所示。

在操作1306中,形成连接至至少一个MOS的至少一个端子的至少一个电阻器,如例如图4的实施例所示。

在操作1307中,形成至少一个邻近MOS的电阻器的多个电阻器,如例如图5的实施例所示。在一些实施例中,电阻器通过预定间隔彼此隔开,如例如图5和图11的实施例所示。在各种实施例中,每个电阻器具有如例如图5的实施例所示的宽度。在各种实施例中,电阻器布置在衬底的非掺杂区之上,如例如图6至图8的实施例所示。

现在参考图14。图14是根据本发明的一些实施例的用于设计集成电路布局设计的电子设计自动化(EDA)系统1400的框图。EDA系统1400构造成实施图13中公开的方法1300的一个或者多个操作,并且结合图1至图12进一步解释。在一些实施例中,EDA系统1400包括APR系统。

在一些实施例中,EDA系统1400是通用计算设备,包括硬件处理器1402和非暂时性计算机可读存储介质1404。除其他外,存储介质1404用计算机程序代码(指令)1406(即一组可执行指令)进行编码,即存储。由硬件处理器1402执行指令1406表示实施一部分或者全部的例如方法1300的(至少一部分)EDA工具。

处理器1402经由总线1408电连接至计算机可读存储介质1404。处理器1402也通过总线1408电连接至I/O接口1410和制造工具1416。网络接口1412也是经由总线1408电连接至处理器1402。网络接口1412连接至网络1414,使得处理器1402和计算机可读存储介质1404能够经由网络1414连接至外部元件。处理器1402构造成执行在计算机可读存储介质1404中编码的计算机程序代码1406,以使得EDA系统1400可以用于实施所提到的工艺和/或方法的一部分或者全部。在一个或者多个实施例中,处理器1402是中央处理单元(CPU)、多处理器、分布式处理系统、专用集成电路(ASIC)、和/或合适的处理单元。

在一个或者多个实施例中,计算机可读存储介质1404是电、磁、光、电磁、红外、和/或半导体系统(或者装置或者设备)。例如,计算机可读存储介质1404包括半导体或者固态存储器、磁带、可移动计算机磁盘、随机存取存储器(RAM)、只读存储器(ROM)、刚性磁盘、和/或光盘。在一个或者多个使用光盘的实施例中,计算机可读存储介质1404包括光盘只读存储器(CD-ROM)、读/写光盘(CD-R/W)、和/或数字视频光盘(DVD)。

在一个或者多个实施例中,存储介质1404存储计算机程序代码1406,该计算机程序代码1406构造成使得EDA系统1400(其中这种执行(至少部分地)代表EDA工具)可以用于实施所提到的工艺和/或方法的一部分或者全部。在一个或者多个实施例中,存储介质1404还存储信息,该信息有助于实施所提到的工艺和/或方法的一部分或者全部。在一个或者多个实施例中,存储介质1404存储包括本文所公开的这种标准单元的IC布局图1420,本文所公开的这种标准单元例如是包括在上述对应于图1至图12的半导体器件100、200、300、400、700、800、900、1000、1100、1200中的单元。

EDA系统1400包括I/O接口1410。I/O接口1410连接至外部电路。在一个或者多个实施例中,I/O接口1410包括键盘、小键盘、鼠标、轨迹球、触控板、触摸屏、和/或光标方向键,用于将信息和命令传达至处理器1402。

EDA系统1400还包括连接至处理器1402的网络接口1412。网络接口1412允许EDA系统1400与网络1414通信,一个或者多个其他计算机系统连接至该网络1414。网络接口1412包括:无线网络接口,例如蓝牙、WIFI、WIMAX、GPRS、或者WCDMA;或者有线网络接口,例如ETHERNET、USB、或者IEEE-1464。在一个或者多个实施例中,在两个或者多个系统1400中实施所提到的工艺和/或方法的一部分或者全部。

EDA系统1400还包括连接至处理器1402的制造工具1416。制造工具1416构造成制造集成电路,例如如图1至图12所示的上述对应于图1至图12的半导体器件100、200、300、400、700、800、900、1000、1100、1200,根据设计文件由处理器1402处理。

EDA系统1400构造成通过I/O接口1410接收信息。通过I/O接口1410接收的信息包括指令、数据、设计规则、标准单元的库、和/或其他参数中的一个或者多个,以供处理器1402处理。经由总线1408将信息传送至处理器1402。EDA系统1400构造成通过I/O接口1410接收与UI有关的信息。该信息作为设计规范1422存储在计算机可读介质1404中。

在一些实施例中,所提到的工艺和/或方法的一部分或者全部实施为用于由处理器执行的独立软件应用。在一些实施例中,所提到的工艺和/或方法的一部分或者全部实施为作为附加软件应用的一部分的软件应用。在一些实施例中,所提到的工艺和/或方法的一部分或者全部实施为软件应用的插件。在一些实施例中,所提到的工艺和/或方法中的至少一个实施为作为EDA工具的一部分的软件应用。在一些实施例中,所提到的工艺和/或方法的一部分或者全部实施为由EDA系统1400使用的软件应用。在一些实施例中,使用合适的布局生成工具来生成包括标准单元的布局图。

在一些实施例中,这些工艺实现为存储在非暂时性计算机可读记录介质中的程序的功能。非暂时性计算机可读记录介质的示例包括但不限于外部/可移动和/或内部/内置存储或者内存单元,例如一个或者多个诸如DVD的光盘、诸如硬盘的磁盘、诸如ROM、RAM、存储卡等的半导体存储器。

图15是根据一些实施例的IC制造系统1500以及与其相关的IC制造流程的框图。在一些实施例中,基于布局图,使用IC制造系统1500制造这两者中的至少一个:(A)一个或者多个半导体掩模,(B)半导体集成电路层中的至少一个组件。

在图15中,IC制造系统1500包括在与制造IC器件1560相关的设计、开发、和制造周期和/或服务中彼此相互作用的实体,例如设计室1520、掩模室1530、和IC制造商/制造者(“fab”)1550。IC制造系统1500中的实体通过通信网络连接。在一些实施例中,通信网络是单个网络。在一些实施例中,通信网络是各种不同的网络,例如企业内部网和因特网。通信网络包括有线和/或无线通信信道。每个实体与一个或者多个其他实体进行交互,并且向一个或者多个其他实体提供服务和/或从一个或者多个其他实体接收服务。在一些实施例中,两个或者更多个设计室1520、掩模室1530和ICfab1550由单个实体拥有。在一些实施例中,两个或者更多个设计室1520、掩模室1530、和ICfab1550在公共设施中共存并且使用公共资源。

设计室(或者设计团队)1520生成IC设计布局图1522。IC设计布局图1522包括各种几何图案,例如用于IC器件1560的IC布局设计,例如图1至图12所示的上述对应于图1至图12的半导体器件100、200、300、400、700、800、900、1000、1100、1200。几何图案与构成要制造的IC器件1560的各种组件的金属、氧化物、或者半导体层的图案相对应。各种层结合形成各种IC部件。例如,IC设计布局图1522的一部分包括形成在半导体衬底(例如硅晶圆)和设置在半导体衬底上的各种材料层中的各种IC部件,例如有源区、栅电极、源极和漏极、导电段、或者层间互连的通孔。设计室1520实施适当的设计过程以形成IC设计布局图1522。设计过程包括一个或者多个逻辑设计、物理设计、或者布局和布线。IC设计布局图1522呈现在具有几何图案信息的一个或者多个数据文件中。例如,IC设计布局图1522可以以GDSII文件格式或者DFII文件格式来表达。

掩模室1530包括数据准备1532和掩模制造1544。掩模室1530使用IC设计布局图1522来制造一个或者多个掩模1545,以用作根据IC设计布局图1522来制造IC器件1560的各个层。掩模室1530实施掩模数据准备1532,其中IC设计布局图1522转换成代表性数据文件(“RDF”)。掩模数据准备1532提供RDF至掩模制造1544。掩模制造1544包括掩模写入器。掩膜写入器将RDF转换为诸如掩膜(中间掩模)1545或者半导体晶圆1553的衬底上的图像。IC设计布局图1522由掩膜数据准备1532操纵以符合掩膜写入器和/或ICfab1550的特定特性。在图15中,数据准备1532和掩模制造1544示出为单独的元件。在一些实施例中,数据准备1532和掩模制造1544可以统称为掩模数据准备。

在一些实施例中,数据准备1532包括光学接近度校正(OPC),其使用光刻增强技术来补偿图像误差,例如可能由于衍射、干涉、其他处理效果等引起的图像误差。OPC调整IC设计布局图1522。在一些实施例中,数据准备1532包括其他分辨率增强技术(RET),例如离轴照明、子分辨率辅助功能、相移掩模、其他合适的技术等、或其组合。在一些实施例中,还使用反光刻技术(ILT),其将OPC视为反成像问题。

在一些实施例中,数据准备1532包括掩模规则检查器(MRC),该掩模规则检查器使用一组掩模创建规则来检查已经在OPC中进行过处理的IC设计布局图1522,该掩模创建规则包含某些几何和/或连接性限制,以确保足够的余量,以解决半导体制造工艺中的可变性等。在一些实施例中,MRC修改IC设计布局图1522以补偿掩模制造1544期间的限制,其可以撤消由OPC实施的修改的一部分,以满足掩模创建规则。

在一些实施例中,数据准备1532包括光刻工艺检查(LPC),其仿真将由ICfab1550实施以制造IC器件1560的工艺。LPC基于IC设计布局图1522来仿真该工艺,以创建仿真的制造器件,例如IC器件1560。LPC仿真中的工艺参数可以包括与IC制造周期的各种工艺相关的参数、与用于制造IC的工具相关的参数、和/或制造工艺的其他方面。LPC考虑了各种因素,例如航空图像对比度、焦深(“DOF”)、掩模误差增强因素(“MEEF”)、其他适当的因素等、或其组合。在一些实施例中,在已经通过LPC创建了仿真的制造设备之后,如果仿真的设备在形状上不足以满足设计规则,则重复OPC和/或MRC以进一步细化IC设计布局图1522。

应当理解,为了清楚起见,已经简化了数据准备1532的以上描述。在一些实施例中,数据准备1532包括诸如逻辑操作(LOP)的附加特征,以根据制造规则来修改IC设计布局图1522。另外,可以以各种不同的顺序来执行在数据准备1532期间应用于IC设计布局图1522的工艺。

在数据准备1532之后以及在掩模制造1544期间,基于修改的IC设计布局图1522来制造掩模1545或者一组掩模1545。在一些实施例中,掩模制造1544包括基于IC设计布局图1522来实施一个或者多个光刻曝光。在一些实施例中,基于修改的IC设计布局图1522,使用电子束(e-beam)或者多个电子束的机构来在掩模(光掩模或者中间掩模)1545上形成图案。掩模1545可以以各种技术形成。在一些实施例中,使用二进制技术形成掩模1545。在一些实施例中,掩模图案包括不透明区和透明区。用于曝光已经涂覆在晶圆上的图像敏感材料层(例如光刻胶)的辐射束,例如紫外线(UV)束,由不透明区阻挡,并且透射穿过透明区。在一个实例中,掩模1545的二元掩模版本包括透明衬底(例如熔融石英)和涂覆在二元掩模的不透明区中的不透明材料(例如铬)。在另一个示例中,使用相移技术形成掩模1545。在掩模1545的相移掩模(PSM)版本中,形成在相移掩模上的图案中的各种特征构造成具有适当的相差,以增强分辨率和成像质量。在各种示例中,相移掩模可以是衰减的PSM或者交替的PSM。由掩模制造1544产生的(一些)掩模用于多种工艺中。例如,在离子注入工艺中使用这样的(一些)掩模,以在半导体晶圆1553中形成各种掺杂区;在蚀刻工艺中使用这样的(一些)掩模,以在半导体晶圆1553中形成各种蚀刻区;和/或在其他合适的工艺中使用这样的(一些)掩模。

ICfab1550包括晶圆制造1552。ICfab1550是IC制造企业,其包括一个或者多个制造设施,用于制造各种不同的IC产品。在一些实施例中,ICFab1550是半导体制造工厂。例如,可能有一个制造工厂用于多个IC产品的前端制造(线路的前端(FEOL)制造),而第二个制造工厂可以为IC产品的互连和封装提供后端制造(线路的后端(BEOL)制造),第三个制造工厂可能会为制造工厂业务提供其他服务。

ICfab1550使用由掩模室1530制造的(一些)掩模1545来制造IC器件1560。因此,ICfab1550至少间接地使用IC设计布局图1522来制造IC器件1560。在一些实施例中,半导体晶圆1553通过ICfab1550使用(一些)掩模1545来制造,以形成IC器件1560。在一些实施例中,IC制造包括至少间接基于IC设计布局图1522实施一次或者多次光刻曝光。半导体晶圆1553包括硅衬底或者在其上形成有材料层的其他合适的衬底。半导体晶圆1553进一步包含各种掺杂区、电介质部件、多层互连等的一个或者多个(在随后的制造步骤中形成)。

如上所述,通过在不改变天线开关的电路设计的情况下实施上述实施例中呈现的特征,包括在本发明提供的半导体器件中的天线开关具有改善的插入损耗和隔离件。

在一些实施例中,公开了一种半导体器件,包括:衬底;金属氧化物半导体器件,设置在衬底中;以及部件,设置成邻近金属氧化物半导体器件。所述部件以第一深度延伸至衬底中,金属氧化物半导体器件以小于第一深度的第二深度延伸至衬底中。在一些实施例中,所述部件包括:多个深浅沟槽隔离件。浅沟槽隔离件具有在约0.5微米至约10微米的范围内的第一深度。在一些实施例中,所述部件包括:两个深浅沟槽隔离件,设置在金属氧化物半导体器件的相对侧,并且具有大于约0.5微米的第一深度。在一些实施例中,半导体器件还包括:第一类型的第一阱和第二阱、以及不同于所述第一类型的第二类型的第三阱,位于所述衬底上;第二类型的第四阱,设置在第一阱之上,其中第二阱插入第三阱和第四阱之间;第二类型的第一掺杂区,设置在第二阱中;以及第一类型的第二掺杂区,设置在第三阱中;栅极结构,设置在第四阱之上;以及第三掺杂区至第五掺杂区,设置在第四阱中,其中第三掺杂区至第五掺杂区和栅极结构包括在构造成用作金属氧化物半导体器件的结构中。栅极结构、第一掺杂区、第二掺杂区、第五掺杂区、或其组合构造成电连接至所述部件,或者浮置。在一些实施例中,所述部件包括至少一个电阻器,该电阻器具有约500ohms至约1,000,000ohms的电阻。在一些实施例中,所述部件与金属氧化物半导体器件间隔开一定的距离。所述部件包括:多个半导体结构;以及抗蚀剂保护氧化物(RPO)层,设置在半导体结构上方。所述距离在约1微米至约100微米的范围内。在一些实施例中,半导体还包括:多个电阻器,布置在所述部件之上,其中,电阻器沿着一定的方向彼此间隔开,并且每个电阻器沿着所述方向具有在约0.001微米至约10微米的范围内的宽度。在一些实施例中,电阻器彼此间隔开的距离在约0.001微米至约10微米的范围内。在一些实施例中,衬底包括:非本征衬底;以及本征衬底,布置在所述部件和非本征衬底之间。本征衬底包括具有比非本征衬底的阻抗更高的阻抗的材料。半导体器件还包括:电阻器,布置在所述部件和本征衬底之上。在一些实施例中,半导体器件还包括:多个金属层,布置在所述部件之上。电阻器布置在金属层中的一个金属层中。在一些实施例中,金属氧化物半导体器件包括:多个金属氧化物半导体器件,在布局图中以一定的距离彼此间隔开。该距离在约0.001微米至约5微米的范围内。在一些实施例中,衬底具有在约100ohm-cm至约1,000,000ohm-cm的范围内的电阻率。

还公开了一种半导体器件,包括:衬底;第一阱至第三阱,设置在衬底中;第一掺杂区和第二掺杂区,设置在位于第一阱之上的第四阱中,其中第二阱插入第三阱和第四阱之间;以及第三掺杂区,设置在第三阱中。第三掺杂区构造成浮置。在一些实施例中,半导体器件包括:多个电阻器;以及第四掺杂区,设置在第一阱中;和第五掺杂区,设置在第二阱中。第四掺杂区、第五掺杂区、或其组合构造成连接至至少一个电阻器。在一些实施例中,电阻器以预定的间隔彼此间隔开。在一些实施例中,半导体还包括:多个金属层,位于衬底之上;以及至少一个电阻器,设置在至少一个金属层之上。衬底包括:非本征衬底;以及本征衬底,布置在非本征衬底和金属层之间,其中本征衬底包括具有比非本征衬底的阻抗更高的阻抗的材料。至少一个电阻器进一步设置在本征衬底之上。在一些实施例中,第一掺杂区和第二掺杂区包括在多个金属氧化物半导体器件中的每个金属氧化物半导体器件中。多个金属氧化物半导体器件彼此间隔开的距离在约0.001微米至5微米的范围内。

还公开了一种半导体器件,包括:衬底,包括非掺杂区;金属氧化物半导体器件,延伸至衬底中,其中金属氧化物半导体器件邻近非掺杂区;以及至少一个电阻器,设置在非掺杂区的正上方,并且布置成沿着一定的方向与金属氧化物半导体器件排列成一排。在一些实施例中,至少一个电阻器包括:多个电阻器,其中每个电阻器具有在约0.001微米至约10微米的范围内的宽度,并且具有约500ohms的最小电阻。在一些实施例中,金属氧化物半导体器件包括:多个栅极结构,具有在约100纳米至约220纳米的范围内的间距;以及多个导电段,具有约40纳米的宽度。

前面概述了若干实施例的特征,使得本领域的技术人员可以更好地理解本公开的各个方面。本领域的技术人员应该理解,他们可以容易地使用本公开作为用于设计或修改用于执行与本公开相同或类似的目的和/或实现相同或类似优点的其他工艺和结构的基础。本领域的技术人员还应该意识到,这种等效结构不背离本公开的精神和范围,并且可以进行各种改变、替换和变更而不背离本公开的精神和范围。

- 半导体器件用部材、以及半导体器件用部材形成液和半导体器件用部材的制造方法、以及使用该方法制造的半导体器件用部材形成液、荧光体组合物、半导体发光器件、照明装置和图像显示装置

- 半导体器件的制造方法、半导体器件的制造装置、半导体器件、半导体器件的制造程序、半导体用处理剂以及转印用部件