一种高功率密度IGZO薄膜晶体管

文献发布时间:2023-06-19 12:14:58

技术领域

本发明涉及半导体制造领域,特别是一种拥有较高功率密度IGZO薄膜晶体管。

背景技术

柔性电子是将有机或无机材料电子器件制作在柔性基板上的新兴电子技术,其具有柔性以及高效、低成本制造工艺等特点。

目前大部分有关柔性系统的研究集中在提升器件性能以及可靠性方面,对提升薄膜晶体管耐压能力的研究几乎为空白。当前的柔性电子产品仍大量使用传统固态原件,尤其是电源管理模块,高性能柔性功率器件的缺失导致“全柔性”无法实现。为了实现真正意义上的“全柔性”器件,具有高功率密度的薄膜晶体管亟待发明。

柔性薄膜材料中,氧化铟镓锌氧化物IGZO薄膜晶体管具有高迁移率、高开关电流比等优点,已经应用于柔性显示屏、可折叠穿戴设备、柔性传感器等商业产品。现有关于提升IGZO薄膜晶体管耐压值的研究主要包括两种方法。其一是通过原子层沉积(ALD)工艺制备高质量、高介电常数的绝缘介电层。另一种方法通过偏移栅极、漏电极之间的距离来提升IGZO薄膜晶体管极限耐压。ALD工艺制备成本高,且不适合大规模生产。偏移栅极、漏电极之间的距离会使器件电流密度大打折扣,从而降低器件功率密度。据现有研究发现,一定范围内提升IGZO薄膜厚度对器件电流密度几乎无影响,因此增加栅介电层厚度必然会导致器件电流密度的牺牲。因此有必要提出一种创新型IGZO薄膜晶体管结构,在提升器件耐压能力的同时降低电流密度的牺牲,提升器件功率密度。

发明内容

技术问题:鉴于上述问题,本发明提供了一种带有阶梯栅氧结构的IGZO薄膜晶体管,有效提升器件击穿电压、降低电流能力的牺牲,显著提高器件最大功率密度。

技术方案:本发明一种高功率密度IGZO薄膜晶体管包括:

第一基底、第二基底;第二基底位于第一基底上;

栅电极,位于所述第二基底上;

第一层栅介电层,位于所述栅电极之上的一端;

第二层栅介电层,位于所述栅电极之上,其一端覆盖住第一层栅介电层,二者构成“阶梯型”栅介电层;

铟镓锌氧化物IGZO有源层,位于所述“阶梯型”栅介电层上并覆盖住第一层栅介电层和第二层栅介电层;

第一源电极、第二漏电极,位于铟镓锌氧化物IGZO有源层上相对两侧,其中第二漏电极位于第一层栅介电层之上方一侧,第一源电极位于远离第一层栅介电层的另一侧。

所述第一基底为半导体衬底,在所述半导体衬底上的第二基底为绝缘氧化层。

所述第一层栅介电层、第二层栅介电层构成双层材料的栅介电层,第一层栅介电层设于栅电极之上,长度为2~6um;第二层栅介电层设于栅电极上并覆盖住第一层栅介电层;两层栅介电层形成“阶梯状”。

所述铟镓锌氧化物IGZO有源层位于源电极、漏电极之间的部分为沟道。

所述沟道长度为10~100um。

所述铟镓锌氧化物IGZO有源层厚度为10nm~40nm,形成于所述“阶梯型”的第二层栅介电层上。

所述第一层栅介电层为利用溶液工艺制备的二氧化锆ZrO

所述第二层栅介电层为利用溶液工艺制备的氧化铝Al

有益效果:传统的IGZO薄膜晶体管主要通过增加栅介电层的厚度来提升耐压能力,而这必然导致栅控能力减弱,输出电流降低。本发明提供的具有“阶梯型”栅氧结构的IGZO薄膜晶体管仅提升了漏极一侧(也是易发生击穿的主要位置)的栅介电层厚度,可以有效地降低栅介电层承担的电场,提升耐压能力;而沟道上方的栅介电层厚度保持不变,尽可能地减少输出电流的损失,以此达到提升功率密度的目的。在本实施例中采用ZrO

附图说明

为了更好地描述和说明这里公开的那些发明的实施例和/或示例,可以参考一幅或多幅附图。用于描述附图的附加细节或示例不应当被认为是对所公开的发明、目前描述的实施例和/或示例以及目前理解的这些发明的最佳模式中的任何一者的范围的限制。

图1是现有的IGZO薄膜晶体管的示意图;

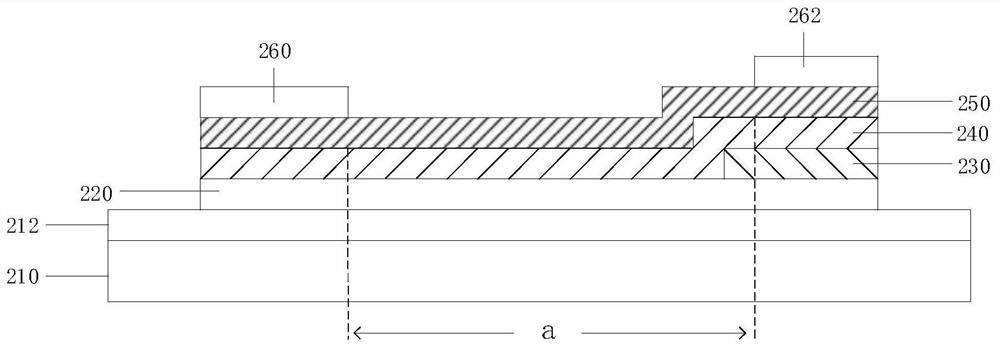

图2是本发明的一实施例中IGZO薄膜晶体管的示意图;

图3是一实施例中IGZO薄膜晶体管的制造方法的流程图;

图4是一实施例中步骤S330的子流程图;

图5是一实施例中步骤S340的子流程图;

图6是一实施例中步骤S350的子流程图;

图7是本发明实施例与对比例的IGZO薄膜晶体管电流曲线图;

图8是本发明实施例与对比例的IGZO薄膜晶体管电场分布图。

表1是本发明实施例与对比例的参数表格对比图。

具体实施方式

为了便于理解本发明,下面将参照相关附图对本发明进行更全面的描述。附图中给出了本发明的首选实施例。但是,本发明可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使对本发明的公开内容更加透彻全面。

除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本发明。本文所使用的术语“及/或”包括一个或多个相关的所列项目的任意的和所有的组合。

应当明白,当元件或层被称为“在...上”、“与...相邻”、“连接到”或“耦合到”其它元件或层时,其可以直接地在其它元件或层上、与之相邻、连接或耦合到其它元件或层,或者可以存在居间的元件或层。相反,当元件被称为“直接在...上”、“与...直接相邻”、“直接连接到”或“直接耦合到”其它元件或层时,则不存在居间的元件或层。应当明白,尽管可使用术语第一、第二、第三等描述各种元件、部件、区、层和/或部分,这些元件、部件、区、层和/或部分不应当被这些术语限制。这些术语仅仅用来区分一个元件、部件、区、层或部分与另一个元件、部件、区、层或部分。因此,在不脱离本发明教导之下,下面讨论的第一元件、部件、区、层或部分可表示为第二元件、部件、区、层或部分。

空间关系术语例如“在...下”、“在...下面”、“下面的”、“在...之下”、“在...之上”、“上面的”等,在这里可为了方便描述而被使用从而描述图中所示的一个元件或特征与其它元件或特征的关系。应当明白,除了图中所示的取向以外,空间关系术语意图还包括使用和操作中的器件的不同取向。例如,如果附图中的器件翻转,然后,描述为“在其它元件下面”或“在其之下”或“在其下”元件或特征将取向为在其它元件或特征“上”。因此,示例性术语“在...下面”和“在...下”可包括上和下两个取向。器件可以另外地取向(旋转90度或其它取向)并且在此使用的空间描述语相应地被解释。

在此使用的术语的目的仅在于描述具体实施例并且不作为本发明的限制。在此使用时,单数形式的“一”、“一个”和“所述/该”也意图包括复数形式,除非上下文清楚指出另外的方式。还应明白术语“组成”和/或“包括”,当在该说明书中使用时,确定所述特征、整数、步骤、操作、元件和/或部件的存在,但不排除一个或更多其它的特征、整数、步骤、操作、元件、部件和/或组的存在或添加。在此使用时,术语“和/或”包括相关所列项目的任何及所有组合。

对于传统的IGZO薄膜溶液制备工艺,通过控制栅介电层的厚度是常用的提升薄膜晶体管耐压的方法。但是栅介电层厚度的提升会导致栅控能力减弱,输出电流减小,薄膜晶体管的功率密度无明显提升。

随着学术界与产业界的不断发展,提出了两种方法来提升α-IGZO薄膜晶体管的耐压能力。主要包括:1)通过原子层沉积(ALD)工艺制备高质量、高介电常数的绝缘介电层。2)偏移栅极、漏极之间的距离来提升IGZO薄膜晶体管的极限耐压。然而,ALD工艺制备成本高,不适合大规模生产;偏移栅极、漏极之间的距离会使器件电流密度大打折扣,从而降低功率密度。本发明提出了一种通过改变薄膜晶体管结构来提升耐压能力从而提升功率密度的方法。

本发明提供的IGZO薄膜晶体管结构图如图2所示,自下而上分别是:基底210(包括基底上的绝缘层212)、栅电极220、第一层栅介电层230、第二层栅介电层240、IGZO沟道层250、源极260和漏极262。第二层栅介电层240设于栅电极220上并覆盖住第一层栅介电层230,两层栅介电层形成“阶梯型”的结构。

一种IGZO薄膜晶体管,包括:基底;栅电极,形成于基底之上;两种不同材料构成的“阶梯型”栅介电层,形成于栅电极之上;IGZO有源层,形成于“阶梯型”栅介电层之上;源电极、漏电极,位于IGZO有源层上相对两侧,二者之间间距为沟道长度。

本发明的一个实施例中,所述衬底包括半导体衬底和半导体衬底上的绝缘氧化层,所述栅电极为ITO电极,所述第一层栅介电层为二氧化锆(ZrO

本发明的IGZO薄膜晶体管的制备方法,包括:获取基底;在所述基底上形成栅电极;在栅电极上形成第一层栅介电层;在栅电极上形成第二层栅介电层并覆盖住第一层栅介电层,二者形成“阶梯型”栅介电层;在“阶梯型”栅介电层上形成IGZO有源层;在IGZO有源层上源电极和漏电极。

本发明的一个实施例中,利用溶液旋涂工艺在基底上形成栅电极,利用溶液工艺形成第一层ZrO

图1是现有的IGZO薄膜晶体管的示意图,图2是本发明一实施例中IGZO薄膜晶体管的示意图,图3为一实施例中IGZO薄膜晶体管的制造方法的流程图,该方法可以用于制造图2所示的IGZO薄膜晶体管,具体包括如下步骤:

S310,获取基底。

基底可以是本领域习知的刚性基底(例如玻璃)或柔性基底。在一个实施例中,基底为半导体衬底,例如硅衬底。

S320,通过溶液工艺在基底上形成栅电极。

在本实施例中,可以在硅衬底上氧化形成二氧化硅层,然后再于二氧化硅层上形成ITO栅电极。也可以采用本领域习知的其他源漏材质/结构作为栅电极。

S330,在栅电极上形成第一层栅介电层。

在本实施例中,是在步骤S320后于栅电极上形成第一层栅介电层。在本实施例中,第一层栅介电层的长度为2um,材料为ZrO

S340,在栅电极上形成第二层栅介电层。

在本实施例中,第二层栅介电层设于栅电极之上并覆盖住第一层栅介电层。在本实施例中,第二层栅介电层未延伸至基底之上。在其他实施例中,栅介电层也可以延伸至基底上。在本实施例中,第二层栅介电层的长度为11um,材质为Al

S350,通过溶液工艺在“阶梯型”栅介电层上形成IGZO有源层。

在本实施例中,是在步骤S340后于“阶梯型”栅介电层上形成IGZO有源层,并且IGZO有源层覆盖住第一层栅介电层。

S360,在IGZO有源层上形成源电极、漏电极。

在本实施例中,源电极、漏电极为ITO电极;在其他实施例中,也可以采用其他本领域习知的栅极材质作为源电极/漏电极。在本实施例中,源电极、漏电极之间间距为10um。

上述IGZO薄膜晶体管的制造方法,在传统结构IGZO薄膜晶体管栅电极与栅介电层之间靠近漏极的一侧(即易发生击穿的位置)增加了ZrO

参见图4,在一个实施例中,步骤S330包括:

S332,制作ZrO

在一个实施例中,是将硝酸氧锆(ZrO(NO)

S334,将ZrO

在一个实施例中,是将ZrO

S336,进行热退火处理。

在一个实施例中,是将旋涂有ZrO

参见图5,在一个实施例中,步骤S340包括:

S342,制作Al

在一个实施例中,是将硝酸铝水合物(Al(NO

S344,将Al

在一个实施例中,是将Al

S346,进行热退火处理。

在一个实施例中,是将旋涂有Al

参见图6,在一个实施例中,步骤S350包括:

S332,制作IGZO前体溶液。

在一个实施例中,是将硝酸铟(III)水合物(ln(NO

在一个实施例中,步骤S332具体是在室内环境下将硝酸铟(III)水合物(ln(NO

S224,将IGZO前体溶液旋涂于“阶梯型”栅介电层上。

在一个实施例中,是将α-IGZO前体溶液旋涂于“阶梯型”栅介电层上并以4000RPM(转/分)的速度旋转30秒。

S226,进行热退火处理。

在一个实施例中,是将旋涂有IGZO前体溶液的“阶梯型”栅介电层在400℃温度条件下退火30分钟。

申请还提供一种IGZO薄膜晶体管,该IGZO薄膜晶体管可以通过以上任一实施例的制造方法进行制备。如图2所示,IGZO薄膜晶体管包括基底210、栅电极220、第一层栅介电层230、第二层栅介电层240、IGZO有源层250、源电极260以及漏电极262。基底210可以是本领域习知的刚性基底(例如玻璃)或柔性基底。在一个实施例中,基底为半导体衬底,例如硅衬底。在图2所示的实施例中,IGZO薄膜晶体管采用底栅交错(Bottom-gate/Top-contact)结构。需要指出的是,各膜层在图2中的尺寸只是一个示意,并不代表其实际尺寸。

栅电极220形成于基底210上。在一个实施例中,栅极250为ITO电极。

第一层栅介电层230形成于栅电极220上。第二层栅介电层240形成于栅电极220上并覆盖住第一层栅介电层230。两层栅介电层构成“阶梯型”栅介电层。在一个实施例中,第一层栅介电层230材质为ZrO

IGZO有源层250设于“阶梯型”栅介电层之上。在图2所示的实施例中,IGZO有源层250是通过溶液工艺形成。

源电极260与漏电极262形成于IGZO有源层250上。其中漏电极262设于第一层栅介电层230上方,而源电极260设于远离第一层栅介电层的一侧。在图2所示的实施例中,间距a为10um。在图2所示的实施例中,源极260为ITO电极、漏极262为ITO电极,在其他实施例中,也可以采用本领域习知的其他源漏材质/结构作为源极和漏极。

在一个实施例中,IGZO有源层250为α-IGZO薄膜。在IGZO薄膜晶体管工作时,栅极220接正电压,在α-IGZO薄膜沟道中积累形成负电荷,漏极262加电进行载流子输运形成电流。

在图2所示的实施例中,IGZO薄膜晶体管还包括设于基底210上的绝缘氧化层212。在一个实施例中,绝缘氧化层212的材质为二氧化硅。

在图2所示的实施例中,栅极220的厚度为100nm,第一层栅介电层230的厚度为100nm,第2层栅介电层240的厚度为100nm,IGZO有源层250的厚度为40nm,源极222和漏极224的厚度为100nm。沟道a的长度为10um。

图7是本申请实施例与对比例的IGZO薄膜晶体管漏极电流曲线图,其中对比例为1)仅有单层100nmAl

由上述数据可知,相较于对比例1的薄栅介电层IGZO薄膜晶体管而言,本实施例的阶梯栅氧结构与对比例2的厚栅氧层结构都可以提升IGZO薄膜晶体管的耐压能力,并且效果相当,而电流能力都有所损失。但本实施例的电流损失明显小于对比例2,即在耐压能力相同时本实施例的电流能力更强,功率密度更高。当栅极电压为4V时,本发明的实施例的功率密度为1.428W/cm,而对比例1、对比例2的功率密度分别为1.043W/cm和0.838W/cm。由此可知,本发明的IGZO薄膜晶体管与传统的IGZO薄膜晶体管相比,功率密度提升了36.9%,与传统的提升薄膜晶体管厚度的方法相比,功率密度提升了70.4%。

以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

本发明提供的IGZO薄膜晶体管结构图如图2所示,自下而上分别是:基底210(包括基底上的绝缘层212)、栅电极220、第一层栅介电层230、第二层栅介电层240、IGZO沟道层250、源极260和漏极262。第二层栅介电层240设于栅电极220上并覆盖住第一层栅介电层230,两层栅介电层形成“阶梯型”的结构。

一种IGZO薄膜晶体管,包括:基底;栅电极,形成于基底之上;两种不同材料构成的“阶梯型”栅介电层,形成于栅电极之上;IGZO有源层,形成于“阶梯型”栅介电层之上;源电极、漏电极,位于IGZO有源层上相对两侧,二者之间间距为沟道长度。

本发明的一个实施例中,所述衬底包括半导体衬底和半导体衬底上的绝缘氧化层。

本发明的一个实施例中,所述栅电极为ITO电极。

本发明的一个实施例中,所述第一层栅介电层为二氧化锆(ZrO

本发明的一个实施例中,所述第二层栅介电层为氧化铝(Al

本发明的一个实施例中,IGZO有源层形成于“阶梯型”栅介电层之上并覆盖住第一层栅介电层。

本发明的一个实施例中,所述源电极、漏电极均为ITO电极。

一种IGZO薄膜晶体管的制备方法,包括:获取基底;在所述基底上形成栅电极;在栅电极上形成第一层栅介电层;在栅电极上形成第二层栅介电层并覆盖住第一层栅介电层,二者形成“阶梯型”栅介电层;在“阶梯型”栅介电层上形成IGZO有源层;在IGZO有源层上源电极和漏电极。

本发明的一个实施例中,利用溶液旋涂工艺在基底上形成栅电极。

本发明的一个实施例中,利用溶液工艺形成第一层ZrO

本发明的一个实施例中,利用溶液工艺形成第二层Al

本发明的一个实施例中,所述通过溶液工艺形成IGZO有源层的步骤包括:制作IGZO前体溶液;将所述IGZO前体溶液旋涂于先前形成的“阶梯型”栅介电层上。

本发明的一个实施例中,还包括对旋涂了所述IGZO前体溶液的基底进行热退火处理的步骤。

本发明的一个实施例中,所述制作IGZO前体溶液的步骤包括:将硝酸铟水合物、硝酸锌水合物、硝酸镓水合物溶解于2-甲氧基乙醇溶剂中并进行搅拌;将搅拌后的液体进行过滤得到所述IGZO前体溶液。

本发明的一个实施例中,所述将硝酸铟水合物、硝酸锌水合物、硝酸镓水合物溶解于2-甲氧基乙醇溶剂中的步骤中,硝酸铟水合物、硝酸锌水合物、硝酸镓水合物的摩尔比是6:1:1。

本发明的一个实施例中,利用溶液工艺形成源电极、漏电极。

本发明的一个实施例中,所述过滤是使用0.2微米厚的聚四氟乙烯滤膜进行。

表1是本发明实施例与对比例的参数表格对比。

表1

- 一种高功率密度IGZO薄膜晶体管

- IGZO纳米线的制备方法、IGZO薄膜晶体管及其制备方法