基于M-LVDS总线的多板卡通信系统及方法

文献发布时间:2023-06-19 10:08:35

技术领域

本发明涉及数字通信技术领域,具体地,涉及一种基于M-LVDS总线的多板卡通信系统及方法。

背景技术

在轨道交通的控制系统等嵌入式系统中,存在很多板卡,这些板卡之间需要通信。目前板级间通信广泛使用的通信协议有:PCI、CAN、I2C、SPI、串口、以太网等,其中串行通信使用较多的是CAN总线协议。基于安全性、方便性、低成本等方面的考虑,CAN总线协议在汽车产业中广泛使用,CAN总线最大支持长度为40米,最高通信速度为1Mbps。

在轨道交通控制系统中,板卡之间的传输速率要求在25Mbps~100Mbps之间,CAN总线已无法满足通信要求。以太网传输支持10/100/1000Mbps等传输速率,但以太网的实时性、可靠性较差,不适合在控制类嵌入式系统中使用。

专利文献CN108038073Agon公开了一种基于MLVDS的多板卡通信系统,包括相互连接通信的一个第一通信板卡及多个第二通信板卡,第一通信板卡及第二通信板卡包括一个FPGA芯片、第一MLVDS芯片、第二MLVDS芯片;第一通信板卡包括时钟芯片;第一通信板卡的FPGA芯片分别与时钟芯片及第一通信板卡的第二MLVDS芯片连接,时钟芯片与第一通信板卡的第一MLVDS芯片连接;第二通信板卡的FPGA芯片分别与第二通信板卡的第一MLVDS芯片、第二MLVDS芯片连接;第一通信板卡的第二MLVDS芯片与第二通信板卡的第二MLVDS芯片经数据总线连接,第一通信板卡的第一MLVDS芯片与第二通信板卡的第一MLVDS芯片经时钟总线连接实现第一通信板卡与第二通信板卡共享时钟。该专利在结构和技术效果上仍然有待提高的空间。

发明内容

针对现有技术中的缺陷,本发明的目的是提供一种基于M-LVDS总线的多板卡通信系统及方法。

根据本发明提供的一种基于M-LVDS总线的多板卡通信系统,包括:M-LVDS总线、M-LVDS驱动芯片、M-LVDS控制器;所述M-LVDS控制器(基于FPGA实现)输出控制与数据的数字信号给M-LVDS驱动芯片;所述M-LVDS驱动芯片实现数字信号与差分电平信号的转换;将0、1数字信号转换成M-LVDS总的H/L信号,所述M-LVDS总线作为传输介质,能够传输H/L等电平信号;所述M-LVDS总线与发送通路相应的是接收通路,在接收方向,M-LVDS驱动芯片将M-LVDS总线上的H/L电平信号转换成数字信号,提交给M-LVDS控制器。

优选地,还包括:板卡部件;

所述M-LVDS驱动芯片、M-LVDS控制器设置于板卡部件上;

所述板卡部件与M-LVDS总线相连。

优选地,所述板卡部件的数量为一个或者多个;

所述多个板卡部件与M-LVDS总线相连。

优选地,所述M-LVDS总线是共享总线;

所述M-LVDS总线上的每个节点都能够发起传输事务。

为了解决多节点争夺总线使用权问题,需要定义仲裁策略。由于仲裁时存在多节点同时驱动总线的可能,导致总线上信号质量变差。因此本发明规定总线上只能有一个节点可以主动发起总线事务。这个节点一般是控制系统中的主处理器板,负责数据收集和处理。本发明称这个节点为主节点,其它节点为从节点。

优选地,所述M-LVDS总线上的每个节点都设置有唯一的机箱号和槽位号,作为节点的唯一标识。主节点定期产生控制帧,根据机箱号和槽位号依次轮询总线上的其它节点是否还处于活动状态,以此识别总线上的节点。关于控制帧的格式,以及从节点应答帧的格式在后续帧格式定义部分介绍。

如果从节点长时间没有接收到控制帧,将通过指示灯显示在机箱面板上。

主节点根据接收到的从节点的应用帧,确定总线上有多少节点。

优选地,所述M-LVDS总线上的主节点在发送控制帧的同时,也能够监听发送的控制帧。这主要是为了检测主节点与总线的连接没有故障。如果主节点无法监听到发送的控制帧,则可能是主节点的发送通路出现故障;或主节点的接收通路出现故障。此时,主节点将停止发送控制帧,并通过指示灯显示在机箱面板上。

在总线上可以设置一个备份主节点。备份主节点如果长时间没有接收到控制帧,将激活成主节点,接管总线,生成控制帧,发送到总线上。

优选地,根据M-LVDS总线传输帧格式定义控制信息,对传输帧格式进行定义,获取M-LVDS总线传输帧格式定义结果信息。

在总线上传输的帧的格式见图2所示。帧格式说明如下:

帧起始符:8位,值为8’h00,用于标识帧的开始;

帧同步符:8位,值位8’hAA,用于从节点的时钟恢复;

帧类型:8位,帧类型值编码如下:

8’hff:控制帧,用于轮询节点是否处于活动状态。从节点接收到控制帧后,将驱动控制响应帧到总线上;

8’hf0:控制响应帧,用于应对主节点的控制帧。从节点接收到控制帧后,将驱动控制响应帧到总线上。控制帧与响应控制帧以成对的方式出现,具体格式及时序关系见图3所示。

8’hf5:写命令帧,用于主节点写数据到从节点。写命令帧与图2的标准传输帧格式相同。

8’hf6:读命令帧,用于主节点发送读命令到从节点。

8’hf7:读命令响应帧,用于从节点发送读数据到总线上。读命令帧和读命令响应帧以成对的方式出现,两者的格式及时序关系见图4所示。

帧长度:8位,指示数据负载部分的字节数,以16位,即2个字节为单位。0表示没有数据负载,1表示数据负载部分有2个字节,2表示数据负载部分有4个字节,…,依次类推,最大值255表示数据负载有510个字节。具体实现时,可以限定帧长度的最大值为128,即数据负载最大256字节;

目标节点地址/从节点地址:16位,由8位机箱号+8位槽位地址组成。

数据负载:长度由帧长度决定,具体内容由软件解析;

校验码:16位,是根据帧类型、帧长度、目标节点地址、数据负载等部分生成的校验码。

总线上的帧传输都是主节点发起,从节点的响应帧都是在接收到控制帧或命令帧之后的8个时钟周期后响应。如果从节点在64个总线周期内没有检测到总线上有信号,则判断从节点不在总线上。响应帧与新的控制帧或命令帧的间隔在32个总线时钟周期以上。

优选地,所述M-LVDS总线上的所有节点的参考时钟频率都是100MHz。总线上支持的时钟频率有:1MHz、10MHz、25MHz、50MHz、100MHz等。从节点接入到总线上后,首先要确定总线上的帧起始符,其特征是总线在一段时间的空闲状态(没有任何设备驱动总线,M-LVDS驱动芯片输出给FPGA的信号是1)后出现一个下降沿,然后在出现上升沿。通过两个沿之间参考时钟(100MHz)计数周期数,可以判断总线时钟的周期数。例如,两个沿之间的计数器值在750以上,则可推断总线传输时钟频率为1MHz;如果计数器值在75~85之间,可初步推断总线时钟频率在10MHz左右。根据帧起始符,只能初步猜测总线的传输时钟频率。后面还要根据帧同步符进一步确认总线的传输时钟频率。

从节点接入总线上后,可能要经过2-3个帧之后,才能确定总线传输时钟频率。

根据本发明提供的一种基于M-LVDS总线的多板卡通信方法,采用基于M-LVDS总线的多板卡通信系统,能够基于M-LVDS总线进行多板卡通信。

与现有技术相比,本发明具有如下的有益效果:

1、本发明能够满足1Mbs~100Mbps的传输速率要求,支持节点数可达32个,传输距离可达50米;

2、本发明可以满足轨道交通控制系统等控制类嵌入式系统的应用要求;

3、本发明构造合理,使用方便,能够克服现有技术的缺陷。

附图说明

通过阅读参照以下附图对非限制性实施例所作的详细描述,本发明的其它特征、目的和优点将会变得更明显:

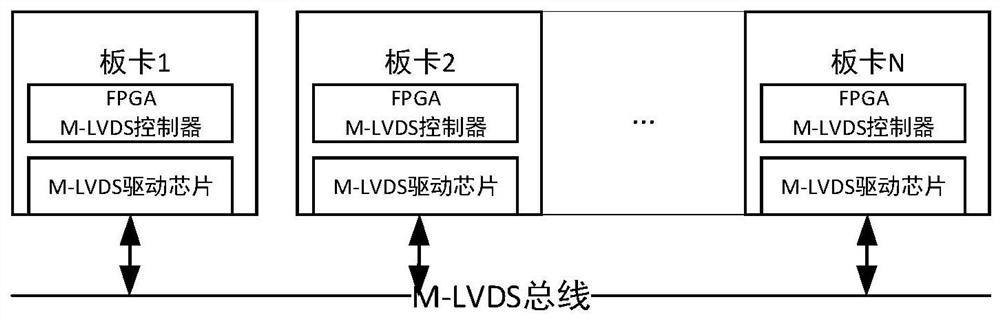

图1为本发明提供的基于M-LVDS总线的多板卡通信系统示意图。

图2为本发明实施例中的传输帧格式示意图。

图3为本发明实施例中的控制帧与控制应答帧示意图。

图4为本发明实施例中的读命令帧与读命令响应帧示意图。

图5为本发明实施例中的主节点M-LVDS控制器结构框示意图。

具体实施方式

下面结合具体实施例对本发明进行详细说明。以下实施例将有助于本领域的技术人员进一步理解本发明,但不以任何形式限制本发明。应当指出的是,对本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变化和改进。这些都属于本发明的保护范围。

图1展示了基于M-LVDS总线的多板卡通信系统结构框图。M-LVDS控制器(基于FPGA实现)输出控制与数据的数字信号给M-LVDS驱动芯片,M-LVDS驱动芯片实现数字信号与差分电平信号的转换,将0、1数字信号转换成M-LVDS总的H/L信号,M-LVDS总线作为传输介质,传输H/L等电平信号。与发送通路相应的是接收通路,在接收方向,M-LVDS驱动芯片将M-LVDS总线上的H/L电平信号转换成数字信号,提交给M-LVDS总线控制器。这里简述了基于M-LVDS总线传输数据的过程,下面介绍本发明的具体实现方法。

要点1:定义仲裁策略

理论上,M-LVDS总线是共享总线,总线上的每个节点都可以发起传输事务,为了解决多节点争夺总线使用权问题,需要定义仲裁策略。由于仲裁时存在多节点同时驱动总线的可能,导致总线上信号质量变差。因此本发明规定总线上只能有一个节点可以主动发起总线事务。这个节点一般是控制系统中的主处理器板,负责数据收集和处理。本发明称这个节点为主节点,其它节点为从节点。

要点2:对总线上节点的识别

总线上的每个节点都有唯一的机箱号和槽位号,作为节点的唯一标识。主节点定期产生控制帧,根据机箱号和槽位号依次轮询总线上的其它节点是否还处于活动状态,以此识别总线上的节点。关于控制帧的格式,以及从节点应答帧的格式在后续帧格式定义部分介绍。

如果从节点长时间没有接收到控制帧,将通过指示灯显示在机箱面板上。

主节点根据接收到的从节点的应用帧,确定总线上有多少节点。

要点3:对可靠性的实现

主节点在发送控制帧的同时,也会监听发送的控制帧。这主要是为了检测主节点与总线的连接没有故障。如果主节点无法监听到发送的控制帧,则可能是主节点的发送通路出现故障;或主节点的接收通路出现故障。此时,主节点将停止发送控制帧,并通过指示灯显示在机箱面板上。

在总线上可以设置一个备份主节点。备份主节点如果长时间没有接收到控制帧,将激活成主节点,接管总线,生成控制帧,发送到总线上。

要点4:对传输帧格式的定义

在总线上传输的帧的格式见图2所示。帧格式说明如下:

帧起始符:8位,值为8’h00,用于标识帧的开始;

帧同步符:8位,值位8’hAA,用于从节点的时钟恢复;

帧类型:8位,帧类型值编码如下:

8’hff:控制帧,用于轮询节点是否处于活动状态。从节点接收到控制帧后,将驱动控制响应帧到总线上;

8’hf0:控制响应帧,用于应对主节点的控制帧。从节点接收到控制帧后,将驱动控制响应帧到总线上。控制帧与响应控制帧以成对的方式出现,具体格式及时序关系见图3所示。

8’hf5:写命令帧,用于主节点写数据到从节点。写命令帧与图2的标准传输帧格式相同。

8’hf6:读命令帧,用于主节点发送读命令到从节点。

8’hf7:读命令响应帧,用于从节点发送读数据到总线上。读命令帧和读命令响应帧以成对的方式出现,两者的格式及时序关系见图4所示。

帧长度:8位,指示数据负载部分的字节数,以16位,即2个字节为单位。0表示没有数据负载,1表示数据负载部分有2个字节,2表示数据负载部分有4个字节,…,依次类推,最大值255表示数据负载有510个字节。具体实现时,可以限定帧长度的最大值为128,即数据负载最大256字节;

目标节点地址/从节点地址:16位,由8位机箱号+8位槽位地址组成。

数据负载:长度由帧长度决定,具体内容由软件解析;

校验码:16位,是根据帧类型、帧长度、目标节点地址、数据负载等部分生成的校验码。

总线上的帧传输都是主节点发起,从节点的响应帧都是在接收到控制帧或命令帧之后的8个时钟周期后响应。如果从节点在64个总线周期内没有检测到总线上有信号,则判断从节点不在总线上。响应帧与新的控制帧或命令帧的间隔在32个总线时钟周期以上。

要点5:传输时钟频率判断

总线上所有节点的参考时钟频率都是100MHz。总线上支持的时钟频率有:1MHz、10MHz、25MHz、50MHz、100MHz等。从节点接入到总线上后,首先要确定总线上的帧起始符,其特征是总线在一段时间的空闲状态(没有任何设备驱动总线,M-LVDS驱动芯片输出给FPGA的信号是1)后出现一个下降沿,然后在出现上升沿。通过两个沿之间参考时钟(100MHz)计数周期数,可以判断总线时钟的周期数。例如,两个沿之间的计数器值在750以上,则可推断总线传输时钟频率为1MHz;如果计数器值在75~85之间,可初步推断总线时钟频率在10MHz左右。根据帧起始符,只能初步猜测总线的传输时钟频率。后面还要根据帧同步符进一步确认总线的传输时钟频率。

从节点接入总线上后,可能要经过2-3个帧之后,才能确定总线传输时钟频率。

要点6:总线信号的翻转率

对于帧传输,从帧的类型开始,到帧的校验码结束,如果出现连续5个0或1,将自动插入一位反码,从而保证总线信号上有足够的翻转率,不会出现总线上长时间的0或1,导致节点误以为从设备不存在。

要点7:帧校验码的生成

校验码覆盖的对象包括帧类型、帧长度、目标节点地址、数据负载等部分。校验码的生成使用CRC16_CCITT多项式:x^16+x^12+x^5+1计算生成。

要点8:帧的接收

节点判断出总线时钟频率后,首先恢复出跟总线时钟频率相应的总线时钟BUS_CLK。在接收通路上,有两套并行的接收处理逻辑,这两套逻辑的工作时钟分别是BUS_CLK和~BUS_CLK,即总线时钟和总线时钟的反相。两套接收逻辑都会生成校验结果。如果两套接收逻辑的校验结果都正确,则取BUS_CLK一路接收到的数据进一步处理;如果一套校验码正确,一套校验码不正确,则取校验码正确的一路;如果两套校验码都不正确,则丢弃接收到的数据,不做响应。

上述8个要点,是实现基于M-LVDS总线的通信系统实现方法的主要技术要点。在具体实现,还会采用一些具体细节,例如在接收通路上使用”乒乓FIFO”等,本文不再具体说明。

在本申请的描述中,需要理解的是,术语“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本申请和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本申请的限制。

以上对本发明的具体实施例进行了描述。需要理解的是,本发明并不局限于上述特定实施方式,本领域技术人员可以在权利要求的范围内做出各种变化或修改,这并不影响本发明的实质内容。在不冲突的情况下,本申请的实施例和实施例中的特征可以任意相互组合。

- 基于M-LVDS总线的多板卡通信系统及方法

- 一种基于M-LVDS实时多主高速总线的通信系统