一种时钟分频系统、方法及设备

文献发布时间:2023-06-19 10:38:35

技术领域

本发明实施例涉及电子电路设计与通信技术,尤其涉及一种时钟分频系统、方法及设备。

背景技术

SOC(System On Chip,系统级芯片)中包含的各子系统或模块的工作频率可能各不相同,因此需要时钟电路进行分频。SOC时钟网络一般是从外部获取基频,然后由PLL(Phase Lock Loop,锁相环)将基频倍频到各子系统需要的基本频率和系统最高频率,最终由子系统内部的分频电路进行分频得到其他所需频点。

随着集成电路不断发展,一个SOC时钟网络相关时钟数量可能有成百上千,频点的分布也从几MHz到几GHz,在这种情况下,使用现有技术中分散的分频电路模块或单一的分频电路模块容易导致时钟关系混乱、时钟约束复杂,还可能影响时钟树综合的质量,从而影响芯片的时序收敛。

发明内容

本发明实施例提供一种时钟分频系统、方法及设备,采用多层次时钟分频模块,将复杂的SOC时钟网络结构进行层次化、规范化处理。

第一方面,本发明实施例提供了一种时钟分频系统,所述系统包括:绝对全局时钟生成模块、预分频模块以及至少一个子系统,每个子系统中包括时钟分频模块;绝对全局时钟生成模块与预分频模块相连,预分频模块分别与各子系统中的时钟分频模块相连;

所述绝对全局时钟生成模块,用于生成绝对全局时钟发送至预分频模块;

所述预分频模块,用于根据所述绝对全局时钟,生成与各子系统分别对应的相对全局时钟,并将各相对全局时钟下发至匹配的子系统中的时钟分频模块;

所述时钟分频模块,用于根据从预分频模块处获取的相对全局时钟,生成至少一个同步时钟;

其中,所述同步时钟用于提供至所述子系统的本级或下一级电子模块。

第二方面,本发明实施例还提供了一种时钟分频方法,所述方法包括:

绝对全局时钟生成模块根据外部参考时钟生成绝对全局时钟,并将所述绝对全局时钟发送至预分频模块;

所述预分频模块根据所述绝对全局时钟,生成与各子系统分别对应的相对全局时钟,并将各相对全局时钟下发至匹配的子系统中的时钟分频模块;

所述时钟分频模块根据从预分频模块处获取的相对全局时钟,生成至少一个同步时钟;

其中,所述同步时钟用于提供至所述子系统的本级或下一级电子模块。

第三方面,本发明实施例还提供了一种电子设备,包括:

本发明任意实施例提供的时钟分频系统。

本发明实施例的技术方案,绝对全局时钟生成模块根据外部参考时钟生成绝对全局时钟并发送至预分频模块,预分频模块根据绝对全局时钟,生成与各子系统分别对应的相对全局时钟,并将各相对全局时钟下发至匹配的子系统中的时钟分频模块,最终时钟分频模块根据从预分频模块处获取的相对全局时钟,生成至少一个同步时钟,用于提供至子系统的本级或下一级电子模块,解决了现有技术中使用分散的分频电路模块或单一的时钟分频电路模块容易导致时钟关系混乱、时钟约束复杂,影响时钟树综合质量的问题,采用多层次时钟专用模块将复杂的SOC时钟网络结构进行层次化、规范化处理。

附图说明

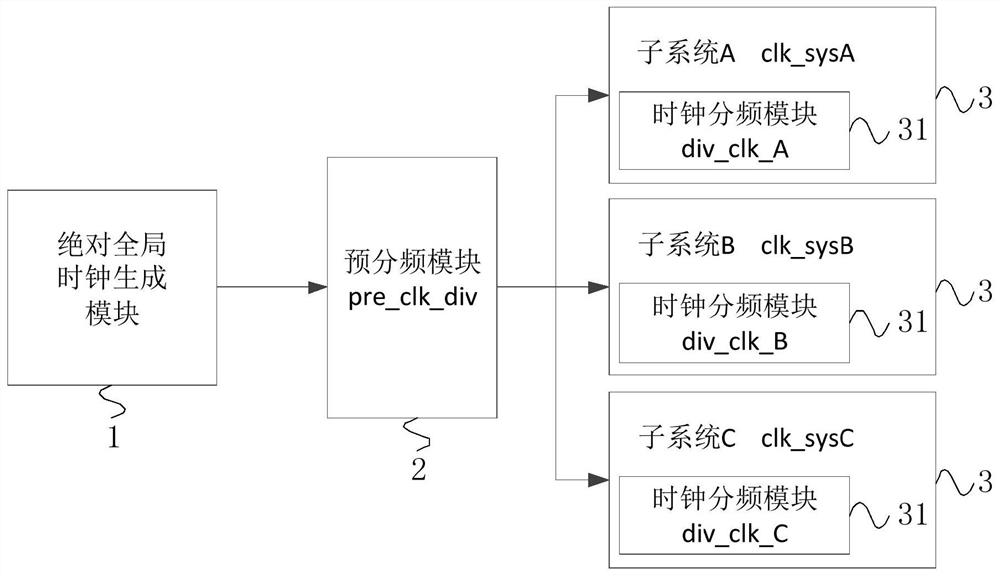

图1a是本发明实施例一中的一种时钟分频系统的结构示意图;

图1b是本发明实施例一中分散的分频电路模块的时钟结构示意图;

图1c是本发明实施例一中单一的时钟分频电路模块的时钟结构示意图;

图1d是本发明实施例一中的一种分层次时钟结构示意图;

图2是本发明实施例二中的一种时钟分频方法的流程图;

图3是本发明实施例三提供的一种电子设备的结构示意图。

具体实施方式

下面结合附图和实施例对本发明作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释本发明,而非对本发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本发明相关的部分而非全部结构。

实施例一

图1a为本发明实施例一中的一种时钟分频系统的结构示意图,本实施例的技术方案适用于将复杂的SOC时钟网络切分到各功能模块中的情况。

时钟对于数字系统而言是心跳,是脉搏,时序电路的事件触发大多都集中在时钟沿。时钟网络的设计实现贯穿芯片设计的全部流程,确保SOC时钟网络的正确和高效运行是十分关键的。为了便于理解,首先对现有技术中针对SOC的时钟结构进行说明,现有技术中常用的时钟结构包括使用分散的分频电路模块以及使用单一的时钟分频电路模块。

使用分散的分频电路模块的时钟结构如图1b所示,由锁相环直接将输出的时钟送入各时钟模块,由各时钟模块产生系统所需的功能时钟,这种结构一方面存在由锁相环送出的高频时钟需要进行远距离传输而导致的高能耗问题,另一方面还可能导致时钟树的源头延时过大,使功耗和时序不能得到较好的收敛。

使用单一的时钟分频电路模块的时钟结构如图1c所示,由锁相环产生的高频时钟经过时钟分频电路产生系统所需的功能时钟,这中方式在遇到复杂系统或者子模块过多时,还是与上述分散的分频电路模块的时钟结构存在同样的局限,且由于各功能时钟缺少统一的同步关系界定,在后续的时钟约束、时钟测试以及时钟树综合等相关过程中增加困难。

下面结合图1a对本发明实施例一提供的一种时钟分频系统进行说明:

时钟分频系统包括绝对全局时钟生成模块1、预分频模块2以及至少一个子系统3,每个子系统3中包括时钟分频模块31;绝对全局时钟生成模块1与预分频模块2相连,预分频模块2分别与各子系统3中的时钟分频模块31相连。

本实施例中,时钟分频系统中包括包括绝对全局时钟生成模块1、预分频模块2(pre_clk_div),以及至少一个子系统3(例如图1a中所示的,clk_ssysA、clk_ssysB和clk_ssysC),每个子系统3中包括时钟分频模块31。具体的连接关系包括,绝对全局时钟生成模块1与预分频模块2相连,预分频模块2与各子系统3包含的时钟分频模块31相连。其中,绝对全局时钟生成模块1能够统一整合外部输入的参考时钟信号,生成高频时钟,使高频器件正常工作。

绝对全局时钟生成模块1,用于生成绝对全局时钟发送至预分频模块2。

本实施例中,将外部参考时钟通过功能管脚输入到系统内部的绝对全局时钟生成模块1,由绝对全局时钟生成模块1根据外部参考时钟,生成系统所需的绝对全局时钟,并将绝对全局时钟生成模块1产生的绝对全局时钟发送至预分频模块2。

可选的,绝对全局时钟生成模块1可以是锁相环(Phase Lock Loop,PLL)。

预分频模块2,用于根据绝对全局时钟,生成与各子系统3分别对应的相对全局时钟,并将各相对全局时钟下发至匹配的子系统3中的时钟分频模块31;

本实施例中,为了避免时钟远距离传输造成的功耗较大的问题,在时钟分频系统中引入预分频模块2,预分频模块2在接收到绝对全局时钟生成模块1发送的绝对全局时钟后,根据各子系统3所需的时钟频率,对绝对全局时钟进行分频,生成与各子系统3分别对应的相对全局时钟,并将各相对全局时钟下发至匹配的子系统3中的时钟分频模块31。其中,每个时钟分频模块31可以根据实际需求,接收至少一个相对全局时钟。

可选的,预分频模块2输出的至少一个相对全局时钟均为异步时钟。

为了确保本实施例中的时钟分频系统的约束正确且简单易行,在分频系统结构设计的时候遵守和时钟约束相关的一些基本规则,本可选的实施例中提供了一种约束规则,预分频模块2输出的至少一个相对全局时钟均为异步时钟,各异步时钟放在不同时钟组。示例性的,预分频模块2产生的各时钟分别命名为*gmc_125M,*dma_125M,*SD0_96M以及*SD1_96M,各时钟均为异步。

基于上述规则,与预分频模块2相连的各子系统3的时钟输入端口不能同时存在同步的2个相对全局时钟,如果是2个同步时钟则需要合并,以保证输入至一个子系统3的时钟都是异步的。

时钟分频模块31,用于根据从预分频模块2处获取的相对全局时钟,生成至少一个同步时钟;

其中,同步时钟用于提供至子系统3的本级或下一级电子模块。

本实施例中,时钟分频模块31在接收到预分频模块2发送的相对全局时钟后,根据每个相对全局时钟,生成至少一个同步时钟,其中,同步时钟用于提供至子系统3的本级或下一级电子模块。

示例性的,时钟分频模块31接收到预分频模块2发送的2个相对全局时钟,分别为*gmc_125M和*dma_125M,时钟分频模块31可以根据相对全局时钟*gmc_125M,生成多个同步时钟,例如,生成2个同步时钟,分别为*gmc_125M和*gmc_62.5M;也可以根据相对全局时钟*dma_125M,生成多个同步时钟,例如,生成2个同步时钟,分别为*dma_125M和*dma_62.5M,当然,根据不同相对全局时钟生成的时钟均为异步时钟,例如,时钟分频模块31分别根据相对全局时钟*gmc_125M和*dma_125M生成的时钟*gmc_62.5M和*dma_62.5M为异步时钟。上述由时钟分频模块31生成的同步时钟用于提供至与子系统3相连的下一级电子模块,以为电子模块提供与其工作频率匹配的时钟。

可选的,各子系统3内部的时钟分频模块31生成的至少一个同步时钟,与预分频模块2生成的各相对全局时钟均为异步时钟。

本可选的实施例中,提供了一种和时钟约束相关的基本规则,各子系统3内部的时钟分频模块31生成的各同步时钟,与预分频模块2生成的各相对全局时钟均为异步时钟。示例性的,预分频模块2生成的时钟*gmc_125M,与子系统3内部的时钟分频模块31生成的时钟*gmc_125M为异步时钟。

可选的,时钟分频系统中的时钟走向为从预分频模块2指向到各子系统3包含的时钟分频模块31,不支持时钟逆向回传。

本可选的实施例中,提供了又一种和时钟约束相关的基本规则,规定了时钟分频系统中的时钟走向为从预分频模块2指向到各子系统3包含的时钟分频模块31,不支持时钟逆向回传。各底层电子模块之间如果存在同步路径,时钟需求需要从绝对全局时钟生成模块1接入,无需将子系统3生成的时钟回传出来。

可选的,预分频模块2的至少一个输出,与各子系统3内部的时钟分频模块31的输入功能相同;

当各子系统3单独使用时,各子系统3内部的时钟分频模块31的输入定义为创建时钟;

当各子系统3在时钟分频系统中时,将各子系统3内部的时钟分频模块31的输入省略,并将预分频模块2的至少一个输出定义为创建子时钟;

创建子时钟是系统前级逻辑的停止点,同时作为系统后级逻辑的根节点。

可选的,绝对全局时钟生成模块1的至少一个输出,与预分频模块2的至少一个输入功能相同;

当预分频模块2单独使用时,预分频模块2的至少一个输入定义为创建时钟;

当预分频模块2在所述时钟分频系统中时,将预分频模块2的至少一个输入省略,并将绝对全局时钟生成模块1的至少一个输出定义为创建子时钟;

创建子时钟是系统前级逻辑的停止点,同时作为系统后级逻辑的根节点。

上述两个可选的实施例中,提供了基于图1d所示的时钟结构应用示例的相关时钟约束和时钟树综合的规则,具体为,3-1-*相关的时钟(表示图1d中名称开头为3-1的时钟,下述包含符号*的时钟名称的表示同理),即各子系统3中包含的时钟分频模块31生成的时钟定义为创建子时钟(Create_Generate_Clock)且无需同步,对下级逻辑(例如,当前子系统的下一级子系统)来说是时钟树综合的根节点(root点),对前级逻辑(例如,当前子系统)来说是停止点(stop pin点)。

3-0-*相关的时钟和2-1-*相关的时钟功能对等,其中,3-0-*是时钟分频模块31的输入时钟,2-1-*是预分频模块2输出的时钟,当各子系统3单独使用时,各子系统3内部的时钟分频模块31的输入(即3-0-*)定义为创建时钟(Create clock),当各子系统3在时钟分频系统中时,则可以将时钟分频模块31的输入(即3-0-*)的定义省略,将预分频模块2的至少一个输出(即2-1-*)定义为创建子时钟(Create_Generate_Clock)且无需同步。

与上述介绍同理,2-0-*相关的时钟和1-1-*相关的时钟功能对等,其中,2-0-*是预分频模块2的输入时钟,1-1-*是绝对全局时钟生成模块1的输出时钟,当预分频模块2单独使用时,将预分频模块2的至少一个输入(即2-0-*)定义为创建时钟(Create clock),当预分频模块2在时钟分频系统中时,则可以将预分频模块2的输入(即2-0-*)的定义省略,将绝对全局时钟生成模块1的至少一个输出(即1-1-*)定义为创建子时钟(Create_Generate_Clock)且无需同步。

另外,各层次输出的时钟均为异步,例如,1-1-*,2-1-*和3-1-*输出的时钟均为异步时钟。

实施例二

图2为本发明实施例二中的一种时钟分频方法的流程图,本实施例的技术方案适用于将复杂的SOC时钟网络切分到各功能模块中的情况,该方法可以由时钟分频系统执行。下面结合图2对本发明实施例二提供的一种时钟分频方法进行说明,包括以下步骤:

步骤210、绝对全局时钟生成模块根据外部参考时钟生成绝对全局时钟,并将绝对全局时钟发送至预分频模块。

本实施例中,将外部参考时钟通过功能管脚输入到系统内部的绝对全局时钟生成模块,由绝对全局时钟生成模块根据外部参考时钟,生成系统所需的绝对全局时钟,并将绝对全局时钟生成模块产生的绝对全局时钟发送至预分频模块。

步骤220、预分频模块根据绝对全局时钟,生成与各子系统分别对应的相对全局时钟,并将各相对全局时钟下发至匹配的子系统中的时钟分频模块。

本实施例中,为了避免时钟远距离传输造成的功耗较大的问题,在时钟分频系统中引入预分频模块,预分频模块在接收到绝对全局时钟生成模块发送的绝对全局时钟后,根据各子系统所需的时钟频率,对绝对全局时钟进行分频,生成与各子系统分别对应的相对全局时钟,并将各相对全局时钟下发至匹配的子系统中的时钟分频模块。

可选的,预分频模块输出的至少一个相对全局时钟均为异步时钟。

本可选的实施例中提供了一种约束规则,预分频模块输出的至少一个相对全局时钟均为异步时钟。示例性的,预分频模块产生的各时钟命分别名为*gmc_125M,*dma_125M,*SD0_96M以及*SD1_96M,各时钟均为异步,与预分频模块相连的各子系统的时钟输入端口不能同时存在同步的个相对全局时钟,如果是个同步时钟则需要合并,以保证输入至一个子系统的时钟都是异步。

步骤230、时钟分频模块根据从预分频模块处获取的相对全局时钟,生成至少一个同步时钟;

其中,同步时钟用于提供至子系统的本级或下一级电子模块。

本实施例中,时钟分频模块在接收到预分频模块发送的相对全局时钟后,根据每个相对全局时钟,生成至少一个同步时钟,其中,同步时钟用于提供至子系统的本级或下一级电子模块,电子模块是时钟分频系统中最底层单位。

示例性的,时钟分频模块接收到预分频模块发送的2个相对全局时钟,分别为*gmc_125M和*dma_125M,时钟分频模块可以根据相对全局时钟*gmc_125M,生成多个同步时钟,例如,生成2个同步时钟,分别为*gmc_125M和*gmc_62.5M;也可以根据相对全局时钟*dma_125M,生成多个同步时钟,例如,生成2个同步时钟,分别为*dma_125M和*dma_62.5M,上述由时钟分频模块生成的同步时钟用于提供至与子系统相连的下一级电子模块,以为电子模块提供与其工作频率匹配的时钟。

本发明实施例的技术方案,绝对全局时钟生成模块根据外部参考时钟生成绝对全局时钟并发送至预分频模块,预分频模块根据绝对全局时钟,生成与各子系统分别对应的相对全局时钟,并将各相对全局时钟下发至匹配的子系统中的时钟分频模块,最终时钟分频模块根据从预分频模块处获取的相对全局时钟,生成至少一个同步时钟,用于提供至子系统的本级或下一级电子模块,解决了现有技术中使用分散的分频电路模块或单一的时钟分频电路模块容易导致时钟关系混乱、时钟约束复杂,影响时钟树综合质量的问题,采用多层次时钟专用模块将复杂的SOC时钟网络结构进行层次化、规范化处理。

实施例三

图3为本发明实施例三中的一种电子设备的结构示意图,如图3所示,该电子设备包括任意实施例所提供的时钟分频系统30,时钟分频系统30包括绝对全局时钟生成模块1、预分频模块2以及至少一个子系统3,每个子系统3中包括时钟分频模块31;绝对全局时钟生成模块1与预分频模块2相连,预分频模块2分别与各子系统3中的时钟分频模块31相连。

可选的,该电子设备还包括多个电子模块4,每个子系统3中包括的时钟分频模块31,与至少一个电子模块4相连。

所述绝对全局时钟生成模块1,用于生成绝对全局时钟发送至预分频模块2;

所述预分频模块2,用于根据所述绝对全局时钟,生成与各子系统3分别对应的相对全局时钟,并将各相对全局时钟下发至匹配的子系统3中的时钟分频模块31;

所述时钟分频模块31,用于根据从预分频模块2处获取的相对全局时钟,生成至少一个同步时钟;

其中,所述同步时钟用于提供至所述子系统3的下一级电子模块4。

本发明实施例的技术方案,绝对全局时钟生成模块根据外部参考时钟生成绝对全局时钟并发送至预分频模块,预分频模块根据绝对全局时钟,生成与各子系统分别对应的相对全局时钟,并将各相对全局时钟下发至匹配的子系统中的时钟分频模块,最终时钟分频模块根据从预分频模块处获取的相对全局时钟,生成至少一个同步时钟,用于提供至子系统的本级或下一级电子模块,解决了现有技术中使用分散的分频电路模块或单一的时钟分频电路模块容易导致时钟关系混乱、时钟约束复杂,影响时钟树综合质量的问题,采用多层次时钟专用模块将复杂的SOC时钟网络结构进行层次化、规范化处理。

注意,上述仅为本发明的较佳实施例及所运用技术原理。本领域技术人员会理解,本发明不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整和替代而不会脱离本发明的保护范围。因此,虽然通过以上实施例对本发明进行了较为详细的说明,但是本发明不仅仅限于以上实施例,在不脱离本发明构思的情况下,还可以包括更多其它等效实施例,而本发明的范围由所附的权利要求范围决定。

- 跨时钟域分频时钟保护电路、分频电路、方法及终端设备

- 一种时钟分频系统、方法及设备