半导体封装元件、射频晶体管用基底基板及其制造方法

文献发布时间:2023-06-19 12:02:28

技术领域

本发明涉及一种半导体封装元件、射频晶体管用基底基板及其制造方法。更为详细地,涉及一种形成有凸起部的射频晶体管用基底基板及其制造方法。更为详细地,涉及一种半导体封装元件、射频晶体管用基底基板及其制造方法,将模具芯片和引线框架通过金属线连接,从而金属线的长度减少了与基底基板的凸出的高度一样多,可进行射频晶体管的阻抗匹配调节。

背景技术

半导体封装化的射频电力设备一般包括安装于基底上并安装于半导体封装内的模具芯片。射频输入信号通过从封装外部向封装内部延长的射频输入线提供至晶体管,射频输出信号通过从封装内部向外部延长的射频输出线从设备传递。

相关技术1中公开了一种电子射频装置及其制造方法,针对通过输入线和输出线的电信号,通过补偿晶体管的寄生电容的方法来控制运转带宽、电力效率等。

相关技术2中,封装化的射频晶体管设备包括耦合到射频晶体管单元的射频输入线、射频输出线及耦合的输出匹配网络。电容器的上部电容器极板耦合到射频晶体管单元的输出端子,在晶体管的基本操作频率下对晶体管的输入提供阻抗匹配。

相关技术3中公开了高频率半导体用基板及其制造方法,在高频率半导体中实质上以相同的形式构成使得引线框架和基板之间绝缘的绝缘体和热膨胀系数,同时热导率高,从而提高散热效果。

但是,就现有射频功率型晶体管用基底基板而言,金属基底形成为平板,在晶体管进行引线接合时阻抗匹配存在限制。因此,需要用于扩张射频带宽的开发。

以上的背景技术中记载的事项用于帮助对发明背景的理解,可包括不是该技术所属的领域内具有一般知识的人员已经知晓的现有技术的事项。

先行技术文献

(专利文献1)相关技术1:国际公开专利公告WO2006/097893

(专利文献2)相关技术2:韩国公开专利公告KR 2015-0039759

(专利文献3)相关技术3:韩国公开专利公告KR 2017-0008695

发明内容

本发明是为了解决上述的课题而考虑的,目的在于,提供一种半导体封装元件、射频晶体管用基底基板及其制造方法,在基底基板上安装模具芯片,基底基板形成有凸出部,在凸出部上安装模具芯片,将模具芯片和引线框架通过金属线连接,从而金属线的长度减少了与凸出的高度一样的多,进而可进行射频晶体管的阻抗匹配调节。

本发明提供一种半导体封装元件,作为半导体封装元件,其包括:基底基板;陶瓷层,其形成于基底基板的上部;引线框架,其形成于陶瓷层的上部;以及模具芯片(diechip),其安装于基底基板的上部;基底基板形成有凸出部,在凸出部上安装模具芯片,并将模具芯片和引线框架通过金属线连接。

本发明提供一种半导体封装元件的制造方法,作为半导体封装元件的制造方法,包括:第一步骤,形成陶瓷层,所述陶瓷层形成在基底基板的上部;第二步骤,形成引线框架,所述引线框架形成在陶瓷层的上部;以及第三步骤,在基底基板的上部安装模具芯片;基底基板形成有凸出部,在凸出部上安装模具芯片,将模具芯片和引线框架通过金属线连接。

此外,作为本发明的一个例子,提供一种半导体封装元件及其制造方法,其中,基底基板为金属基板。

此外,作为本发明的一个例子,提供一种半导体封装元件及其制造方法,其中,基底基板形成为多层结构。

此外,作为本发明的一个例子,提供一种半导体封装元件及其制造方法,其中,形成为多层结构的基底基板包括:第一铜层;铜-钼合金层,其形成于第一铜层上部;第二铜层,其形成于铜-钼合金层上。

此外,作为本发明的一个例子,提供一种半导体封装元件及其制造方法,其中,凸出部与基底基板为一体型。

此外,作为本发明的一个例子,提供一种半导体封装元件及其制造方法,其中,陶瓷层的高度为0.4mm至0.7mm。

此外,作为本发明的一个例子,提供一种半导体封装元件及其制造方法,其中,凸出部的高度为0.2mm至0.6mm。

此外,作为本发明的一个例子,提供一种半导体封装元件及其制造方法,其中,凸出部的高度比陶瓷层的高度低。

此外,作为本发明的一个例子,提供一种半导体封装元件及其制造方法,其中,当陶瓷层的高度为r,凸出部的高度为k时,r与k的比例为1:0.5至1:0.8。

此外,作为本发明的一个例子,提供一种半导体封装元件及其制造方法,其中,陶瓷层以包裹凸出部的外周的形态形成。

此外,作为本发明的一个例子,提供一种半导体封装元件及其制造方法,其中,凸出部的面积大于模具芯片的面积。

此外,作为本发明的一个例子,提供一种半导体封装元件及其制造方法,其中,凸出部不与陶瓷层接触。

然后,本发明提供一种射频晶体管用基底基板,作为由金属形成的射频晶体管用基底基板,其特征在于,在基底基板的一侧配备凸出部。

本发明的另一个例子中,提供一种射频晶体管用基底基板,其特征在于,基底基板以多层的形式形成。

本发明的另一个例子中,提供一种射频晶体管用基底基板,其特征在于,基底基板包括:基底中间层;第一金属层,其配备于基底中间层的一面;以及第二金属层,其配备于基底中间层的另一面。

本发明的另一个例子中,提供一种射频晶体管用基底基板,其特征在于,基底基板具有4~9ppm/℃的热膨胀率和140~240W/m·K的热导率。

本发明的另一个例子中,提供一种射频晶体管用基底基板,其特征在于,基底中间层为铜-钼合金层,第一金属层及第二金属层包括铜层。

本发明的另一个例子中,提供一种射频晶体管用基底基板,其特征在于,第一金属层和第二金属层具有金属熔化后再次硬化的熔化结构。

本发明的另一个例子中,提供一种射频晶体管用基底基板,其特征在于,凸出部与基底基板通过焊接形成或形成为一体型。

本发明提供一种射频晶体管用基底基板的制造方法,作为由金属形成的射频晶体管用基底基板的制造方法,其特征在于,在基底基板的一侧形成凸出部。

本发明的另一个例子中,提供一种射频晶体管用基底基板的制造方法,其特征在于,基底基板以多层的形式形成。

本发明的另一个例子中,提供一种射频晶体管用基底基板的制造方法,其特征在于,以多层的形式形成基底基板的步骤包括:准备基底中间层的步骤;以及形成金属层的步骤,在基底中间层的两面分别形成第一金属层和第二金属层。

本发明的另一个例子中,提供一种射频晶体管用基底基板的制造方法,其特征在于,基底基板具有4~9ppm/℃的热膨胀率和140~240W/m·K的热导率。

本发明的另一个例子中,提供一种射频晶体管用基底基板的制造方法,其特征在于,基底中间层为铜-钼合金层,第一金属层及第二金属层为铜层。

本发明的另一个例子中,提供一种射频晶体管用基底基板的制造方法,其特征在于,第一金属层和第二金属层形成金属熔化后再次硬化的熔化结构。

本发明的另一个例子中,提供一种射频晶体管用基底基板的制造方法,其特征在于,凸出部与基底基板通过焊接形成或形成为一体型。

本发明的另一个例子中,提供一种射频晶体管用基底基板的制造方法,其特征在于,凸出部通过端铣刀加工而形成。

本发明的另一个例子中,提供一种射频晶体管用基底基板的制造方法,其特征在于,凸出部通过压力加工而形成。

根据本发明,效果在于,在半导体封装元件中将模具芯片和引线框架通过金属线连接的时候,金属线的长度减少了与基底基板的凸出的高度一样多,从而可进行射频晶体管的阻抗匹配调节,且射频晶体管的热导率、热膨胀系数、信赖性等优秀。

附图说明

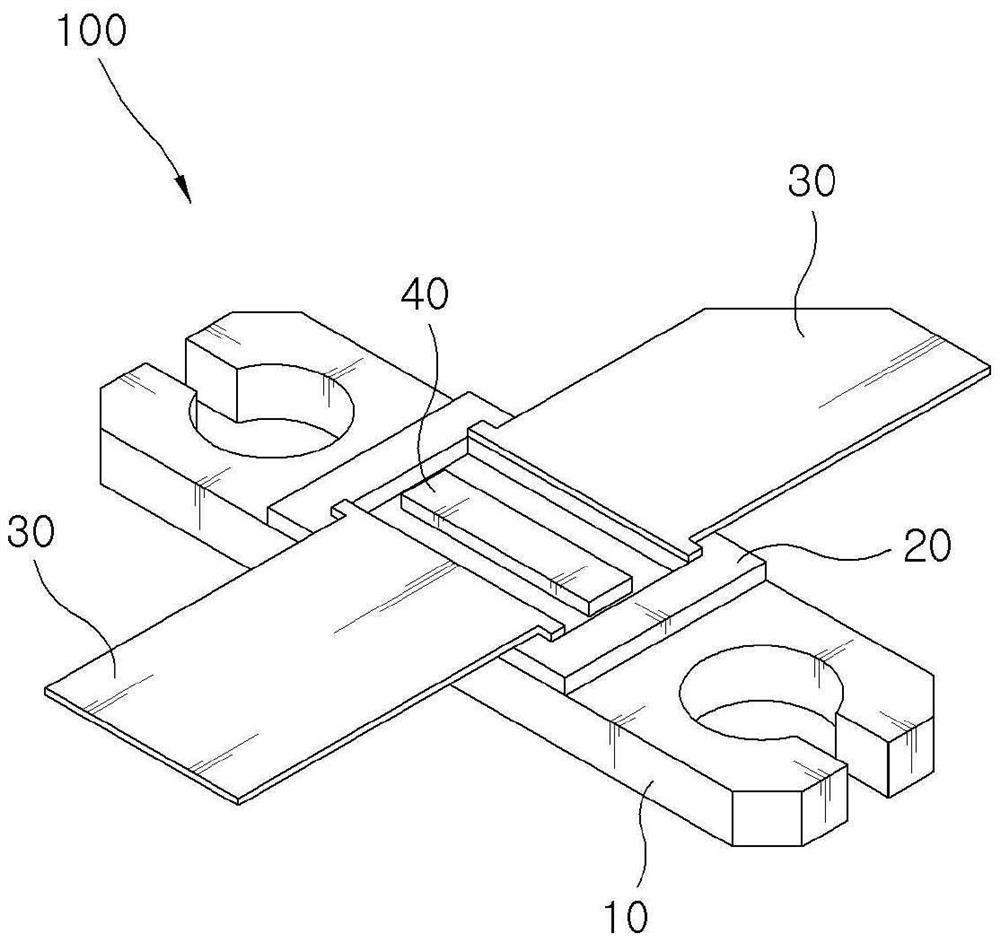

图1表示本发明的半导体封装元件。

图2表示本发明的基底基板。

图3表示半导体封装元件的截面图。

图4表示本发明的基底基板的制造例。

图5表示本发明的基底基板的另一个制造例。

标号说明

10:基底基板

11:第二金属层

12:基底中间层

13:第一金属层

20:陶瓷层

30:引线框架

40:凸出部

50:模具芯片

60:金属线

具体实施方式

为了充分地理解本发明和本发明的操作上的优点及通过本发明的实施实现的目的,应参照例示本发明的优选实施例的附图及附图上记载的内容。

就说明本发明的优选实施例而言,对可能会不必要地混淆本发明的要旨的公知的技术或反复的说明,减少或省略其说明。

图1表示本发明的半导体封装元件。如图1所示,本发明的半导体封装元件100可包括:基底基板10;陶瓷层20,其形成于基底基板10的上部;引线框架30,其形成于陶瓷层20的上部。此外,本发明的半导体封装元件100中,基底基板10上部可形成有凸出部40。

图2表示本发明的基底基板的一个例子。基底基板10可使用金属基板。基底基板铸造铜(Cu)、银(Ag)、铝(Al)、镍(Ni)、锡(Sn)、钼(Mo)中任意一个,从而可制造基板,也可混合这些合金或其他的金属并使用。例如,可使用诸如TiCu、NiTi、TiCu、NiNb、CuMo、TiAg的合金。

如图2(a)所示,基底基板10可使用单层结构10A,此外可使用以多层的形式形成的结构。多层结构的情况,可使用2层或3层以上,如图2(b)所示,可使用3层结构11、12、13。

基底基板10可包括:基底中间层12;第一金属层11,其配备于基底中间层12的一面;第二金属层13,其配备于基底中间层12的另一面。

基底中间层12的材料可使用铜(Cu)、铝(Al)、银(Ag)、金(Au)、钼(Mo)中任意一个或这些合金,第一金属层11及第二金属层13可使用铜(Cu)、铝(Al)、银(Ag)、金(Au)、钼(Mo)中任意一个或这些合金,优选地,第一金属层11及第二金属层13互相种类相同。尤其,基底中间层12为铜-钼合金层,第一金属层11及第二金属层13形成铜层,从而效果在于,基底基板10的热膨胀系数变小,提高热导率。

此外,优选地,第一金属层11及第二金属层13的热膨胀率比基底中间层12的热膨胀率小,第一金属层11及第二金属层13的热导率比基底中间层12的热导率低。即,优选地,第一金属层11及第二金属层13用热膨胀率和热导率比基底中间层12的热膨胀率和热导率小的金属分别叠层在基底中间层12的两面而形成。

具有多层结构的基底基板10作为用于满足特定膨胀率的金属基板,以具有4~9ppm/℃的热膨胀率的金属基板为例,此外,根据本发明的具有多层结构的金属基板作为用于满足特定热膨胀率和热导率的基底基板10,以具有140~240W/m·K的热导率的金属基板为例。

例如,第一金属层11及第二金属层13通过金属膜而钎焊接合在基底中间层12上。例如,第一金属层11及第二金属层13可通过使用金属膜而接合基底中间层12,也可使用蒸镀层进行钎焊接合。第一金属层11及第二金属层13可具有金属熔化后再次硬化的熔化结构。

本发明的陶瓷层20可使用ZTA(Zirconia ToughenedAlumina,氧化锆增韧氧化铝)、氮化铝(AlN)、氧化铝(Al

陶瓷层20根据组成比以具有0.4mm至0.7mm厚度的形式形成。此时,为了增强和基底基板10的接合力,陶瓷层20也可通过化学药品或物理研磨在表面形成有细微凸起部。

陶瓷层20可以形成为包裹凸出部40的外周的形态。根据半导体封装元件的设计可形成为圆形、椭圆形、四边形、五边形等多边形的形态。

本发明的凸出部40可位于基底基板10的中心部。可将凸出部40通过焊接等接合在基底基板10的上部并使用。

或者,也可将凸出部40和基底基板10加工为一体型。例如,第二金属层13和凸出部40也可加工为一体型。凸出部40和基底基板10为一体型的情况,优点在于,省略将凸出部40和基底基板10接合的工艺,从而提高工艺效率,也可减少由于焊接等产生的误差。

如图2(a)及2(b)所示,凸出部40可具有直四面体的形状。或可具有圆筒形的形状,根据半导体设计可适当地使用。

图3(a)表示基底基板为单层结构的半导体封装元件的截面图,图3(b)表示基底基板为多层结构的半导体封装元件的截面图。

图3(a)及图3(b)中示出了凸出部40的面积与模具芯片50的面积相同,但凸出部40的面积也可以大于模具芯片50的面积。在模具芯片50稳定地附着在凸出部40并可以减少对齐误差的方面,更为优选地,凸出部40的面积大于模具芯片50的面积。但是,凸出部40和陶瓷层20接触的情况容易产生短路,因此,优选地,凸出部40不与陶瓷层20接触。

考虑到与陶瓷层20的高度差,凸出部40的高度可形成为具有0.2mm至0.6mm的厚度。更为优选地,可形成为具有0.3mm至0.5mm的厚度。此时,优选地,凸出部40的高度以比陶瓷层20的高度低的形式形成。例如,当陶瓷层20的高度为r,凸出部40的高度为k时,r与k的比例可使用1:0.5~1:0.8。更为优选地,r与k的比例使用1:0.6~1:0.7。r与k的比例不足0.5的情况,在进行晶体管的引线接合时阻抗匹配的效果不足,r与k的比例超过0.8的情况,产生金属线短路的可能性可能变高。

金属线60将模具芯片50与引线框架30电连接,可使用在白金、金、银、铜等中选择的任意一种或两种以上的合金。

在图3(a)及图3(b)中,示出了一个金属线60连接模具芯片50和引线框架30,射频输入信号可通过从半导体封装元件的外部向半导体封装元件的内部延长的射频输入引线框架提供至晶体管,射频输出信号可通过从半导体封装元件内部向外部延长的射频输出引线框架从设备传递。

本发明的半导体封装可包括陶瓷盖(未示出),其保护半导体封装元件100。此外,本发明的半导体封装可用于射频晶体管。射频电力晶体管可以是例如MOSFET(metal-oxidesemiconductor field-effect transistor,金属氧化物半导体场效应晶体管)、LDMOST(lateral diffusedmetal-oxide semiconductor transistor,横向扩散金属氧化物半导体晶体管)、BJT(bipolarjunction transistor,双极面结型晶体管)、JFET(junctionfield-effect transistor,结型场效应晶体管)或HBT(heterojunction bipolartransistor,异质结双极性晶体管)等任意种类的晶体管。使用射频电力晶体管可在电子射频装置生成射频电力。

下面,参照图4通过本发明的基底基板的制造例进行说明。

可包括准备基底中间层的步骤S100。并且,以多层的形式形成基底基板的步骤,可包括:准备基底中间层的步骤;以及形成金属层的步骤S200,在基底中间层的两面分别形成第一金属层和第二金属层。

作为形成基底基板的方法的一个例子,还可包括蒸镀步骤S110,准备比基底中间层热膨胀率小的金属材料的第一金属膜和第二金属膜,在第一金属膜的一面和第二金属膜的一面分别形成分别用于钎焊接合的第一接合用蒸镀层和第二接合用蒸镀层。

并且,形成金属层的步骤S200可包括:在基底中间层的两面分别形成钎料层的过程S210及在基底金属基材的两面叠层并钎焊第一金属膜和第二金属膜的过程S220。

然后,本发明的凸出部可形成于基底基板的中心部S300。可以以通过焊接等接合在作为基底基板上部的第二金属层上的形式制造凸出部,或可以以与基底基板的第二金属层加工为一体型的形式制造凸出部。将凸出部与基底基板的第二金属层制造为一体型的情况,优点在于,省略将凸出部和基底基板的第二金属层接合的工艺,从而提高工艺效率,还可减少由于焊接等产生的误差。

为了将凸出部和基底基板的第二金属层制造为一体型,可以向配备有凹面部的模具倒入熔解的金属,从而在基底基板的第二金属层形成凸出部,也可以在平面形的基底基板的第二金属层中去除除凸出部区域以外的剩余部分来形成凸出部。例如,可使用端铣刀去除凸出部区域以外的部分。或者,在短时间内加工的方面,通过使用冲压等方法的压力加工形成凸出部的方法也是有利的。

在图5说明本发明的基底基板的其他制造例。

在准备基底中间层的步骤S100后,形成金属层的步骤S200可包括在熔融的金属熔融液内部浸渍基底中间层的过程S230、在金属熔融液中取出基底中间层并使其硬化的过程S240。然后在基底中间层的两面也可以分别形成有第一金属层和第二金属层。之后,本发明的凸出部可形成于基底基板的中心部S300。

本发明的射频晶体管用基底基板及其制造方法,可在例如MOSFET(metal-oxidesemiconductor field-effect transistor,金属氧化物半导体场效应晶体管)、LDMOST(lateral diffused metal-oxide semiconductor transistor,横向扩散金属氧化物半导体晶体管)、BJT(bipolar junction transistor,双极面结型晶体管)、JFET(junctionfield-effect transistor,结型场效应晶体管)或HBT(heterojunction bipolartransistor,异质结双极性晶体管)等任意种类的晶体管及其制造方法中使用,但不限定于此。

- 半导体封装元件、射频晶体管用基底基板及其制造方法

- 挠性装置用基板、挠性装置用薄膜晶体管基板、挠性装置、薄膜元件用基板、薄膜元件、薄膜晶体管、薄膜元件用基板的制造方法、薄膜元件的制造方法及薄膜晶体管的制造方法