一种基于多站串测的抽测方法及系统

文献发布时间:2023-06-19 10:32:14

技术领域

本发明涉及射频芯片测试技术领域,尤其涉及一种基于多站串测的抽测方法及系统。

背景技术

QA即Quality Assurance,质量保证。为提高射频芯片测试机的测试结果的准确性,一批测试合格的芯片需要再抽出一部分重新测试,若两次测试结果相同则表明测试机测试结果准确。

现有的QA测试多应用于单站测试和多站并测,因为这两者的核心是一样的,常规测试完成后即可知道当前测试芯片的测试结果。具体表现为,以单站测试为例,累计(n-1)颗芯片测试合格后,该站常规测试完第n颗芯片,若该芯片测试合格,则可直接继续做QA测试,若不合格则进行下一个芯片的测试,直至测到第n颗合格的芯片,然后再进行QA测试。但是如果测试模式采用的是双站串测,一颗芯片的测试合格与否涉及到所有站的测试结果。那么及时预判就显得尤为重要了。

例如,中国专利CN110665845A公开了一种堆栈式芯片硅基质量检测装置,包括底端四角安装有支撑杆的输送平台,所述输送平台上安装有传动模组、图像采集结构、带有单片机的图像处理设备以及用于不合格产品筛选的剔除模组,所述输送平台为阶梯式结构,其上分别开设有芯片传送槽和设备传动槽,所述输送平台上安装的传动模组包括安装于芯片传送槽侧面的输送电机和安装于设备传动槽内的伺服电机,所述芯片传送槽内安装有一组配合输送电机的传送带,芯片传送槽内设置有一组配合伺服电机安装的传动丝杠,且传动丝杠远离伺服电机的一端与输送平台之间通过滚子轴承配合。但是,该堆栈式芯片硅基质量检测装置只能用于单站检测,无法用于多站串测,并且检测效率也不高效。

当前,现有技术还没有在多站并测的背景下提供一种能够预判测试结果的抽测方法。

此外,一方面由于对本领域技术人员的理解存在差异;另一方面由于发明人做出本发明时研究了大量文献和专利,但篇幅所限并未详细罗列所有的细节与内容,然而这绝非本发明不具备这些现有技术的特征,相反本发明已经具备现有技术的所有特征,而且申请人保留在背景技术中增加相关现有技术之权利。

发明内容

针对现有技术之不足,本发明提供一种基于多站串测的抽测方法,所述方法至少包括:在至少两个测试站对芯片进行不同的常规测试的情况下,在合格的芯片数量达到抽测指数时,与抽测指数对应的各个所述测试站对当前在测芯片进行质量测试。

优选地,所述方法还包括:所述抽测指数的确定方式为,m=n-a+b,

其中,m表示抽测指数,n表示一轮测试芯片的数量;a表示测试站的数量;b表示测试站的序号。

优选地,所述方法还包括:在合格的芯片的数量达到一轮测试芯片的数量时,

第n颗合格芯片重新进行一次质量测试。

优选地,所述方法还包括:在合格的芯片数量达到抽测指数时,各个所述测试站对后续进行常规测试的芯片进行质量测试。

优选地,所述方法还包括:在最后一个测试站的一轮测试中的最后一个芯片的常规测试和/或质量测试完成后,

第一测试站将新一轮中的芯片的质量测试数据删除。

优选地,所述方法还包括:在其中一个测试站的一个芯片的常规测试不合格时,在常规测试不合格的测试站的测试顺序之前的测试站将同一芯片的质量测试数据删除。

优选地,所述方法还包括:在测试不合格的芯片的质量测试数据删除后,至少两个测试站继续对后续的芯片进行常规测试和/或质量测试,直至芯片合格的数量达到一轮测试芯片的数量。

本发明还提供一种基于多站串测的抽测系统,所述系统至包括至少一个测试站和控制单元,至少两个测试站对芯片进行不同的常规测试,在合格的芯片数量达到抽测指数时,所述控制单元指示与抽测指数对应的各个所述测试站对当前在测芯片进行质量测试。

优选地,所述控制单元确定所述抽测指数的方式为,m=n-a+b,

其中,m表示抽测指数,n表示一轮测试芯片的数量;a表示测试站的数量;b表示测试站的序号。

优选地,在合格的芯片的数量达到一轮测试芯片的数量时,所述控制单元指示第一测试站对第n颗合格芯片重新进行一次质量测试。

本发明的有益技术效果:

本发明通过设置抽测指数来对对应的芯片进行抽测质量,使得不同测试站的同一芯片的质量测试数据能够互相关联,在其中一项不合格时,其他测试站的对应的芯片的质量测试数据同步删除,从而提高了一轮芯片测试中的芯片测试质量,实现了高效的芯片质量测试,节约了时间。

附图说明

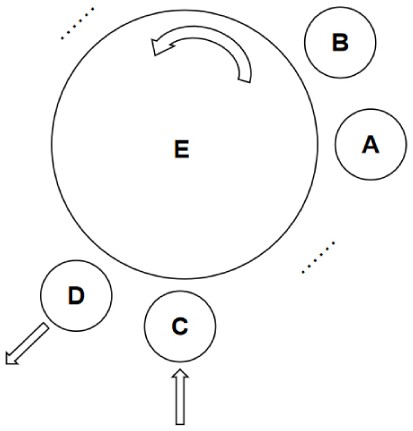

图1是本发明的基于多站串测的分选机的结构示意图。

具体实施方式

下面结合附图进行详细说明。

本发明的应用场景是多站串测。多站串测是指一颗芯片在多个不同的站点测试不同的测项,当且仅当所有站的测试结果均为合格,该芯片的测试结果才算合格。

本发明中,一轮芯片测试结束是指累计n颗芯片测试合格,第n颗合格芯片完成所有测试站的质量测试。一轮芯片测试结束也可以称为一组芯片测试结束。

本发明中,合格的芯片是指在各个测试站的常规测试均合格的芯片。

本发明中,常规测试是指:射频芯片出厂前进行的一些比较常规的功能测试,一般包含射频类测试和直流类测试,射频类测试(即RF测试)包含S参数,增益,损耗等测项;直流类测试(即DC测试)包含工作电压,工作电流,泄露电流等测项。

本发明中,质量测试是指:QA(Quality Assurance)测试。为提高射频芯片测试机的测试结果的准确性,将一批测试合格的芯片需要再抽出一部分重新测试,若两次测试结果相同则表明测试机的质量测试结果准确。

实施例1

针对现有技术之不足,本发明提供一种基于多站串测的抽测方法,所述方法至少包括:在至少两个测试站对芯片进行不同的常规测试的情况下,在合格的芯片数量达到抽测指数时,各个所述测试站对当前进行常规测试的芯片进行质量测试。

抽测指数的确定方式为,m=n-a+b。其中,m表示抽测指数,n表示一轮测试芯片的数量;a表示测试站的数量;b表示测试站的序号。

当有m个芯片测试合格,测试站正在测试的芯片在进行常规测试后,继续进行质量测试,直到一轮结束。

例如,最常见的测试站数量为2。测试站分别为第一测试站site0,第二测试站site1。0和1分别就是第一测试站和第二测试站的序号。若n为5,对于测试系统,当前累计已有3个芯片测试合格,则测试站的芯片在进行常规测试后,继续进行质量测试,直到一轮芯片测试结束。

本发明以设置两个测试站为例来对本发明进行具体说明。

如图1所示,基于多站串测的分选机E中,C为上料口,D为下料口。芯片从上料口C进入,单颗进行测试,直到测试完毕从下料口D出来。

图1表示的是双站串测,A可以表示为第一测试站site0,B可以表示为第二测试站site1。即,当A在测第x个芯片的时候,B正在测第(x-1)颗芯片。

优选地,在合格的芯片的数量达到一轮测试芯片的数量时,第n颗合格芯片重新进行一次质量测试。

例如,以n=5为例,测试逻辑则为每测试完5颗合格的芯片时,第5颗合格芯片重新再测试一遍。

第一测试站site0:m=5-2+0=3,表示芯片整体已经测试完3个合格的芯片时,第一测试站site0要开始对当前在测芯片做质量测试。

第二测试站site1:m=5-2+1=4, 表示芯片整体已经测试完4个合格的芯片时,第二测试站要开始对当前在测芯片做质量测试。

表1:简易的双站串测的芯片测试记录。

如表1所示,第一颗芯片的测试数据直接简化成其序号,2就表示第2颗芯片的测试数据。芯片先在第一测试站site0上进行DC测试,再转到第二测试站site1进行RF测试。表1的数据记录就如阶梯状所示。最后一列的pass为1表示芯片常规测试合格,为0表示不合格。

表1没有完整的表现出抽测的逻辑,只是一种测试结果的静态呈现。后续的表2~表9的示例能够展现出测试数据的变化过程。从表1看到,第3颗芯片测试成功后,满足累计有3颗芯片测试成功的条件,此时第一测试站site0正在测第5颗芯片,第二测试站site1正在测第4颗芯片。

第一示例:

优选地,所述方法还包括:在合格的芯片数量达到抽测指数时,各个所述测试站对后续进行常规测试的芯片进行质量测试。

例如:在第一测试站site0常规测试第5颗芯片合格时,继续对第5颗芯片进行质量测试,第二测试站site1常规测试第4颗芯片合格。

优选地,在最后一个测试站的一轮测试中的最后一个芯片的常规测试和/或质量测试完成后,第一测试站将新一轮中的芯片的质量测试数据删除。

例如,如表2所示,第一测试站site0常规测试第6颗芯片,继续第6颗芯片的质量测试,第二测试站site1常规测试第5颗芯片合格,继续第5颗芯片的质量测试。此时,第一测试站site0中的第6颗芯片的质量测试数据自动删除。

此时,一轮芯片测试结束。

表2:第n颗芯片质量合格示例

第二示例:

优选地,在其中一个测试站的一个芯片的常规测试不合格时,在常规测试不合格的测试站的测试顺序之前的测试站将在测芯片的质量测试数据删除。

表3:第二测试站的第4颗芯片测试不合格示例

如表3所示,第一测试站site0常规测试第5颗芯片合格,继续第5颗芯片的质量测试,第二测试站site1常规测试第4颗芯片不合格。第5颗芯片在第一测试站site0上的质量测试数据自动删除。

表4:第六颗芯片的测试记录结果

如表4所示,第一测试站site0常规测试第6颗芯片合格,继续第6颗芯片的质量测试,第二测试站site1常规测试第5颗芯片合格。

表5:一轮芯片测试结果记录

优选地,在测试不合格的芯片的质量测试数据删除后,至少两个测试站继续对后续的芯片进行常规测试和/或质量测试,直至芯片合格的数量达到一轮测试芯片的数量。

如表5所示,第一测试站site0常规测试第7颗芯片合格,继续第7颗芯片的质量测试。第二测试站site1常规测试第6颗芯片合格,继续第6颗芯片的质量测试。

表6:一轮芯片测试结束的记录结果

在第6颗芯片的常规测试合格后,累计合格芯片的数量达到5颗,即一轮芯片测试结束。

如表6所示,在一轮芯片测试结束后,第7颗芯片在第一测试站site0上的质量测试数据自动删除。

表7:一轮芯片测试结束的最终记录结果

表8:一轮芯片测试结束的合格记录结果

一轮芯片测试结束的合格记录结果如表8所示。

第三示例:

表9:第一测试站第5颗芯片不合格的记录结果

如表9所示,第一测试站site0常规测试第5颗芯片不合格,第二测试站site1常规测试第4颗芯片合格。

第一测试站site0常规测试第6颗芯片合格,继续第6颗芯片的QA测试,第二测试站site1常规测试第5颗芯片合格。

第一测试站site0常规测试第7颗芯片合格,继续第7颗芯片的QA测试,第二测试站site1常规测试第6颗芯片合格,继续第6颗芯片的QA测试。第7颗芯片在第一测试站site0上的QA测试数据自动删除。

一轮芯片测试结束。

实施例2

本实施例是对实施例1的进一步改进,重复的内容不再赘述。

本发明还提供一种基于多站串测的抽测系统,用于执行本发明的基于多站串测的抽测方法。

基于多站串测的抽测系统包括至少一个测试站和控制单元。至少两个测试站对芯片进行不同的常规测试,在合格的芯片数量达到抽测指数时,所述控制单元指示各个所述测试站对当前进行常规测试的芯片进行质量测试。

控制单元可以是专用集成芯片、服务器、计算机中的一种或几种。

优选地,所述控制单元确定所述抽测指数的方式为,m=n-a+b。其中,m表示抽测指数,n表示一轮测试芯片的数量;a表示测试站的数量;b表示测试站的序号。

优选地,在合格的芯片的数量达到一轮测试芯片的数量时,所述控制单元指示第一测试站对第n颗合格芯片重新进行一次质量测试。

优选地,在合格的芯片数量达到抽测指数时,控制单元指示与抽测指数对应的各个所述测试站对后续进行常规测试的芯片进行质量测试。

优选地,在最后一个测试站的一轮测试中的最后一个芯片的常规测试和/或质量测试完成后,控制单元指示第一测试站将新一轮中的芯片的质量测试数据删除。

优选地,在其中一个测试站的一个芯片的常规测试不合格时,在常规测试不合格的测试站的测试顺序之前的测试站将同一芯片的质量测试数据删除。

优选地,在测试不合格的芯片的质量测试数据删除后,至少两个测试站继续对后续的芯片进行常规测试和/或质量测试,直至芯片合格的数量达到一轮测试芯片的数量。

本发明的基于多站串测的抽测系统,各个测试站能够基于对应的抽测指数对芯片进行质量测试,从而使得芯片能够在常规测试进行的过程中得到合格结果,而不是在全部常规测试完成后才知晓其合格结果,从而节约了大量的测试时间,提高了质量测试的效率。

需要注意的是,上述具体实施例是示例性的,本领域技术人员可以在本发明公开内容的启发下想出各种解决方案,而这些解决方案也都属于本发明的公开范围并落入本发明的保护范围之内。本领域技术人员应该明白,本发明说明书及其附图均为说明性而并非构成对权利要求的限制。本发明的保护范围由权利要求及其等同物限定。

本发明说明书包含多项发明构思,申请人保留根据每项发明构思提出分案申请的权利。本发明说明书包含多项发明构思,诸如“优选地”、“根据一个优选实施方式”或“可选地”均表示相应段落公开了一个独立的构思,申请人保留根据每项发明构思提出分案申请的权利。

- 一种基于多站串测的抽测方法及系统

- 一种基于串测数据拼接异常的处理方法及系统