具有高阶温度补偿的带隙基准电压生成电路

文献发布时间:2023-06-19 11:22:42

技术领域

本申请涉及一种集成电路技术领域,更涉及一种具有高阶温度补偿的带隙基准电压生成电路。

背景技术

许多电子电路,例如模数转换器、数模转换器和DC-DC转换器,都需要稳定且准确的参考电压才能有效运行。

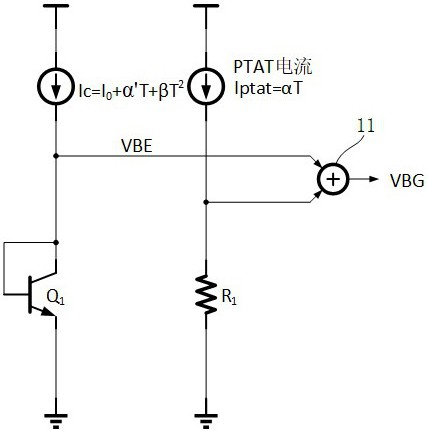

参考图1所示,生成对温度不敏感的参考电压的常规方法是将具有负温度系数的双极型晶体管(BJT)的基极-发射极电压(V

这样生成的参考压通常称为带隙基准电压(Bandgap Reference Voltage,BGR)V

发明内容

本申请的目的在于提供一种具有高阶温度补偿的带隙基准电压生成电路,得到温度不敏感的带隙基准电压。

本申请公开了一种具有高阶温度补偿的带隙基准电压生成电路,包括:

第一电流源,所述第一电流源与温度线性相关,其相关系数为α

第二电流源,所述第二电流源包括与温度二阶相关的电流项,其相关系数为β,所述第二电流源通过第一双极型晶体管生成第二电压;

加法器,所述加法器根据所述第一电压和第二电压生成与温度无关的带隙基准电压。

在一个优选例中,所述第二电流源还包括与温度线性相关的电流项和与温度无关的电流项,该与温度线性相关的电流项的相关系数为α

在一个优选例中,还包括:电流平方电路,用于生成所述与温度二阶相关的电流项,所述电流平方电路包括:第三至第七电流源,第一至第五NMOS晶体管,第一和第二PMOS晶体管,及第二至第五双极型晶体管,其中,

所述第三电流源与温度线性相关,其相关系数为α

所述第四电流源与温度线性相关,其相关系数为α

所述第五电流源与温度无关;

所述第二双极型晶体管的集电极连接所述第三电流源和所述第一NMOS晶体管的栅极,发射极连接地端,基极连接所述第三NMOS晶体管的漏极和所述第三双极型晶体管的发射极;

所述第三双极型晶体管的集电极连接所述第四电流源和所述第二NMOS晶体管的栅极,基极连接所述第四双极型晶体管的基极和所述第一NMOS晶体管的源极;

所述第四双极型晶体管的集电极连接所述电源端,发射极连接所述第五电流源和所述第五双极型晶体管的基极;

所述第五双极型晶体管的集电极连接所述第一PMOS晶体管的漏极,发射极连接地端;

所述第六电流源连接所述第三和第四双极型晶体管的基极,及所述第一NMOS晶体管的源极;

所述第一NMOS晶体管的漏极连接所述电源端;

所述第二NMOS晶体管的漏极连接所述电源端,源极连接所述第三NMOS晶体管的栅极和所述第四NMOS晶体管的漏极;

所述第三NMOS晶体管的源极连接地端;

所述第四NMOS晶体管的栅极连接所述第五NMOS晶体管的栅极和漏极,源极连接地端;

所述第五NMOS晶体管的漏极连接第七电流源,源极连接地端;

所述第一和第二PMOS晶体管的源极连接所述电源端,所述第一和第二PMOS晶体管的栅极相连,其中,所述第二PMOS晶体管和所述第一PMOS晶体管之间的比例系数为K,所述第二PMOS晶体管的漏极电流为所述与温度二阶相关的电流项;

其中,通过调节所述相关系数为α

在一个优选例中,还包括:电流平方电路,用于生成所述与温度二阶相关的电流项,所述电流平方电路包括:第三至第五电流源,第一NMOS晶体管,第一和第二PMOS晶体管,及第二至第五双极型晶体管,其中,

所述第三电流源与温度线性相关,其相关系数为α

所述第四电流源与温度无关;

所述第三双极型晶体管的集电极连接所述第三电流源,发射极连接所述第二双极型晶体管的集电极,基极连接所述第四双极型晶体管的基极;

所述第四双极型晶体管的集电极连接所述电源端,发射极连接所述第五电流源和所述第五双极型晶体管的基极;

所述第五双极型晶体管的集电极连接所述第一PMOS晶体管的漏极,发射极连接地端;

所述第一NMOS晶体管的栅极和漏极连接第五电流源,源极连接地端;

所述第一和第二PMOS晶体管的源极连接所述电源端,所述第一和第二PMOS晶体管的栅极相连,其中,所述第二PMOS晶体管和所述第一PMOS晶体管之间的比例系数为K,所述第二PMOS晶体管的漏极电流为所述与温度二阶相关的电流项;

其中,通过调节所述相关系数为α

在一个优选例中,还包括:电流平方电路,用于生成所述与温度二阶相关的电流项,所述电流平方电路包括:第三至第七电流源,第一至第八NMOS晶体管,第一和第二PMOS晶体管,及第二至第五双极型晶体管,其中,

所述第三电流源与温度线性相关,其相关系数为α

所述第四电流源与温度线性相关,其相关系数为α

所述第五电流源与温度无关;

所述第二双极型晶体管的集电极连接所述第三电流源和所述第一NMOS晶体管的栅极,发射极连接地端,基极连接所述第三NMOS晶体管的漏极和所述第三双极型晶体管的发射极;

所述第三双极型晶体管的集电极连接所述第四电流源和所述第二NMOS晶体管的栅极,基极连接所述第四双极型晶体管的基极和所述第一NMOS晶体管的源极;

所述第四双极型晶体管的集电极连接所述第五电源端和所述第六NMOS晶体管的栅极,发射极连接所述第七NMOS晶体管的漏极和所述第五双极型晶体管的基极;

所述第五双极型晶体管的集电极连接所述第一PMOS晶体管的漏极,发射极连接地端;

所述第六电流源连接所述第三和第四双极型晶体管的基极,及所述第一NMOS晶体管的源极;

所述第一NMOS晶体管的漏极连接所述电源端;

所述第二NMOS晶体管的漏极连接所述电源端,源极连接所述第三NMOS晶体管的栅极和所述第四NMOS晶体管的漏极;

所述第三NMOS晶体管的源极连接地端;

所述第四NMOS晶体管的栅极连接所述第五NMOS晶体管的栅极和漏极,源极连接地端;

所述第五NMOS晶体管的源极连接第六电流源,漏极连接地端;

所述第六NMOS晶体管的漏极连接所述电源端,源极连接所述第七NMOS晶体管的栅极和所述第八NMOS晶体管的漏极,所述第八NMOS晶体管的源极连接地端;

所述第一和第二PMOS晶体管的源极连接所述电源端,所述第一和第二PMOS晶体管的栅极相连,其中,所述第二PMOS晶体管和所述第一PMOS晶体管之间的比例系数为K,所述第二PMOS晶体管的漏极电流为所述与温度二阶相关的电流项;

其中,通过调节所述相关系数为α

在一个优选例中,所述加法器包括:第九至第十二NMOS晶体管,其中,

所述第九NMOS晶体管的栅极连接所述第二电流源和所述第一双极型晶体管的集电极连接,漏极连接所述第一电流源和所述第十NMOS晶体管的栅极,源极所述第一电阻的一端;

所述第一双极型晶体管的发射极连接地端,基极连接所述第一电阻的另一端和所述第十二NMOS晶体管的漏极;

所述第十NMOS晶体管的漏极连接电源端,源极连接所述第十一NMOS晶体管的漏极和所述第十二NMOS晶体管的栅极,所述第十一和第十二NMOS晶体管的源极连接地端;

其中,所述第九NMOS晶体管的源极输出所述与温度无关的带隙基准电压。

在一个优选例中,还包括:电流平方电路,用于生成所述与温度二阶相关的电流项,所述电流平方电路包括:第三至第七电流源,第一、第二、第四、第五、第六和第八NMOS晶体管,第一和第二PMOS晶体管,第二至第七双极型晶体管及第二和第三电阻,其中,所述第一NMOS晶体管、第二NMOS晶体管及第六NMOS晶体管为本征阈值晶体管,其中,

所述第三电流源与温度线性相关,其相关系数为α

所述第四电流源与温度线性相关,其相关系数为α

所述第五电流源与温度无关;

所述第二双极型晶体管的集电极连接所述第三电流源和所述第一NMOS晶体管的栅极,发射极连接地端,基极连接所述第六双极型晶体管的集电极和所述第三双极型晶体管的发射极;

所述第三双极型晶体管的集电极连接所述第四电流源和所述第二NMOS晶体管的栅极,基极连接所述第四双极型晶体管的基极和所述第一NMOS晶体管的源极;

所述第四双极型晶体管的集电极连接所述第五电源端和所述第六NMOS晶体管的栅极,发射极连接所述第七双极型晶体管的集电极和所述第五双极型晶体管的基极;

所述第五双极型晶体管的集电极连接所述第一PMOS晶体管的漏极,发射极连接地端;

第六双极型晶体管的发射极连接地端,基极连接所述第四NMOS晶体管的漏极和所述第二电阻的一端;

第七双极型晶体管的发射极连接地端,基极连接所述第八NMOS晶体管的漏极和所述第三电阻的一端;

所述第六电流源连接所述第三和第四双极型晶体管的基极,及所述第一NMOS晶体管的源极;

所述第一NMOS晶体管的漏极连接所述电源端;

所述第二NMOS晶体管的漏极连接所述电源端,源极连接所述第二电阻的另一端;

所述第四NMOS晶体管的栅极连接所述第五NMOS晶体管的栅极和漏极,源极连接地端;

所述第五NMOS晶体管的源极连接第六电流源,漏极连接地端;

所述第六NMOS晶体管的漏极连接所述电源端,源极连接所述第三电阻的另一端;

所述第八NMOS晶体管的源极连接地端;

所述第一和第二PMOS晶体管的源极连接所述电源端,所述第一和第二PMOS晶体管的栅极相连,其中,所述第二PMOS晶体管和所述第一PMOS晶体管之间的比例系数为K,所述第二PMOS晶体管的漏极电流为所述与温度二阶相关的电流项;

其中,通过调节所述相关系数为α

在一个优选例中,所述加法器包括:第九至第十NMOS晶体管,第八双极型晶体管,第八电流源及第四电阻,其中,所述第九至第十NMOS晶体管为本征阈值晶体管,其中,

所述第九NMOS晶体管的栅极连接所述第二电流源和所述第一双极型晶体管的集电极连接,漏极连接所述第一电流源和所述第十NMOS晶体管的栅极,源极所述第一电阻的一端;

所述第一双极型晶体管的发射极连接地端,基极连接所述第一电阻的另一端和所述第八双极型晶体管的集电极;

第十NMOS晶体管的漏极连接所述电源端,源极连接所述第四电阻的一端,所述第四电阻的另一端连接所述第一电流源,所述第八电流源和所述第八双极型晶体管的基极,所述第八电流源与温度无关;

其中,所述第九NMOS晶体管的源极输出所述与温度无关的带隙基准电压。

在一个优选例中,所述加法器包括:放大器和第九NMOS晶体管,其中,所述第九NMOS晶体管为本征阈值晶体管,其中,

所述放大器的同相输入端连接所述第二电流源,第一双极型晶体管的集电极和基极,反相输入端连接所述第一电流源的所述第一电阻的一端,所述第一双极型晶体管的发射极连接地端,所述放大器的输出端连接所述第九NMOS晶体管的栅极;

所述第九NMOS晶体管的漏极连接电源端,源极连接所述第一电阻的另一端;

其中,所述第九NMOS晶体管的源极输出所述与温度无关的带隙基准电压,并连接负载电流。

本申请可以采用具有高阶项的电流源

本说明书中记载了大量的技术特征,分布在各个技术方案中,如果要罗列出本申请所有可能的技术特征的组合(即技术方案)的话,会使得说明书过于冗长。为了避免这个问题,本说明书上述发明内容中公开的各个技术特征、在下文各个实施方式和例子中公开的各技术特征、以及附图中公开的各个技术特征,都可以自由地互相组合,从而构成各种新的技术方案(这些技术方案均应该视为在本说明书中已经记载),除非这种技术特征的组合在技术上是不可行的。例如,在一个例子中公开了特征A+B+C,在另一个例子中公开了特征A+B+D+E,而特征C和D是起到相同作用的等同技术手段,技术上只要择一使用即可,不可能同时采用,特征E技术上可以与特征C相组合,则,A+B+C+D的方案因技术不可行而应当不被视为已经记载,而A+B+C+E的方案应当视为已经被记载。

附图说明

图1是现有技术中带隙基准电压的生成原理图。

图2是参考图1中方法生成的带隙基准电压与温度的关系曲线。

图3是本申请一实施例中具有高阶温度补偿的带隙基准电压的生成原理图。

图4是本申请一实施例中具有高阶温度补偿的带隙基准电压电路的示意图。

图5是本申请一实施例中带隙基准电压的温度曲线。

图6是本申请另一实施例中具有高阶温度补偿的带隙基准电压电路的示意图。

图7是本申请另一实施例中具有高阶温度补偿的带隙基准电压电路的示意图。

图8是本申请另一实施例中具有高阶温度补偿的带隙基准电压电路的示意图。

图9是本申请另一实施例中具有高阶温度补偿的带隙基准电压电路的示意图。

图10本申请一实施例中生成与温度线性相关的电流I

具体实施方式

在以下的叙述中,为了使读者更好地理解本申请而提出了许多技术细节。但是,本领域的普通技术人员可以理解,即使没有这些技术细节和基于以下各实施方式的种种变化和修改,也可以实现本申请所要求保护的技术方案。

为使本申请的目的、技术方案和优点更加清楚,下面将结合附图对本申请的实施方式作进一步地详细描述。

本申请一实施方式中提供了一种具有高阶温度补偿的带隙基准电压生成电路,图3是一实施例中具有高阶温度补偿的带隙基准电压的生成原理图,该带隙基准电压的生成电路包括第一电流源I

第一电流源I

实施例一

图4示出了一实施例中带隙基准电压的生成电路的示意图。该带隙基准电压的生成电路包括第一电流源I

电流平方电路41包括第三电流源I

第三电流源I

第二双极型晶体管Q

第三双极型晶体管Q

第四双极型晶体管Q

第五双极型晶体管Q

第六电流源I

第一NMOS晶体管NM

第一PMOS晶体管PM

继续参考图4所示,电流平方电路41中有:

忽略双极型晶体管Q

根据第一PMOS晶体管PM

因此,第二电流源为:

第一双极型晶体管Q

继续参考图4所示,加法器42包括第九至第十二NMOS晶体管NM

第一电流源I

从上式可看出,通过调节相关系数为α

图5是本申请一实施例中带隙基准电压的温度曲线。从图中可以看出,温度从-40℃到150℃的变化范围内,带隙基准电压V

实施例二

本实施例中,电流平方电路61包括第三电流源I

第三电流源I

第三双极型晶体管Q

第一PMOS晶体管PM

本实施例中的带隙基准电压生成电路与实施例一基本相同,其主要区别在于:图4的电流平方电路中相关系数为α

由上文描述可知,第二电流源为:

高阶温度补偿的V

其中,通过调节相关系数为α

实施例三

本实施例中,电流平方电路71包括第三电流源I

当温度较高时,图4的电流平方电路中第五双极型晶体管Q

实施例四

本实施例中的带隙基准电压适用于低电压应用。参考图8所示,本实施例中的带隙基准电压的生成电路包括第一电流源I

电流平方电路82包括第三电流源I

第三电流源I

第二双极型晶体管Q

第三双极型晶体管Q

第四双极型晶体管Q

第五双极型晶体管Q

第六双极型晶体管Q

第七双极型晶体管Q

第六电流源I

第一NMOS晶体管NM

第一PMOS晶体管PM

本实施例中,电流平方电路81与图7中的电流平方电路基本相同,主要区别在于:第一NMOS晶体管NM

本实施例中,加法器81包括:第九至第十NMOS晶体管NM

第九NMOS晶体管NM

本实施例中,由于采用本征阈值晶体管,可以有如下关系:

因此,通过调节第八电流源I

类似的,本实施例中,可以使得V

实施例五

本实施例中的加法器92包括放大器93和第九NMOS晶体管NM

放大器93的同相输入端连接第二电流源I

本申请一实施例中与温度线性相关的电流源或电流项I

需要说明的是,在本专利的申请文件中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个”限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。本专利的申请文件中,如果提到根据某要素执行某行为,则是指至少根据该要素执行该行为的意思,其中包括了两种情况:仅根据该要素执行该行为、和根据该要素和其它要素执行该行为。多个、多次、多种等表达包括2个、2次、2种以及2个以上、2次以上、2种以上。

在本说明书提及的所有文献都被认为是整体性地包括在本说明书的公开内容中,以便在必要时可以作为修改的依据。此外应理解,以上所述仅为本说明书的较佳实施例而已,并非用于限定本说明书的保护范围。凡在本说明书一个或多个实施例的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本说明书一个或多个实施例的保护范围之内。

- 具有高阶温度补偿的带隙基准电压生成电路

- 一种具有高阶温度补偿的带隙基准电压源电路