电源管理电路及电子设备

文献发布时间:2023-06-19 11:34:14

技术领域

本发明涉及电源管理电路。

背景技术

手机、平板终端、笔记本型个人计算机(PC)、台式PC、游戏机等电子设备具有包括CPU(Central Processing Unit:中央处理器)或GPU(Graphics Processing Unit:图形处理单元)等处理器、存储器的运算处理系统。运算处理系统也有时会如微控制器或SoC(System on Chip:片上系统)那样进行一体化。

伴随低电力消耗化的要求,运算处理系统被构成为:细分为多个电路块,能够针对每个电路块独立地供给电源电压。为了控制对应于多个电路块的多个电源系统,使用PMIC(Power Management Integrated Circuit:电源管理集成电路)。采用PMIC时,可以按照预定的顺序细致地控制多个电源的导通、截止或输出电压的设定电平,从而能够提高系统的性能。

[现有技术文献]

[专利文献]

专利文献1:日本特开2013-089060号公报

专利文献2:日本特许第3738245号公报

发明内容

在以往,针对每个平台优化设计PMIC,会发生对某个平台最优化的PMIC无法利用在其他平台的状况。因此,在预估出货台数不多的平台中,出于回收设计成本的观点难以专用设计PMIC,有时不得不放弃PMIC的采用。

本发明是在这样的状况下得到的,其一个方案的例示性的目的之一在于,提供一种提高通用性的电源管理电路。

[用于解决技术问题的方法]

本发明的一方案涉及电源管理电路。电源管理电路包括:第一电路块,包括第一反馈管脚、第二反馈管脚、第一反馈控制器及第一前置驱动器;以及第二电路块,包括第二反馈控制器及第二前置驱动器。在第一模式中,第一反馈控制器根据第一反馈管脚的信号生成第一控制信号,第一前置驱动器根据第一控制信号工作,第二反馈控制器根据第二反馈管脚的信号生成第二控制信号,第二前置驱动器根据第二控制信号工作。在第二模式中,第一反馈控制器根据第一反馈管脚的信号生成第一控制信号,第一前置驱动器根据第一控制信号工作,第二前置驱动器根据来自第一电路块的第三控制信号工作。

此外,将上述结构要素的任意组合或本发明的结构要素或表现在方法、装置、系统等之间相互置换来作为本发明的方案也是有效的。

[发明效果]

根据本发明的一个方案,可以提高电源管理电路的通用性。

附图说明

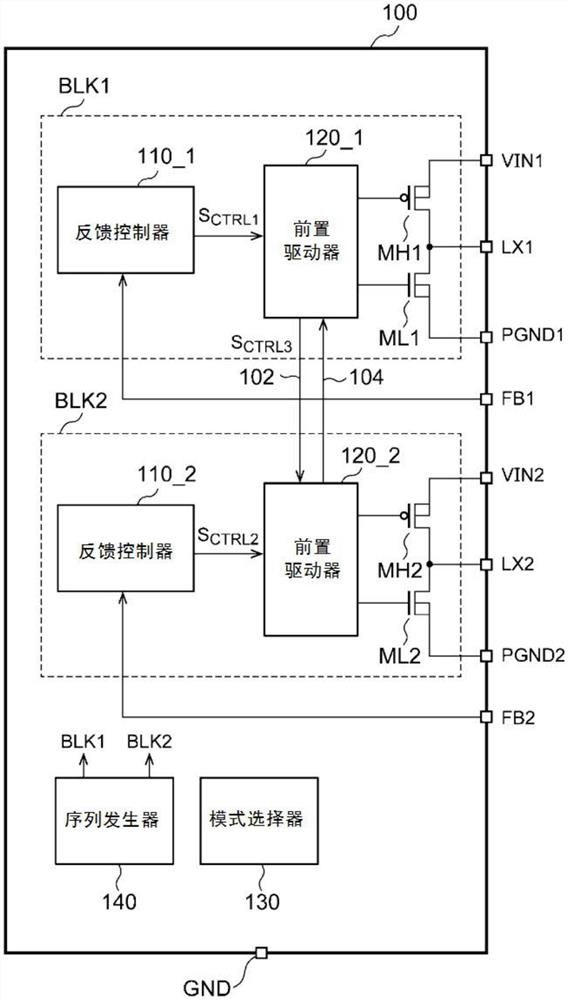

图1是实施方式的电源管理电路的框图。

图2是具备电源管理电路的第一系统的框图。

图3是具备电源管理电路的第二系统的框图。

图4是示出模式选择器的结构例的电路图。

图5是示出第一前置驱动器及第二前置驱动器的结构例的框图。

图6的(a)、(b)是过电流保护电路的电路图。

图7的(a)、(b)是峰值电流检测电路的电路图。

图8的(a)、(b)是低侧电流检测电路的电路图。

图9是电源管理电路的布局图。

图10的(a)、(b)是具备电源管理电路的电子设备的框图。

具体实施方式

(实施方式的概要)

本说明书所公开的一实施方式涉及电源管理电路。电源管理电路包括:第一电路块,第一反馈管脚、第二反馈管脚、第一反馈控制器及第一前置驱动器;以及第二电路块,包括第二反馈控制器及第二前置驱动器。在第一模式中,第一反馈控制器根据第一反馈管脚的信号生成第一控制信号,第一前置驱动器根据第一控制信号工作,第二反馈控制器根据第二反馈管脚的信号生成第二控制信号,第二前置驱动器根据第二控制信号工作。在第二模式中,第一反馈控制器根据第一反馈管脚的信号生成第一控制信号,第一前置驱动器根据第一控制信号工作,第二前置驱动器根据来自第一电路块的第三控制信号工作。

在一个平台中设定为第一模式,作为2通道的DC/DC转换器而工作。另外,在另一平台中设定为第二模式,将2个通道的输出汇集于1个系统,通过与单个的电感器连接,从而作为1通道的DC/DC转换器而工作。

在第二模式中,也可以停止第二反馈控制器的工作。由此可以减少电力消耗。

电源管理电路还可以具备模式选择器,在起动时,模式选择器根据第二反馈管脚的电气状态,选择第一模式和第二模式的一者。通过在模式设定中利用第二反馈管脚,可以抑制电源管理电路的管脚数的增加。

第一电路块和第二电路块也可以为同一芯体。由此,可以简化电路设计。

还可以设置信号路径,其用于在第二模式中,在第一前置驱动器和第二前置驱动器之间,传递用于控制死区时间的信号。由此,可以防止第一前置驱动器驱动的高侧晶体管(低侧晶体管)和第二前置驱动器驱动的低侧晶体管(高侧晶体管)的同时导通。

电源管理电路还可以包括第一输入管脚、第一输出管脚、第一接地管脚、第一输入管脚、第二输入管脚、第二输出管脚、以及第二接地管脚。第一电路块还可以包括:第一高侧晶体管,被设置在第一输出管脚之间;以及第一低侧晶体管,被设置在第一输出管脚和第一接地管脚之间。第二电路块还可以包括:第二高侧晶体管,被设置在第二输入管脚和第二输出管脚之间;以及第二低侧晶体管,被设置在第二输出管脚和第二接地管脚之间。

电源管理电路还可以包括:第一过电流检测电路,将第一高侧晶体管中流动的电流与第一过电流阈值相比较;以及第二过电流检测电路,将第二高侧晶体管中流动的电流与第二过电流阈值相比较。也可以是,在第一模式中,第一过电流检测电路和第二过电流检测电路是有效的(enabled),在第二模式中,第一过电流检测电路是有效的,第二过电流检测电路是无效的(disable)。在第二模式中,通过仅使第一过电流检测电路有效,可以减少电力消耗。

在第二模式中,也可以使第一过电流检测电路和第二过电流检测电路二者工作。在该情况下,也可以根据较早检测到过电流的一者的输出施加保护。

第一过电流检测电路也可以构成为能够将第一高侧晶体管的两端间电压与对应于第一过电流阈值的第一阈值电压相比较。可以是,在第二模式中,缩放第一阈值电压。在第二模式中,并联连接两个高侧晶体管,它们的导通电阻变为1/2倍。结合于此,通过缩放第一阈值电压,能够进行正确的过电流判定。

也可以是,第一过电流检测电路包括:虚设晶体管,一端与第一输入管脚连接;电流源,与虚设晶体管的另一端连接,向虚设晶体管供给电流;以及比较器,将第一高侧晶体管的两端间电压与虚设晶体管和电流源的连接节点的电位相比较。

也可以是,在第一模式和第二模式中,电流源生成的电流量不同。由此,可以缩放第一过电流阈值。

电源管理电路还可以包括:第一峰值电流检测电路,将第一高侧晶体管中流动的电流与第一峰值阈值相比较;以及第二峰值电流检测电路,将第二高侧晶体管中流动的电流与第二峰值阈值相比较。可以是,在第一模式中,第一峰值电流检测电路和第二峰值电流检测电路是有效的,在第二模式中,第一峰值电流检测电路是有效的,第二峰值电流检测电路是无效的,第一峰值阈值被缩放。在第二模式中,通过仅使第一峰值电流检测电路有效,可以减少电力消耗。

也可以是,在第二模式中,使第一峰值电流检测电路和第二峰值电流检测电路二者工作。在该情况下,也可以将较早反应的一者的输出利用在保护处理或反馈控制中。

第一峰值电流检测电路也可以构成为能够将第一高侧晶体管的两端间电压与对应于第一峰值阈值的第二阈值电压进行比较。在第二模式中,可以是第二阈值电压被缩放。在第二模式中并联连接两个高侧晶体管,它们的导通电阻变为1/2倍。结合于此,通过缩放第二阈值电压,能够进行正确的峰值电流检测。

第一峰值电流检测电路也可以包括:虚设晶体管,一端与第一输入管脚连接;电流源,与虚设晶体管的另一端连接,向虚设晶体管供给电流;以及比较器,将第一高侧晶体管的两端间电压与虚设晶体管和电流源的连接节点的电位相比较。

也可以是,虚设晶体管包括串联连接的多个晶体管元件,在第二模式中多个晶体管元件的一部分被旁路。由此可以缩放第一峰值阈值。

电源管理电路还可以包括将第一低侧晶体管中流动的电流与零或零附近的负的阈值相比较的低侧电流检测电路。可以是,在第一模式中,第一反馈控制器及第二反馈控制器根据低侧电流检测电路的输出生成第一控制信号及第二控制信号,在第二模式中第一反馈控制器根据低侧电流检测电路的输出生成第一控制信号。在轻负载状态下,低侧电流检测电路的输出为了在二极管整流模式下使其工作而被利用,主要为了改善效率而使用。或者,低侧电流检测电路的输出用在限制负电流不会过大的NCP(Negative CurrentProtection:反向电流保护)中。这些功能相比于过电流检测并不严格。因此,无论模式如何,都仅监测第一低侧晶体管的电流,由此可以削减电力消耗。

也可以是,在第一模式和第二模式中,用于零交叉检测的阈值被移位。

也可以是,使第一接地管脚和第二接地管脚共通化。由此可以削减管脚个数。

可以呈镜像地布局包括第一电路块的第一高侧晶体管和第一低侧晶体管的第一输出级以及包括第二电路块的第二高侧晶体管和第二低侧晶体管的第二输出级。由此,可以提高电路的对称性,可以使第二模式中的两个输出级均等地工作。也可以使第一接地管脚和第二接地管脚共通化。

也可以是,以同一芯体构成包括第一输出级和第一前置驱动器的部分以及包括第二输出级和第二前置驱动器的部分。另外,可以呈镜像地布局它们。通过包含前置驱动器在内呈对称地进行配置,可以提高工作的一致性。

(实施方式)

以下,基于优选实施方式,参照附图对本发明进行说明。对于各附图所示的相同或同等的构成要素、部件、处理标注相同的附图标记,并适当省略重复的说明。另外,实施方式是例示而非限定发明的内容,并非实施方式中所记载的全部特征及其组合都是发明的本质特征。

在本说明书中,所谓“部件A和部件B连接的状态”,除了部件A和部件B物理性地直接连接的情况以外,还包括部件A和部件B经由不会对它们的电连接状态造成实质性影响的或者不妨碍通过它们的结合所实现的功能或效果的其他部件而间接连接的情况。

同样地,所谓“部件C被设置在部件A和部件B之间的状态”,除了部件A和部件C、或部件B和部件C直接连接的情况以外,还包括经由不会对它们的电连接状态造成实质性影响的或者不妨碍通过它们的结合所实现的功能或效果的其他部件而间接连接的情况。

本说明书中参照的波形图或时序图的纵轴及横轴是为了容易理解而适当放大、缩小后的,并且所示的各波形也为了容易理解而被简化、夸张或强调。

图1是实施方式的电源管理电路100的框图。电源管理电路100具有第一输入(VIN1)管脚、第一输出(LX1)管脚、第一接地(PGND1)管脚、第一反馈(FB1)管脚FB1、第二输入(VIN2)管脚、第二输出(LX2)管脚、第二接地(PGND2)管脚、第二反馈(FB2)管脚、接地(GND)管脚,被容纳在一个封装中。

电源管理电路100包括第一反馈控制器110_1、第二反馈控制器110_2、第一前置驱动器120_1、第二前置驱动器120_2、第一高侧晶体管MH1、第一低侧晶体管ML1、第二高侧晶体管MH2、第二低侧晶体管ML2、模式选择器130、序列发生器140。

电源管理电路100可以选择第一模式和第二模式。第一模式和第二模式可以在安装有电源管理电路100的平台中固定地设定。模式选择器130根据来自外部的设定,选择第一模式和第二模式的一者。

第一反馈控制器110_1、第一前置驱动器120_1、第一高侧晶体管MH1、第二低侧晶体管ML1形成第一电路块BLK1。此外,第二反馈控制器110_2、第二前置驱动器120_2、第二高侧晶体管MH2、第二低侧晶体管ML2形成第二电路块BLK2。第一电路块BLK1和第二电路块BLK2可以设为同一芯体。因此,反馈控制器110_1和110_2具有相同的功能、结构,前置驱动器120_1和120_2具有相同的功能、结构。此外,第一高侧晶体管MH1和第二高侧晶体管MH2的尺寸相等,第一低侧晶体管ML1和第二低侧晶体管ML2的尺寸也相等。

序列发生器140控制第一电路块BLK1、第二电路块BLK2各自的起动、停止的时刻(timing)。

(第一模式)

第一模式是第一电路块BLK1和第二电路块BLK2完全独立工作的模式,电源管理电路100与外设的元件一起形成2输出(2通道)的DC/DC转换器。

在第一模式中,向FB1管脚、FB2管脚分别反馈与第一通道的DC/DC转换器的输出信号对应的反馈信号V

反馈控制器110的结构和控制方式并不特别地限定。例如,反馈控制器110可以是电压模式的控制器,也可以是峰值电流模式或平均电流模式的控制器。或者反馈控制器110也可以是迟滞控制(Bang-Bang控制)、波谷检测导通时间固定控制、波峰检测截止时间固定控制等波动控制的控制器。

第一前置驱动器120_1根据第一控制信号S

在第一模式中,序列发生器140以系统的起动的指示或导通电源等作为触发信号,在不同的时刻起动第一电路块BLK1和第二电路块BLK2。另外,也可以是,在支持睡眠模式或待机模式等的应用中,根据来自主处理器的指令,能够仅停止第一电路块BLK1、第二电路块BLK2一者的输出。另外,接收系统的停止的指示时,以不同的时刻停止第一电路块BLK1和第二电路块BLK2。也可以是,两个块BLK1、BLK2的起动时刻、停止时刻能够通过寄存器设定。

(第二模式)

在第二模式中,电源管理电路100与外设的元件一起形成1输出(1通道)的DC/DC转换器。具体而言,共通的电感器连接于LX1管脚、LX2管脚,一对第一高侧晶体管MH1和第二高侧晶体管MH2并联地电连接,一对第一低侧晶体管ML1和第二低侧晶体管ML2并联地电连接。

在第二模式中,向FB1管脚反馈与共通的DC/DC转换器的输出信号对应的反馈信号V

在第二模式中,第一反馈控制器110_1根据FB1管脚的信号生成第一控制信号S

第一前置驱动器120_1根据第一控制信号S

由此,第一高侧晶体管MH1和第二高侧晶体管MH2实质上同时变为导通、变为截止,第一低侧晶体管ML1和第二低侧晶体管ML2实质上同时变为导通、变为截止。

从第二前置驱动器120_2供给至第一前置驱动器120_1的第四控制信号S

电源管理电路100包括信号路径104,其用于在第二模式中,在第一前置驱动器120_1和第二前置驱动器120_2之间,传递用于控制死区时间(防止贯通电流)的控制信号S

在第二模式中,第一电路块BLK1和第二电路块BLK2形成单一的通道。因此,在第二模式中,序列发生器140以系统的起动的指示或导通电源作为触发,在相同时刻起动第一电路块BLK1和第二电路块BLK2。另外,接收到系统的停止指示时,使第一电路块BLK1、第二电路块BLK2停止。

上述为电源管理电路100的结构。接着说明其动作。

图2是具备电源管理电路100的第一系统201的框图。在系统201中,电源管理电路100被设定为第一模式。电感器L1、输出电容器Co1连接于LX1管脚,形成第一通道CH1的DC/DC转换器。电阻分压电路R11、R12连接于FB1管脚,反馈与输出电压V

电感器L2、输出电容器Co2连接于LX2管脚,形成第二通道CH2的DC/DC转换器。电阻分压电路R21、R22连接于FB2管脚,反馈与输出电压V

通过第一电路块BLK1,以第一反馈信号V

图3是具备电源管理电路100的第二系统202的框图。在系统202中,电源管理电路100被设定为第二模式。共通的电感器L1连接于LX1管脚及LX2管脚,形成1通道的DC/DC转换器。

在第二模式中,第一电路块BLK1作为主要,第二电路块BLK2作为从属,进行工作。电阻分压电路R11、R12连接于FB1管脚,反馈与输出电压V

上述为电源管理电路100的动作。根据电源管理电路100,可以在某个平台中设定为第一模式,使其作为2通道的DC/DC转换器进行工作。另外,在其他平台中设定为第二模式,并将2个通道的输出汇集于1个系统,与单个的电感器连接,从而可以使其作为1通道的DC/DC转换器工作。在第二模式中,由于第一高侧晶体管MH1和第二高侧晶体管MH2并联连接,第一低侧晶体管ML1和第二低侧晶体管ML2并联连接,从而可以增大电流供给能力,相比于第一模式,可以作为重负载(工作电流大的负载)的电源使用。

本发明可作为图1的框图或电路图进行理解,或者,及于由上述的说明导出的各种装置、方法,并不限定于特定的结构。下面,不在于缩小本发明的范围,而是为了辅助发明的本质或动作的理解,并使其明确,说明更具体的构成例或实施例。

(模式选择)

在模式的指定中,可以使用第二反馈管脚FB2。图4是示出模式选择器130的结构例的电路图。模式选择器130包括被设置在FB2管脚和接地之间的电阻R31、R32、开关SW31、比较器CMP31。在起动电源管理电路100后的判定期间的过程中,开关SW31为导通,在判定结束后开关SW31为截止。由此,可以防止无用的电流经由电阻R31、R32流动。

在需要设定为第一模式MODE1的应用(系统)中,FB2管脚直接或经由电阻分压电路,与输出电容器Co2连接。在模式判定时,输出电压V

在需要设定为第二模式MODE2的应用(系统)中,将FB2管脚以经由电阻R33升高至高电平电压(例如5V左右的电源电压或其他电压)的方式固定。在模式判定时,开关SW31为导通,比较器CMP31中输入与高电平电压5V成比例的电压。其结果,通过比较器CMP31,判定为V

根据该模式选择器130,可以利用FB2管脚设定模式,因此具有无需增加模式设定用的管脚的优点。

在管脚的个数存在富余的情况下,也可以增加模式设定用的管脚,根据其电气状态指定模式。或者,也可以是,从外部将用于模式设定的数据写入电源管理电路100的寄存器中。或者,也可以是,将用于模式设定的非易失性存储器设置在电源管理电路100中,在电源管理电路100起动时,访问非易失性存储器判定模式。

(前置驱动器)

图5是示出第一前置驱动器及第二前置驱动器的结构例的框图。首先,针对第一反馈控制器110_1进行说明。第一反馈控制器110_1包括死区时间控制器111、死区时间控制器112、控制逻辑单元113、控制逻辑单元114、缓冲器115、缓冲器116。

控制逻辑单元113、114分别根据控制信号S

第一反馈控制器110_1侧的缓冲器115根据控制脉冲S

为了防止第一高侧晶体管MH1和第二高侧晶体管MH2的贯通电流,控制逻辑单元113监测缓冲器116的内部节点的信号,在被指示第一低侧晶体管ML1的导通的期间,控制脉冲S

为了进行死区时间控制,在第二模式中,第二高侧晶体管MH2及第二低侧晶体管ML2的栅极信号V

向死区时间控制器111输入第一高侧晶体管MH1的栅极脉冲V

在第一模式中,死区时间控制器111将栅极信号V

在第二模式中,死区时间控制器111将栅极信号V

向死区时间控制器112输入第一低侧晶体管ML1的栅极脉冲V

在第一模式中,死区时间控制器112将栅极信号V

在第二模式中,死区时间控制器112将栅极信号V

第二反馈控制器110_2的结构与第一反馈控制器110_1相同。第二反馈控制器110_2在第一模式中与第一反馈控制器110_1同样地工作,但在第二模式中,死区时间控制器111、死区时间控制器112、控制逻辑单元113、控制逻辑单元114停止。在第二模式中,从第一反馈控制器110_1向第二反馈控制器110_2供给包含控制脉冲S

本领域技术人员应当理解的是,反馈控制器110的结构并不限定于图5的结构。

(过电流保护)

图6的(a)、(b)是过电流保护电路的电路图。在图6的(a)中示出第一模式的状态,图6的(b)中示出第二模式的状态。第一电路块BLK1、第二电路块BLK2分别包括第一过电流检测电路150_1、第二过电流检测电路150_2。

第一过电流检测电路150_1将第一高侧晶体管MH1中流动的电流I

在第二模式中,通过仅将第一过电流检测电路150_1置于有效,可以减小电力消耗。另外,在第二模式中,若并用两个过电流检测电路150_1、150_2,它们的检测条件或响应速度存在差异的情况下,发生工作的不匹配时,通过仅将一个过电流检测电路150_1置于有效,可以消除不匹配。

第一过电流检测电路150_1构成为能够将第一高侧晶体管MH1的两端间电压V

第一过电流检测电路150_1包括复制晶体管152、电流源154、比较器156。复制晶体管152是第一高侧晶体管MH1的复制品,其一端即源极与VIN1管脚连接。复制晶体管152的栅极以与第一高侧晶体管MH1成为相同状态的方式偏置。电流源154与复制晶体管152的另一端(漏极)连接,向复制晶体管152供给电流。复制晶体管152的两端间电压ΔV

比较器156将第一高侧晶体管的两端间电压(漏极源极间电压)与复制晶体管152的两端间电压ΔV

也可以是,电流源154包括恒流源154a和电流DAC154b,向复制晶体管152供给它们的输出电流的合计。通过使电流DAC154b的数字输入值在第一模式和第二模式中变化,可以缩放阈值ΔV

(峰值电流检测)

在采用峰值电流模式的反馈控制器的情况、或为了进行轻负载时的PFM(PulseFrequency Modulation:脉冲频率调制)控制(也称为间歇模式控制),设置有峰值电流检测电路,其检测高侧晶体管到达预定的峰值电流的情况。

图7的(a)、(b)是峰值电流检测电路的电路图。图7的(a)中示出第一模式的状态,图7的(b)中示出第二模式的状态。第一电路块BLK1、第二电路块BLK2分别包括第一峰值电流检测电路160_1、第二峰值电流检测电路160_2。

第一峰值电流检测电路160_1将第一高侧晶体管MH1中流动的电流I

在第一模式中,第一峰值电流检测电路160_1和第二峰值电流检测电路160_2是有效的,各电路块BLK_#(#=1、2)根据对应的峰值电流检测电路160_#的输出而工作。

在第二模式中,仅第一峰值电流检测电路160_1是有效的,第二峰值电流检测电路160_2是无效的。两个电路块BLK1、BLK2根据第一峰值电流检测电路160_1的输出而工作。

在第二模式中,通过仅将第一峰值电流检测电路160_1置于有效,可以减小电力消耗。另外,在第二模式中,若兼用两个峰值电流检测电路,在它们的检测条件或响应速度存在差异的情况下,发生工作的不匹配时,通过仅将一个峰值电流检测电路置于有效,可以消除不匹配。

第一峰值电流检测电路160_1构成为能够将第一高侧晶体管MH1的两端间电压V

峰值电流检测电路160_1、160_2可以与过电流检测电路150_1、150_2同样地构成。第一峰值电流检测电路160_1包括复制晶体管162、电流源164、比较器166。复制晶体管162包括串联连接的多个晶体管元件,在第二模式中,多个晶体管元件的一部分可以通过开关SW41旁路。若导通开关SW41,则复制晶体管162的电压下降变为1/2,可以适当地缩放阈值电压ΔV

(零电流检测、负电流检测)

在同步整流型的DC/DC转换器中,整流元件即低侧晶体管中流动反向电流时,效率降低。因此,有时会导入如下控制:检测到低侧晶体管中的电流的零交叉时、或检测到负电流时,强制性地截止低侧晶体管,移至二极管整流模式。

或者,还存在低侧晶体管中允许负电流(反向电流)的应用。在该情况下,低侧晶体管中流动的反向电流过大时,产生发热等的问题。另外,在电感器中流动大的反向电流的状态下,开关高侧晶体管或低侧晶体管时,LX管脚或其他电压中引起大的电压振动而不期待。因此,在允许反向电流的应用所使用的控制电路中,安装NCP(Negative CurrentProtection:反向电流保护)功能。

零电流检测、负电流检测在均为将低侧晶体管的电流与零或零附近的负的阈值相比较的方面是共通的。

图8的(a)、(b)是低侧电流检测电路的电路图。低侧晶体管ML的电流的监测并不要求像过电流检测或峰值电流检测那样严格的精度。因此,在一实施例中,仅在第一电路块BLK1中设置低侧电流检测电路170_1,在第二块BLK2没有设置。图8的(a)中示出第一模式的状态,图8的(b)中示出第二模式的状态。

低侧电流检测电路170_1将第一低侧晶体管ML1中流动的电流I

低侧电流检测电路170_1包括带偏置的差动放大器172、电压比较器174。差动放大器172包括尾电流源172a、输入差动对172b、电阻负载172c。被构成为,电阻负载172c的电阻值能够根据模式而切换。

如图8的(a)所示,在第一模式中,低侧电流检测电路170_1的输出被供给至第一反馈控制器110_1、第二反馈控制器110_2。如图8的(b)所示,在第二模式中,低侧电流检测电路170_1的输出被供给至第一反馈控制器110_1。

作为零交叉检测使用时,开关SW51、SW52为截止。在用于NCP的情况下,通过导通开关SW51、SW52的一者,可以导入偏置,可以设定负的阈值。在第一模式和第二模式中,通过切换导通的开关SW51、SW52,可以缩放阈值。

(布局)

接着,说明电源管理电路100的优选的布局。在第二模式中,谋求的是,两个电路块BLK1、BLK2连接于共通的电感器,它们实质上在相同时刻工作。

图9是电源管理电路100的例示性的布局图。两个电路块BLK1、BLK2以形成镜像的方式进行布局。由此,可以使电路块BLK1和电感器L1之间的阻抗、电路块BLK2和电感器L1之间的阻抗一致。

另外,电路块BLK1、BLK2的接地管脚PGND1、PGND2被共通化(PGND管脚),配置在两个块的边界部分。由此,可以使LX1管脚和LX2管脚的距离靠近,能够减小连接于共通的电感器时的阻抗之差。此外,不是必须呈镜像地配置两个电路块BLK1、BLK2。

(应用)

图10的(a)、(b)是具备电源管理电路的电子设备的框图。图10的(a)为具有第一平台的电子设备301,图10的(b)为具有第二平台的电子设备302。在图10的(a)、(b)中,省略外设的电感器和电容器。

参照图10的(a)。电子设备301包括SOC311、向SOC311供给电源电压的电源管理电路100及多个电源电路330。

电源管理电路100包括4通道CH0~CH3的DC/DC转换器的控制器,其中的2个通道CH1、CH采用上述的结构构成。剩余的2个通道CH0、CH3单独工作。

SOC311包括芯体320、存储器322、其他块。电源管理电路100主要向芯体320供给电源电压,其他电源电路330向存储器322或其他块供给电源电压。

图10的(a)的平台所使用的SOC311包括独立的4系统的电源管脚VDD0~VDD3。此时,电源管理电路100被设定为第一模式,两个通道CH1、CH2独立工作,作为4通道的DC/DC转换器工作。

图10的(b)的平台所使用的SOC312包括独立的3系统的电源管脚,其中的一个VDD1相比于其他通道电流量大。在该情况下,电源管理电路100被设定为第二模式,两个通道CH1、CH2作为单一通道工作,整体作为3通道的DC/DC转换器工作。

以上,基于实施方式对本发明进行了说明。本领域技术人员应当理解:该实施方式是例示,在所述各构成要素或各处理过程的组合中可能会存在各种变形例,这些变形例也属于本发明的范围。以下,对这些变形例进行说明。

(变形例1)

将第一电路块BLK1、第二电路块BLK2作为同一芯体进行了说明,但并不限定于此。

例如,可以以同一芯体设计包括第一电路块的第一高侧晶体管和第一低侧晶体管的第一输出级以及包括第二电路块的第二高侧晶体管和第二低侧晶体管的第二输出级。此时,以形成镜像的方式在半导体芯片上布局两个输出级即可。

或者,可以以同一芯体设计包括第一输出级和第一前置驱动器的部分以及包括第二输出级和第二前置驱动器的部分。在该情况下,可以以成为镜像的方式在半导体芯片上布局两个部分。

此外,在两个电路块BLK1、BLK2中,输出级的对应的功率晶体管MH(ML)的尺寸可以不同。

(变形例2)

在实施方式中,说明了电源管理电路100中内置有DC/DC转换器的输出级的功率晶体管的结构,但并不限定于此,功率晶体管也可以外设分立部件。

(变形例3)

电源管理电路100的输出的通道数没有特别的限定。在具有4通道CH0~CH3的情况下,使通道CH0、CH1彼此、CH2、CH3彼此成对,将各对形成为上述的两个电路块BLK1、BLK2。此时,可以使电源管理电路100的输出在2通道~4通道中变化,能够对应更多的平台。

(变形例4)

在图6(或图7)中,在第二模式中将从属侧的第二过电流检测电路150_2(或第二峰值电流检测电路160_2)置于无效,但并不限定于此,可以使其与主要侧的第一过电流检测电路150_1(第一峰值电流检测电路160_1)并联工作。在该情况下,两个检测电路150_1、150_2(160_1、160_2)中,可以将较早反应的一者的输出利用在控制或保护中。

(变形例5)

在实施方式中,说明了2通道的结构,但本发明也可以适用于3以上的任意通道数N。在该情况下,可以构成为能够选择使N通道全部独立工作的模式和将N通道中M通道(M≦N)连接于共通的电感器,将M通道中一个作为主要、将其余作为从属而工作的模式。

(变形例6)

在实施方式中,将第一电路块BLK1固定为主要,将第二电路块BLK2固定为从属,但并不限定于此,还可以支持将第二电路块BLK2作为主要、将第一电路块BLK1作为从属而工作的第三模式。此时,在第三模式中,增加用于从第二电路块BLK2向第一电路块BLK1传递反馈的控制信号的信号路径,增加用于从第一电路块BLK1向第二电路块BLK2,传递用于控制死区时间(防止贯通电流)的控制信号S

模式选择器130构成为能够选择第一模式至第三模式的任一项即可。例如,可以在FB1管脚侧也增加图4的模式选择器130。而且,可以根据FB1管脚、FB2管脚的电气状态的组合,选择第一模式~第三模式。可以针对对应的块BLK#,将第#个FB#管脚(#=1、2)理解为指定主要或从属的管脚。此时,可以按照如下的方式将模式和管脚的状态建立对应。

(i)第一模式

FB1、FB2管脚二者为主要

(ii)第二模式

FB1管脚为主要,FB2管脚为从属

(iii)第三模式

FB1管脚为从属,FB2管脚为主要

(变形例7)

在实施方式中,将低侧电流检测电路仅设置在第一低侧晶体管侧,但并不限定于此,可以针对第一低侧晶体管、第二低侧晶体管分别设置低侧电流检测电路。

基于实施方式,使用具体的语句对本发明进行了说明,但实施方式仅表示本发明的原理和应用,对于实施方式,在不脱离权利要求书所规定的本发明的思想的范围内,认可许多变形例及配置的变更。

[工业上的可利用性]

本发明涉及电源管理电路。

[附图标记说明]

MH1第一高侧晶体管

ML1第一低侧晶体管

BLK1第一电路块

SCTRL1第一控制信号

FB1第一反馈管脚

VIN1第一输入管脚

LX1第一输出管脚

PGND1第一接地管脚

MH2第二高侧晶体管

ML2第二低侧晶体管

BLK2第二电路块

SCTRL2第二控制信号

FB2第二反馈管脚

VIN2第二输入管脚

LX2第二输出管脚

PGND2第二接地管脚

SCTRL3第三控制信号

SCTRL4第四控制信号

100电源管理电路

102、104信号路径

110反馈控制器

110_1第一反馈控制器

110_2第二反馈控制器

111、112死区时间控制器

113、114控制逻辑单元

115、116缓冲器

120_1第一前置驱动器

120_2第二前置驱动器

120前置驱动器

130模式选择器

140序列发生器

150_1第一过电流检测电路

150_2第二过电流检测电路

152复制晶体管

154电流源

154a恒流源

154b电流DAC

156比较器

160_1第一峰值电流检测电路

GND接地管脚

160_2第二峰值电流检测电路

162复制晶体管

164电流源

164a恒流源

164b电流DAC

166比较器

170_1低侧电流检测电路

172差动放大器

174比较器

201、202系统

301、302电子设备。

- 电源管理电路、电子设备及电源管理方法

- 电源管理电路、电子设备及电源管理方法