加密芯片及地下标识器

文献发布时间:2023-06-19 11:35:49

技术领域

本申请涉及电子通信领域,特别是涉及一种加密芯片及地下标识器。

背景技术

传统的射频传输芯片一般为无线感应芯片。无线感应芯片在得到电源与频率之后,会直接将储存在芯片内部的原始数据,传送给接收器,导致被传输的数据没有安全性,而且容易被侧录。

发明内容

基于此,有必要针对传统的无线感应芯片在得到电源与频率之后,会直接将储存在芯片内部的原始数据,传送给接收器,导致被传输的数据没有安全性,而且容易被侧录的问题,提供一种加密芯片及地下标识器。

一种加密芯片,包括:

整流模组,用于产生加密芯片所需的电源;

除频模组,与所述整流模组并联,用于产生所述加密芯片所需的时钟;

控制模组,分别与所述整流模组和所述除频模组电连接,用于总控所述加密芯片的工作流程;

存储模组,与所述控制模组电连接,用于存储芯片数据;

加密模组,分别与所述控制模组和所述存储模组电连接,用于采用进阶加密标准对所述芯片数据进行加密。

在其中一个实施例中,所述加密模组包括:

秘钥产生器,用于产生不同字长的秘钥;

加密处理器,所述加密处理器的输入端分别与所述秘钥产生器和所述存储模组电连接,用于采用进阶加密标准对所述秘钥和所述芯片数据进行加密处理;

加密结果缓存器,与所述加密处理器的输出端电连接,用于缓存加密后的所述芯片数据。

在其中一个实施例中,所述存储模组中存储的数据为128位;

所述秘钥产生器中产生128位,192位或256位字长的秘钥。

在其中一个实施例中,所述加密芯片还包括:

编码模组,与所述加密结果缓存器的输出端电连接,用于将加密后的所述芯片数据转换为射频输出格式的加密数据。

在其中一个实施例中,所述加密芯片还包括:

发射模组,与所述编码模组电连接,用于将所述射频输出格式的加密数据发射出去。

在其中一个实施例中,所述存储模组中存储的数据结构包括:

23位起始码;

80位数据码;

20位横行偶同位校验码,每4位所述数据码组成一行,每个偶数行包括一位所述横行偶同位校验码;

4位纵列奇同位校验码,每20位所述数据码组成一列,每个奇数列包括一位所述纵列奇同位校验码;

1位结束码。

在其中一个实施例中,所述加密芯片输出的波形为非对称波形,所述非对称波形中代表“0”的码元和代表“1”的码元是非对称的。

在其中一个实施例中,所述加密芯片输出的波形中,代表“0”的码元在一个周期内调制为低电平,代表“1”的码元在一个周期内调制为具有三次跳变。

在其中一个实施例中,所述三次跳变中第一次跳变为从高电平到低电平的跳变。

本申请还提供一种地下标识器,包括上述任一项所述的加密芯片。

本申请提供一种加密芯片及地下标识器。所述加密芯片包括:用于产生加密芯片所需的电源的整流模组、用于产生所述加密芯片所需的时钟的除频模组、用于总控所述加密芯片的工作流程的控制模组、用于存储芯片数据的存储模组以及用于采用进阶加密标准对所述芯片数据进行加密的加密模组。所述除频模组与所述整流模组并联。所述控制模组分别与所述整流模组和所述除频模组电连接。所述存储模组与所述控制模组电连接。所述加密模组分别与所述控制模组和所述存储模组电连接。本申请中所述加密芯片的内部增加了采用进阶加密标准进行加密的所述加密模组。所述加密芯片在得到电源与频率之后,会采用进阶加密标准对芯片数据进行加密处理。经过所述加密芯片加密处理之后,再传输的芯片数据具有较高的安全性,不容易被侧录。

附图说明

为了更清楚地说明本申请实施例或传统技术中的技术方案,下面将对实施例或传统技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

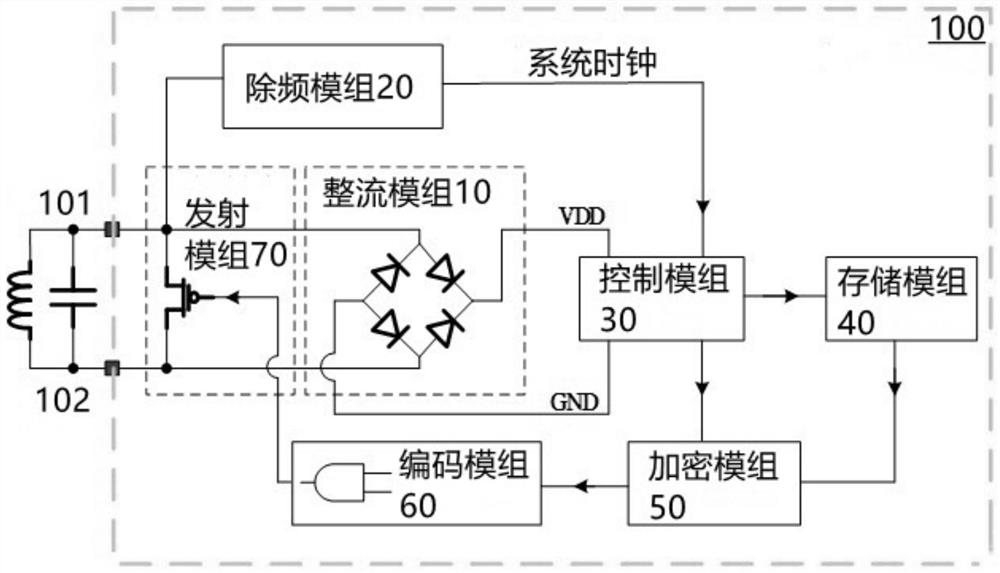

图1为本申请一个实施例提供的所述加密芯片的方框示意图。

图2为本申请一个实施例提供的所述整流模组的电路图。

图3为本申请一个实施例提供的所述除频模组的工作原理示意图。

图4为本申请一个实施例提供的所述控制模组的内部结构示意图。

图5为本申请一个实施例提供的所述加密模组的结构示意图。

图6为本申请一个实施例提供的所述加密芯片输出的数据结构示意图。

图7为本申请一个实施例提供的所述加密芯片的具体结构示意图。

附图标号说明

加密芯片100 第一引脚101 第二引脚102

整流模组10 电压限制电路11 整流电路12

除频模组20

控制模组30 存储控制器31 加密控制器32 编码控制器33

存储模组40

加密模组50 秘钥产生器51 加密处理器52 加密结果缓存器53

编码模组60

发射模组70

具体实施方式

为了使本申请的目的、技术方案及优点更加清楚明白,以下通过实施例,并结合附图,对本申请进行进一步详细说明。应当理解,此处所描述的具体实施例仅用以解释本申请,并不用于限定本申请。

本文中为部件所编序号本身,例如“第一”、“第二”等,仅用于区分所描述的对象,不具有任何顺序或技术含义。而本申请所说“连接”、“联接”,如无特别说明,均包括直接和间接连接(联接)。在本申请的描述中,需要理解的是,术语“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”、“顺时针”、“逆时针”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本申请和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本申请的限制。

在本申请中,除非另有明确的规定和限定,第一特征在第二特征“上”或“下”可以是第一和第二特征直接接触,或第一和第二特征通过中间媒介间接接触。而且,第一特征在第二特征“之上”、“上方”和“上面”可是第一特征在第二特征正上方或斜上方,或仅仅表示第一特征水平高度高于第二特征。第一特征在第二特征“之下”、“下方”和“下面”可以是第一特征在第二特征正下方或斜下方,或仅仅表示第一特征水平高度小于第二特征。

针对传统的无线感应芯片在得到电源与频率之后,会直接将储存在芯片内部的原始数据,传送给接收器,导致被传输的数据没有安全性,而且容易被侧录的问题,提供一种加密芯片及地下标识器。

请参阅图1,图1为本申请一个实施例提供的一种加密芯片100的方框示意图。所述加密芯片100包括:整流模组10、除频模组20、控制模组30、存储模组40和加密模组50。

所述整流模组10用于产生加密芯片100所需的电源。具体的,请参阅图2,图2为本申请一个实施例提供的所述整流模组的电路图。所述整流模组10为全波整流电路。所述整流模组10包括电压限制电路11与整流电路12。所述电压限制电路11负责将感应电压限制在所述加密芯片可100的正常工作范围内(2V-5V),避免所述加密芯片100因为过大的外部感应电压而烧毁。所述整流电路12负责将感应的交流电压,转换为可让所述加密芯片100工作的直流电压。

所述除频模组20与所述整流模组10并联,用于产生所述加密芯片100所需的时钟。具体的,请参阅图3,图3为本申请一个实施例提供的所述除频模组20的工作原理示意图。所述除频模组20用于将原始频率分解为不同的工作频率。所述除频模组20可以包括时钟转换电路与分频电路(图未示)。由于所述加密芯片100内部工作时钟为方波。因此设置所述时钟转换电路,将感应得到的弦波转换为方波。另外,由于所述加密芯片100的工作时序并不同,所述分频电路则负责产生所述加密芯片100各个电路模块需要的工作时钟及各种分频。

所述控制模组30,分别与所述整流模组10和所述除频模组20电连接,用于总控所述加密芯片100的工作流程。请参阅图4,图4为本申请一个实施例提供的所述控制模组30的内部结构示意图。所述控制模组30包括存储控制器31、加密控制器32以及编码控制器33。所述控制模组30负责总控所述加密芯片100的工作流程。具体的,所述存储控制器31用于控制所述存储模组40的数据读入和/或数据读出。所述加密控制器32用于控制所述加密模组50的加密工作开启与否。所述编码控制器33用于实现对加密后的芯片数据的编码工作的运行与开展。

所述存储模组40与所述控制模组30电连接,用于存储芯片数据。所述存储模组40可以为只读存储器(Read-Only Memory,ROM)以非破坏性读出方式工作,只能读出无法写入芯片信息。

所述加密模组50分别与所述控制模组30和所述存储模组40电连接,用于采用进阶加密标准对所述芯片数据进行加密。所述加密模组50的具体结构并不限定,只要能够采用进阶加密标准实现对所述芯片数据进行加密的功能即可。

本实施例中,所述加密芯片100的内部增加了采用进阶加密标准进行加密的所述加密模组50。所述加密芯片100在得到电源与频率之后,会采用进阶加密标准对芯片数据进行加密处理。经过所述加密芯片加密处理之后,再传输的芯片数据具有较高的安全性,不容易被侧录。

请参阅图5,图5为所述加密模组50的结构示意图。在一个实施例中,所述加密模组50包括:秘钥产生器51、加密处理器52和加密结果缓存器53。

所述秘钥产生器51用于产生不同字长的秘钥。所述加密处理器52用于采用进阶加密标准对所述秘钥和所述芯片数据进行加密处理。所述加密处理器52的输入端分别与所述秘钥产生器51和所述存储模组40电连接。所述加密结果缓存器53用于缓存加密后的所述芯片数据。所述加密结果缓存器53与所述加密处理器52的输出端电连接。

本实施例中,提供了所述加密模组50的一种具体结构。所述加密模组50主要负责所述加密芯片100的加密工作,并且所述加密模组50是采用进阶加密标准对所述芯片数据进行加密。具体的,本实施例中,所述加密模组50采用进阶加密标准/高级加密标准(Advanced Encryption Standard,简称AES)对所述芯片数据进行加密处理。所述加密模组50中根据不同字长的秘钥以及不同字长的所述芯片数据,采用不同的加密轮数,最终实现对所述芯片数据的进阶加密处理。

在一个实施例中,所述存储模组40中存储的所述芯片数据为128位。所述秘钥产生器51中产生128位,192位或256位字长的秘钥。

本实施例中,可以是128位的所述芯片数据与128位的秘钥进行AES加密处理。可以是128位的所述芯片数据与192位的秘钥进行AES加密处理。还可以是128位的所述芯片数据与256位的秘钥进行AES加密处理。秘钥的长度不同,在进行AES加密处理时,加密轮数不同,其产生加密的所述芯片数据的加密等级不同。

在一个实施例中,所述加密芯片100还包括编码模组60。

所述编码模组60与所述加密结果缓存器53的输出端电连接,用于将加密后的所述芯片数据转换为射频输出格式的加密数据。所述编码模组60可以为载波编码模组。所述编码模组60用于将加密后的数据,转换为适合射频输出的格式,为下一步的射频输出做准备。

在一个实施例中,所述加密芯片100还包括发射模组70。

所述发射模组70与所述编码模组60电连接,用于将所述射频输出格式的加密数据发射出去。所述发射模组70可以包括高频振荡器和功率放大器。具体的,所述发射模组70可以包括电感,电容,电阻,晶体管放大器等元件组成的发射电路。在一个实施例中,所述发射模组70可以等效为三极管,将经过编码的加密后的所述芯片数据存储并加载至射频,传输至所述加密芯片100之外。

在一个实施例中,所述存储模组40中存储的数据结构包括:23位起始码、80位数据码、20位横行偶同位校验码、4位纵列奇同位校验码以及1位结束码。每4位所述数据码组成一行,每个偶数行包括一位所述横行偶同位校验码。每20位所述数据码组成一列,每个奇数列包括一位所述纵列奇同位校验码。

请参阅表1,本实施例中,所述存储模组40可以为计算机只读存储器(ROM),主要负责储存原始的所述芯片数据(加密前的所述芯片数据)。所述存储模组40中存储的数据共128位(128BITS)。其中包括23位起始码,80位数据码,20位横行偶同位校验码,4位纵列奇同位校验码和1位结束码。其中,23位起始码,即表1中的23个“1”作为起始码。80位数据码,即表1中的D00-DJ3共80BITS的数据位。20位横行偶同位校验码,即表1中的P0-P19横行偶同位校验码。4位纵列奇同位校验码,即表1中的PC0-PC3纵列奇同位校验码。1位结束码,即为表1中的“0”,作为结后缀。

表1:所述存储模组的数据结构示意表

表1中ROM_DATA的数据,为未经加密的原始芯片数据。

请参阅图6,图6为所述加密芯片100输出的数据结构示意图。在一个实施例中,提供了所述加密芯片100的连续输出范例。

在一个具体的实施例中,形成的所述加密芯片100为CSG5208芯片。参照图6,所述加密芯片100中的特殊编码结构为:数据“0”为25%周期的触发波形。数据“1”为100%周期的触发波形。

在一个实施例中,所述加密芯片100输出的波形为非对称波形,所述非对称波形中代表“0”的码元和代表“1”的码元是非对称的。

在一个实施例中,所述加密芯片100输出的波形中,代表“0”的码元在一个周期内调制为低电平,代表“1”的码元在一个周期内调制为具有三次跳变。所述三次跳变中第一次跳变为从高电平到低电平的跳变。

在另一个实施例中,所述加密芯片100输出的波形中,代表“0”的码元在一个周期内调制为高电平,代表“1”的码元在一个周期内调制为具有三次跳变。所述三次跳变中第一次跳变为从低电平到高电平的跳变。

请参阅图7,图7为本申请提供的一种所述加密芯片100的具体结构示意图。所述加密芯片100包括用于产生加密芯片所需的电源的所述整流模组10、用于产生所述加密芯片100所需的时钟的所述除频模组20、用于总控所述加密芯片100的工作流程的所述控制模组30、用于存储芯片数据的所述存储模组40、用于采用进阶加密标准对所述芯片数据进行加密的所述加密模组50、用于将加密后的所述芯片数据转换为射频输出格式的所述加密数据的所述编码模组60以及用于将所述射频输出格式的加密数据发射出去的所述发射模组70。

所述加密芯片100的工作步骤,如下:

所述加密芯片100采用外部LC并联谐振电路触发第一引脚101和第二引脚102。所述整流模组10与所述除频模组20开始产生供整个所述加密芯片100工作所需的电源与时钟。需要进一步说明的是:当外部射频磁场靠近LC并联谐振电路时,在LC并联谐振电路两端的第一引脚101和第二引脚102产生感应电压,由所述加密芯片100本身电路将此感应电压,转化为所述加密芯片100的工作电压与工作频率,并在此感应电压加载回传信号。

所述控制模组30发出控制命令,命令所述存储模组40循序输出所述芯片数据至所述加密模组50。所述加密模组50将所述芯片数据打散,再结合生成的秘钥进行重组加密处理。即,所述加密模组50采用进阶加密标准对所述芯片数据进行加密。加密后的所述芯片数据经过所述编码模组60进行载波编码,最终由所述发射模组70将加密后的所述芯片数据发射出去。

本实施例中,所述加密芯片100内部的原始芯片数据在发射前,先经过所述加密模组50,将数据打散重组,然后再传送给所述加密芯片100的所述发射模组70。当所述加密芯片100被侧录或是盗取后,由于所述加密模组50已经对进行了加密处理,所述加密芯片100不容易被破译,大大提高了所述加密芯片100的安全性。

本申请还提供一种地下标识器,包括上述任一项所述的加密芯片100。本申请提供的所述地下标识器中集成了采用进阶加密标准对所述芯片数据进行加密的所述加密芯片100,使得所述地下标识器数据没有安全性,而且不容易被侧录,大大提升了所述地下标识器的使用安全性。

本申请还包括一种地下标识器读取装置(图未示)。所述地下标识器读取装置可以是手持装置。所述地下标识器读取装置包括:接收模组、解码模组、读取控制模组、输出模组和显示模组。所述接收模组、所述解码模组和所述读取控制模组依次电连接。所述输出模组和所述显示模组分别电连接至所述读取控制模组。所述接收模组用于读取所述地下标识器中所述加密芯片100中加密的所述芯片数据。所述解码模组用于将加密的所述芯片数据还原为所述加密芯片100的原始所述芯片数据。所述输出模组用于将原始的所述芯片数据输出至其他需要识别所述加密芯片100的设备中。所述显示模组用于将原始的所述芯片数据在所述地下标识器读取装置的显示屏中进行显示。所述读取控制模组用于控制所述接收模组、所述解码模组、所述输出模组和所述显示模组的工作流程。

以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

以上所述实施例仅表达了本申请的几种实施方式,其描述较为具体和详细,但并不能因此而理解为本专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本申请构思的前提下,还可以做出若干变形和改进,这些都属于本申请的保护范围。因此,本申请专利的保护范围应以所附权利要求为准。

- 加密芯片及地下标识器

- 动态加密芯片及地下标识器