一种基于服务器PCIE信号扩展的方法及设备

文献发布时间:2023-06-19 11:35:49

技术领域

本发明涉及计算机技术领域,具体而言,涉及一种基于服务器PCIE信号扩展的方法及设备。

背景技术

近年来,随着智能化应用的快速发展,集中式视频监管系统的应用也越来越广泛,流服务器作为主要的数据处理中心,对其处理能力的要求越来越高,当服务器需要增加性能以及提高服务器密度时,就需要添加一些外部扩展设备,例如一些以U.2(又名SFF-8639)为接口的标准硬盘大小的加速卡的应用,但由于受到服务器主板结构空间的限制,无法添加更多的扩展设备,因此,需要设计PCIE(Peripheral Component Interconnect Express,一种高速串行计算机扩展总线标准)的转接卡来扩展服务器主板的PCIE信号,搭配上述加速设备的使用,从而提高服务器密度,增强服务器处理能力。

Oculink是一种支持PCIE 4.0的接口规范,其在服务器主板上已被广泛应用,但由于服务器内部空间有限,主板接口的配置是有一定条件限制的,可以用于连接外部设备的Oculink接口的数量也是有限制的,因此,需要一种将服务器主板上Oculink接口进行扩展的方法,以满足更多硬件加速设备的扩展需求。

发明内容

为了解决上述问题,本发明提供一种基于服务器PCIE信号扩展的方法及设备,通过将两个Oculink接口扩展成四个Oculink接口,实现对服务器主板PCIE信号的扩展,用以提高服务器可搭配使用的外部设备的多样性,增加服务器密度,并同时增强服务器处理能力。

为了达到上述目的,本发明提供了一种基于服务器PCIE信号扩展的方法,其将服务器上的两个主Oculink接口分别各自扩展为两个Oculink扩展接口,共扩展为四个Oculink扩展接口,其中任一主Oculink接口扩展为两个Oculink扩展接口的扩展方法包括PCIE信号扩展方法、复位信号扩展方法和时钟信号扩展方法,其中:

所述PCIE信号扩展方法的具体过程为:

步骤101:主Oculink接口通过Oculink线缆从服务器主机获取PCIE信号,并将获取到的两通路PCIE×4分别传输到第一PCIE中继器和第二PCIE中继器;

步骤102:任一PCIE中继器将对应的一通路PCIE×4扩展为两通路PCIE×2,并同时传输到对应的Oculink扩展接口;

所述复位信号扩展方法的具体过程为:

步骤200:主Oculink接口将从服务器主机获取的两路复位信号分别通过NMOS驱动电路传输到两个Oculink扩展接口;以及

所述时钟信号扩展方法的具体过程为:

步骤300:两个时钟芯片分别将从主Oculink接口获取的时钟信号传输到对应的Oculink扩展接口。

在本发明一实施例中,其中,步骤102的具体传输过程为:

第一PCIE中继器将对应的一通路PCIE×4扩展为两通路PCIE×2,并传输到第一Oculink扩展接口;

第二PCIE中继器将对应的一通路PCIE×4扩展为两通路PCIE×2,并传输到第二Oculink扩展接口。

在本发明一实施例中,其中,步骤300中时钟信号的传输过程具体为:

主Oculink接口将时钟信号分别传输到第一时钟芯片和第二时钟芯片的输入端,然后第一时钟芯片的两个输出端将时钟信号输入到第一Oculink扩展接口,第二时钟芯片的两个输出端将时钟信号输入到第二Oculink扩展接口。

为了达到上述目的,本发明还提供了一种基于服务器PCIE信号扩展的设备,其包括:

一板卡;

两个主Oculink接口,设置于所述板卡上,其分别为第一主Oculink接口和第二主Oculink接口;

四个PCIE中继器,设置于所述板卡上,其分别为第一PCIE中继器、第二PCIE中继器、第三PCIE中继器和第四PCIE中继器,其中,所述第一PCIE中继器和所述第二PCIE中继器与所述第一主Oculink接口连接,所述第三PCIE中继器和所述第四PCIE中继器与所述第二主Oculink接口连接;

四个Oculink扩展接口,设置于所述板卡上,其分别为第一Oculink扩展接口、第二Oculink扩展接口、第三Oculink扩展接口和第四Oculink扩展接口,其中,所述四个Oculink扩展接口与所述四个PCIE中继器对应连接;

多个NMOS驱动电路,设置于所述板卡上,其分别为第一NMOS驱动电路、第二NMOS驱动电路、第三NMOS驱动电路和第四NMOS驱动电路,其中,每个NMOS驱动电路分别与其中一个主Oculink接口和对应的Oculink扩展接口连接;以及

四个时钟芯片,设置于所述板卡上,其分别为第一时钟芯片、第二时钟芯片、第三时钟芯片和第四时钟芯片,其中,每个时钟芯片分别与其中一个主Oculink接口和对应的Oculink扩展接口连接。

在本发明一实施例中,其中,每个主Oculink接口包含两通道PCIE×4。

在本发明一实施例中,其中,每个Oculink扩展接口包含两通道PCIE×2。

在本发明一实施例中,其中,所述四个Oculink扩展接口与所述四个PCIE中继器的具体连接方式为:

所述第一Oculink扩展接口与所述第一PCIE中继器连接,所述第二Oculink扩展接口与所述第二PCIE中继器连接,所述第三Oculink扩展接口与所述第三PCIE中继器连接,所述第四Oculink扩展接口与所述第四PCIE中继器连接。

在本发明一实施例中,其中,每个NMOS驱动电路分别与其中一个主Oculink接口和对应的Oculink扩展接口的连接具体为:

所述第一NMOS驱动电路分别与所述第一主Oculink接口和所述第一Oculink扩展接口连接,所述第二NMOS驱动电路分别与所述第一主Oculink接口和所述第二Oculink扩展接口连接,所述第三NMOS驱动电路分别与所述第二主Oculink接口和所述第三Oculink扩展接口连接,所述第四NMOS驱动电路分别与所述第二主Oculink接口和所述第四Oculink扩展接口连接。

在本发明一实施例中,其中,每个时钟芯片包含一输入端和两个输出端,每个时钟芯片的具体连接方式为:

所述第一时钟芯片的输入端和所述第二时钟芯片的输入端均连接到所述第一主Oculink接口,所述第一时钟芯片的两个输出端与所述第一Oculink扩展接口连接,所述第二时钟芯片的两个输出端与所述第二Oculink扩展接口连接;

所述第三时钟芯片的输入端和所述第四时钟芯片的输入端均连接到所述第二主Oculink接口,所述第三时钟芯片的两个输出端与所述第三Oculink扩展接口连接,所述第四时钟芯片的两个输出端与所述第四Oculink扩展接口连接。

在本发明一实施例中,其中,每个主Oculink接口分别通过一Oculink线缆与服务器主板连接。

本发明提出的基于服务器PCIE信号的扩展方法及设备,能够实现将两个Oculink接口扩展为四个Oculink接口,与现有技术相比,在完成扩展设备与服务器主板正常通信的基础上,还能够实现对服务器主板PCIE信号的扩展,提高服务器可搭配使用的外部设备的多样性,增加服务器密度,增强服务器的处理能力。

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

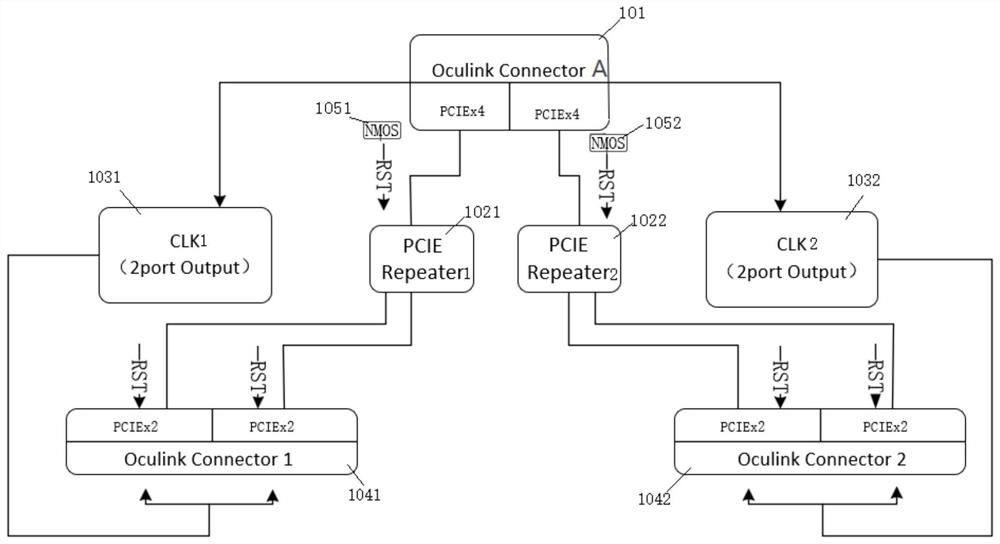

图1为本发明一实施例中将一个Oculink接口扩展为两个的扩展方法示意图;

图2为本发明一实施例的设备架构图。

附图标记说明:101-主Oculink接口;1021-PCIE中继器1;1022-PCIE中继器2;1031-时钟芯片1;1032-时钟芯片2;1041-Oculink扩展接口1;1042-Oculink扩展接口2;1051、1052-NMOS驱动电路;20-板卡;2011-主Oculink接口1;2012-主Oculink接口2;2021-PCIE中继器1;2022-PCIE中继器2;2023-PCIE中继器3;2024-PCIE中继器4;2031-时钟芯片1;2032-时钟芯片2;2033-时钟芯片3;2034-时钟芯片4;2041-Oculink扩展接口1;2042-Oculink扩展接口2;2043-Oculink扩展接口3;2044-Oculink扩展接口4;2051-NMOS驱动电路1;2052-NMOS驱动电路2;2053-NMOS驱动电路3;2054-NMOS驱动电路4。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有付出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

实施例一

图1为本发明一实施例中将一个Oculink接口扩展为两个的扩展方法示意图,如图1所示,本实施例提供了一种基于服务器PCIE信号扩展的方法,其将服务器上的两个主Oculink接口分别各自扩展为两个Oculink扩展接口,共扩展为四个Oculink扩展接口,其中任一个主Oculink接口扩展为两个Oculink扩展接口的扩展方法包括PCIE信号扩展方法、复位信号(RST)扩展方法和时钟信号(CLK)扩展方法,其中:

PCIE信号扩展方法的具体过程为:

步骤101:主Oculink接口(Oculink Connector A)(101)通过Oculink线缆(Cable)从服务器主机获取PCIE信号,并将获取到的两通路(Lane)PCIE×4分别传输到PCIE中继器(Repeater)1(1021)和PCIE中继器(Repeater)2(1022);

步骤102:任一PCIE中继器(Repeater)(1021或1022)将对应的一通路(Lane)PCIE×4扩展为两通路(Lane)PCIE×2,并同时传输到对应的Oculink扩展接口(1041或1042);

在本实施例中,其中,步骤102的具体传输过程为:

PCIE中继器(Repeater)1(1021)将对应的一通路(Lane)PCIE×4扩展为两通路(Lane)PCIE×2,并传输到Oculink扩展接口(Oculink Connector)1(1041);

PCIE中继器(Repeater)2(1022)将对应的一通路(Lane)PCIE×4扩展为两通路(Lane)PCIE×2,并传输到Oculink扩展接口(Oculink Connector)2(1042)。

复位信号(RST)扩展方法的具体过程为:

步骤200:主Oculink接口(Oculink Connector A)(101)将从服务器主机获取的两路复位信号(RST)分别通过NMOS(N-Metal-Oxide-Semiconductor,N型金属-氧化物-半导体)驱动电路传输到Oculink扩展接口1(1041)和Oculink扩展接口2(1042);

时钟信号(CLK)扩展方法的具体过程为:

步骤300:两个时钟(CLK)芯片(1031和1032)分别将从主Oculink接口(OculinkConnector A)(101)获取的时钟信号(CLK)分别传输到对应的Oculink扩展接口(1041或1042)。

在本实施例中,其中,步骤300中时钟信号(CLK)的传输过程具体为:

主Oculink接口(Oculink Connector A)(101)将时钟信号(CLK)分别传输到时钟(CLK)芯片1(1031)和时钟(CLK)芯片2(1032)的输入端,然后时钟(CLK)芯片1(1031)的两个输出端将时钟信号(CLK)输入到Oculink扩展接口1(1041),时钟(CLK)芯片2(1032)的两个输出端将时钟信号(CLK)输入到Oculink扩展接口2(1042)。

通过本实施例的扩展,主Oculink接口(101)的两通路(Lane)PCIE×4分别通过两个PCIE中继器(Repeater)扩展为四通路(Lane)PCIE×2,每两通路(Lane)PCIE×2又集成到一个Oculink扩展接口,共扩展两个Oculink扩展接口,复位信号(RST)和时钟信号(CLK)也分别通过NMOS驱动电路(NMOS)和时钟(CLK)芯片进行扩展,这样每个Oculink扩展接口(1041和1042)都可以获取到两个时钟信号(CLK)、两路复位信号(RST)和两通路(Lane)PCIE×2的输入。同理,另一个主Oculink接口也可以扩展两个Oculink扩展接口,从而实现两个主Oculink接口扩展为四个Oculink扩展接口,以供更多硬件设备接入。

实施例二

图2为本发明一实施例的设备架构图,如图2所示,本实施例提供了一种基于服务器PCIE信号扩展的设备,用以实现前述PCIE信号扩展的方法,其包括:

一板卡(20);

两个主Oculink接口,设置于板卡(20)上,用于与服务器主板连接,其分别为主Oculink接口1(2011)和主Oculink接口2(2012);

四个PCIE中继器(Repeater),设置于板卡(20)上,用于将一通路PCIE×4扩展为两通路PCIE×2,其分别为PCIE中继器1(2021)、PCIE中继器2(2022)、PCIE中继器3(2023)和PCIE中继器4(2024),其中,PCIE中继器1(2021)和PCIE中继器2(2022)与主Oculink接口1(2011)连接,PCIE中继器3(2023)和PCIE中继器4(2024)与主Oculink接口2(2012)连接;

四个Oculink扩展接口,设置于板卡(20)上,其分别为Oculink扩展接口1(2041)、Oculink扩展接口2(2042)、Oculink扩展接口3(2043)和Oculink扩展接口4(2044),其中,四个Oculink扩展接口(2041、2042、2043和2044)与四个PCIE中继器(Repeater)(2021、2022、2023和2024)对应连接;

多个NMOS驱动电路(2051、2052、2053和2054),设置于板卡(20)上,其分别为NMOS驱动电路1(2051)、NMOS驱动电路2(2052)、NMOS驱动电路3(2053)和NMOS驱动电路4(2054),其中,每个NMOS驱动电路分别与其中一个主Oculink接口和对应的Oculink扩展接口连接;

四个时钟芯片,设置于板卡(20)上,其分别为时钟芯片1(2031)、时钟芯片2(2032)、时钟芯片3(2033)和时钟芯片4(2034),其中,每个时钟芯片分别与其中一个主Oculink接口(2011或2012)和对应的Oculink扩展接口(2041、2042、2043或2044)连接。

在本实施例中,其中,每个主Oculink接口(2011和2012)包含两通道(Lane)PCIE×4。

在本实施例中,其中,每个Oculink扩展接口(2041、2042、2043和2044)包含两通道(Lane)PCIE×2。

在本实施例中,其中,四个Oculink扩展接口(2041、2042、2043和2044)与四个PCIE中继器(Repeater)(2021、2022、2023和2024)的具体连接方式为:

Oculink扩展接口1(2041)与PCIE中继器1(2021)连接,Oculink扩展接口2(2042)与PCIE中继器2(2022)连接,Oculink扩展接口3(2043)与PCIE中继器3(2023)连接,Oculink扩展接口4(2044)与PCIE中继器4(2024)连接。

在本实施例中,其中,每个NMOS驱动电路分别与其中一个主Oculink接口和对应的Oculink扩展接口的连接具体为:

NMOS驱动电路1(2051)分别与主Oculink接口1(2011)和Oculink扩展接口1(2041)连接,NMOS驱动电路2(2052)分别与主Oculink接口1(2011)和Oculink扩展接口2(2042)连接,NMOS驱动电路3(2053)分别与主Oculink接口2(2012)和Oculink扩展接口3(2043)连接,NMOS驱动电路4(2054)分别与主Oculink接口2(2012)和Oculink扩展接口4(2044)连接。

在本实施例中,其中,每个时钟芯片(2031、2032、2033和2034)包含一个输入端和两个输出端,每个时钟芯片的具体连接方式为:

时钟芯片1(2031)的输入端和时钟芯片2(2032)的输入端均连接到主Oculink接口1(2011),时钟芯片1(2031)的两个输出端与Oculink扩展接口1(2041)连接,时钟芯片2(2032)的两个输出端与Oculink扩展接口2(2042)连接;

时钟芯片3(2033)的输入端和时钟芯片4(2034)的输入端均连接到主Oculink接口2(2012),时钟芯片3(2033)的两个输出端与Oculink扩展接口3(2043)连接,时钟芯片4(2034)的两个输出端与Oculink扩展接口4(2044)连接。

在本实施例中,其中,每个主Oculink接口分别通过一条Oculink线缆与服务器主板连接,其中,每条Oculink线缆的长度可根据需求定制,本实施例不对其长度进行限定,以满足可以根据实际情况与不同接口的匹配需求,具有较高的灵活度。

本发明提出的基于服务器PCIE信号的扩展方法及设备,能够实现将两个Oculink接口扩展为四个Oculink接口,与现有技术相比,在完成扩展设备与服务器主板正常通信的基础上,还能够实现对服务器主板PCIE信号的扩展,提高服务器可搭配使用的外部设备的多样性,增加服务器密度,增强服务器的处理能力。

本领域普通技术人员可以理解:附图只是一个实施例的示意图,附图中的模块或流程并不一定是实施本发明所必须的。

本领域普通技术人员可以理解:实施例中的装置中的模块可以按照实施例描述分布于实施例的装置中,也可以进行相应变化位于不同于本实施例的一个或多个装置中。上述实施例的模块可以合并为一个模块,也可以进一步拆分成多个子模块。

最后应说明的是:以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明实施例技术方案的精神和范围。

- 一种基于服务器PCIE信号扩展的方法及设备

- 一种在刀片服务器上实现扩展PCIE卡或存储设备的设计方法