一种具有快速自动频率补偿的CPFSK解调装置及方法

文献发布时间:2023-06-19 11:45:49

技术领域

本发明属于无线遥测遥控领域,尤其是涉及一种具有快速自动频率补偿的CPFSK解调装置及方法。

背景技术

在航空航天的遥测领域,调频调制体制是使用最为广泛的调制体制,这是因为调频调制与调相调制等其他调制方法相比具有诸多优点。在数字通信系统中调频技术通常是指FSK(Frequency Shift Keying,频移键控),而CPFSK(Continuous Phase FrequencyShift Keying,连续相位频移键控)是一种特殊的FSK调制,CPFSK调制具有相位连续、包络恒定、带外衰减快和频带利用率高的优点。目前遥测领域使用的调频多为CPFSK调制技术;

在使用过程中,由于通信双方通常存在着快速度的移动,诸如导弹和卫星。快速运动会使的收发双方存在着多普勒频偏,另外考虑到收发双方的时钟的固有系统偏差,这些收发双方存在的频偏容易造成接收端判决错误,造成误码。因此在进行CPFSK解调的时候进行自动频率控制(AFC)能有效提高解调性能;

目前现有的CPFSK解调多采用非相干解调方法,这种解调方法在多普勒频偏较大的时候解调性能较差,也有一些解调方法具有一定的多普勒频偏抑制能力,但需要较长的积分和调整时间,频偏调整速度较慢,这些方法对于固定多普勒频偏的抑制能力尚可,但对具有较快多普勒变化率的应用场景的跟随能力较差。

发明内容

有鉴于此,本发明旨在提出一种具有快速自动频率补偿的CPFSK解调装置,以克服多普勒频偏对解调性能的影响,对多普勒频偏变化率对解调性能的影响同样有很好的抑制能力。

为达到上述目的,本发明的技术方案是这样实现的:

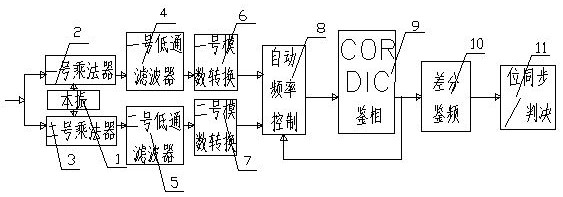

一种具有快速自动频率补偿的CPFSK解调装置,包括依次信号连接的预处理结构、捷变频芯片和FPGA芯片,所述捷变频芯片包括本振、一号乘法器、二号乘法器、一号低通滤波器、二号低通滤波器、一号模数转换和二号模数转换,本振两侧分别信号连接至一号乘法器输入端、二号乘法器输入端,一号乘法器输出端信号连接至一号低通滤波器输入端,一号低通滤波器输出端信号连接至一号模数转换输入端,一号模数转换输出端信号连接至FPGA芯片,二号乘法器输出端信号连接至二号低通滤波器输入端,二号低通滤波器输出端信号连接至二号模数转换输入端,二号模数转换输出端信号连接至FPGA芯片;

所述FPGA芯片包括依次信号连接的自动频率控制、cordic鉴相、差分鉴频和位同步/判决,自动频率控制的输入端分别信号连接至一号模数转换、二号模数转换、cordic鉴相。

进一步的,所述预处理结构包括依次信号连接的一号低噪声放大器、带通滤波器和二号低噪声放大器,一号低噪声放大器输入端用于接收射频信号,二号低噪声放大器输出端用于输出输入信号。

进一步的,所述自动频率控制包括依次信号连接的误差计算、三号低通滤波器、数字控制振荡器和复数乘法器,且误差计算输入端信号连接至cordic鉴相输出端,cordic鉴相输入端信号连接至复数乘法器输出端,复数乘法器输入端信号连接至一号模数转换、二号模数转换,误差计算、三号低通滤波器、数字控制振荡器、复数乘法器、cordic鉴相形成AFC环路控制。

相对于现有技术,本发明所述的一种具有快速自动频率补偿的CPFSK解调装置具有以下优势:

(1)本发明所述的一种具有快速自动频率补偿的CPFSK解调装置,该解调装置结构简单,设计合理,具有架构简洁、硬件资源消耗少,易于FPGA实现等诸多优点。

本发明的另一目的在于提出一种具有快速自动频率补偿的CPFSK解调方法,以解决需要较长的积分和调整时间,频偏调整速度较慢以及应用场景的跟随能力较差的问题。

为达到上述目的,本发明的技术方案是这样实现的:

一种具有快速自动频率补偿的CPFSK解调方法,包括以下步骤:

S1、将CPFSK解调装置启动,将射频信号通过预处理结构处理后得到输入信号;

S2、将输入信号、本振的正交信号分别传送至一号乘法器输入端、二号乘法器输入端,一号乘法器输入端接收到正交信号经相乘后输出一号幅度归一化信号,并将一号幅度归一化信号传送给一号低通滤波器,一号低通滤波器处理后得到一号模拟信号,并将一号模拟信号传送给一号模数转换,一号模数转换处理后得到一号数字信号,并将一号数字信号传送给自动频率控制,二号乘法器输入端接收到正交信号经相乘后输出二号幅度归一化信号,并将二号幅度归一化信号传送给二号低通滤波器,二号低通滤波器处理后得到二号模拟信号,并将二号模拟信号传送给二号模数转换,二号模数转换处理后得到二号数字信号,并将二号数字信号传送给自动频率控制;

S3、自动频率控制接收到信号,并经AFC环路控制后,得到复数表达式,并将复数表达式传送给cordic鉴相,cordic鉴相对复数表达式处理后得到cordic鉴相处理信号,并将cordic鉴相处理信号传送给差分鉴频,差分鉴频对cordic鉴相处理信号处理后得到差分鉴频信号,并将差分鉴频信号传送给位同步/判决,位同步/判决对差分鉴频信号处理后得到输出信号。

进一步的,在步骤S1中的所述输入信号的表达式为

进一步的,在步骤S2中的所述本振的正交信号为

进一步的,在步骤S2中的所述一号幅度归一化信号的表达式为

进一步的,在步骤S2中的所述一号模拟信号为

进一步的,在步骤S3中的所述复数表达式为

进一步的,在步骤S3中的所述鉴相处理信号为

相对于现有技术,本发明所述的一种具有快速自动频率补偿的CPFSK解调方法具有以下优势:

(1)本发明所述的一种具有快速自动频率补偿的CPFSK解调方法,该方法具有简单易实现、硬件资源消耗少、功耗低、体积小的特点。同时该方法不仅可以实现大范围的多普勒频偏的捕获和跟踪,还能实现较大范围的多普勒变化率跟踪。该发明的另一个特点就是每次误差电压的计算更新时间短,算法收敛速度快;该方法具有架构简洁、硬件资源消耗少,易于FPGA实现等诸多优点。

附图说明

构成本发明的一部分的附图用来提供对本发明的进一步理解,本发明的示意性实施例及其说明用于解释本发明,并不构成对本发明的不当限定。在附图中:

图1为本发明实施例所述的一种具有快速自动频率补偿的CPFSK解调装置及方法整体结构原理框图;

图2为本发明实施例所述的一种具有快速自动频率补偿的CPFSK解调装置及方法自动频率控制8内部细化原理框图;

图3为本发明实施例所述的一种具有快速自动频率补偿的CPFSK解调装置及方法中解调装置示意图。

附图标记说明:

1-本振;2-一号乘法器;3-二号乘法器;4-一号低通滤波器;5-二号低通滤波器;6-一号模数转换;7-二号模数转换;8-自动频率控制;9-cordic鉴相;10-差分鉴频;11-位同步/判决;12-误差计算;13-三号低通滤波器;14-数字控制振荡器;15-复数乘法器。

具体实施方式

需要说明的是,在不冲突的情况下,本发明中的实施例及实施例中的特征可以相互组合。

在本发明的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,术语“第一”、“第二”等仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”等的特征可以明示或者隐含地包括一个或者更多个该特征。在本发明的描述中,除非另有说明,“多个”的含义是两个或两个以上。

在本发明的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以通过具体情况理解上述术语在本发明中的具体含义。

下面将参考附图并结合实施例来详细说明本发明。

如图1至图3所示,一种具有快速自动频率补偿的CPFSK解调方法,包括以下步骤:

S1、将一种具有快速自动频率补偿的CPFSK解调装置启动,一种具有快速自动频率补偿的CPFSK解调装置包括依次信号连接的预处理结构、捷变频芯片和FPGA芯片;

所述捷变频芯片包括本振1、一号乘法器2、二号乘法器3、一号低通滤波器4、二号低通滤波器5、一号模数转换6和二号模数转换7,本振1两侧分别信号连接至一号乘法器2输入端、二号乘法器3输入端,一号乘法器2输出端信号连接至一号低通滤波器4输入端,一号低通滤波器4输出端信号连接至一号模数转换6输入端,一号模数转换6输出端信号连接至FPGA芯片,二号乘法器3输出端信号连接至二号低通滤波器5输入端,二号低通滤波器5输出端信号连接至二号模数转换7输入端,二号模数转换7输出端信号连接至FPGA芯片;

所述FPGA芯片包括依次信号连接的自动频率控制8、cordic鉴相9、差分鉴频10和位同步/判决11,自动频率控制8的输入端分别信号连接至一号模数转换6、二号模数转换7、cordic鉴相9;

S2、将射频信号通过预处理结构处理后得到输入信号;

S3、将输入信号、本振1的正交信号分别传送至一号乘法器2输入端、二号乘法器3输入端,一号乘法器2输入端接收到正交信号经相乘后输出一号幅度归一化信号,并将一号幅度归一化信号传送给一号低通滤波器4,一号低通滤波器4处理后得到一号模拟信号,并将一号模拟信号传送给一号模数转换6,一号模数转换6处理后得到一号数字信号,并将一号数字信号传送给自动频率控制8,二号乘法器3输入端接收到正交信号经相乘后输出二号幅度归一化信号,并将二号幅度归一化信号传送给二号低通滤波器5,二号低通滤波器5处理后得到二号模拟信号,并将二号模拟信号传送给二号模数转换7,二号模数转换7处理后得到二号数字信号,并将二号数字信号传送给自动频率控制8;

S4、自动频率控制8接收到信号,并经AFC环路控制后,得到复数表达式,并将复数表达式传送给cordic鉴相9,cordic鉴相9对复数表达式处理后得到cordic鉴相处理信号,并将cordic鉴相处理信号传送给差分鉴频10,差分鉴频10对cordic鉴相处理信号处理后得到差分鉴频信号,并将差分鉴频信号传送给位同步/判决11,位同步/判决11对差分鉴频信号处理后得到输出信号,该解调方法的输入信号是来自于硬件中频或者零中频正交信号通过ADC芯片转换而来的数字信号,该信号通过一个AFC环路控制后,经过CORDIC鉴相和差分鉴频后通过位同步模块完成CPFSK解调,该方法具有简单易实现、硬件资源消耗少、功耗低、体积小的特点。同时该方法不仅可以实现大范围的多普勒频偏的捕获和跟踪,还能实现较大范围的多普勒变化率跟踪。该发明的另一个特点就是每次误差电压的计算更新时间短,算法收敛速度快;该方法具有架构简洁、硬件资源消耗少,易于FPGA实现等诸多优点。

如图3所示,在步骤S1中的所述预处理结构包括依次信号连接的一号低噪声放大器、带通滤波器和二号低噪声放大器,一号低噪声放大器输入端用于接收射频信号,二号低噪声放大器输出端用于输出输入信号,射频信号首先通过一号低噪声放大器进行初次信号放大,信号放大后经过一号带通滤波抑制带外噪声;之后信号经过二号低噪声放大器再次进行信号放大,信号之后接着进入捷变频芯片,在该芯片中完成下变频,低通滤波以及AD转换功能。随后数字化之后的信号进入FPGA芯片进行其余信号处理过程。信号处理完成输出输出信号,即解调之后的PCM信号。

在步骤S1中的所述自动频率控制8包括依次信号连接的误差计算12、三号低通滤波器13、数字控制振荡器14和复数乘法器15,且误差计算12输入端信号连接至cordic鉴相9输出端,cordic鉴相9输入端信号连接至复数乘法器15输出端,复数乘法器15输入端信号连接至一号模数转换6、二号模数转换7,误差计算12、三号低通滤波器13、数字控制振荡器14、复数乘法器15、cordic鉴相9形成AFC环路控制,在实际解调中,误差计算12、三号低通滤波器13、数字控制振荡器14和复数乘法器15均为自动频率控制8的内部细化模块,从而简化CPFSK解调装置结构,提高CPFSK解调装置实用性。

误差计算12的原理是,首先对cordic鉴相9输出的信号

误差计算12的误差计算更新时间短,算法收敛速度快,进一步提高了本发明的解调速度。

三号低通滤波器13将计算误差12输出的误差电压

在步骤S2中的所述输入信号的表达式为

在步骤S3中的所述本振1的正交信号为

在步骤S3中的所述一号幅度归一化信号的表达式为

在步骤S3中的所述一号模拟信号为

在步骤S4中的所述复数表达式为

在步骤S4中的所述鉴相处理信号为

实施例1

射频信号首先通过一号低噪声放大器TQP3M9036进行初次信号放大,信号放大后经过带通滤波器CBP-2250A+,抑制带外噪声,中心频点为2250Mhz,带宽为100Mhz。信号经过二号低噪声放大器GALI-S66+再次进行信号放大。信号接着进入捷变频芯片AD9361BBCZ,在该芯片中完成下变频,低通滤波以及AD转换功能。随后数字化之后的信号进入FPGA芯片XC7A100T-2CSG324进行其余信号处理过程。信号处理完成输出解调之后的PCM信号。

以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 一种具有快速自动频率补偿的CPFSK解调装置及方法

- 一种具有快速自动频率补偿的CPFSK解调装置及方法