用于直接连接到PCB的嵌入式IC芯片的制造方法

文献发布时间:2023-06-19 12:14:58

本申请要求于2018年10月16日提交的美国临时专利第62/746,189号的权益,其全部内容通过引用合并于本文中。

技术领域

本发明的领域涉及用于制造电路的方法和系统。

背景技术

以下描述包括可用于理解本发明的信息。不承认本文提供的任何信息是现有技术或者与当前要求保护的发明有关,也不承认明确或隐含引用的任何出版物是现有技术。

电路(例如,印刷电路板等)的制造是具有不断创新的高度竞争的领域。例如,授予Kozlovski的WO 2018/140517教导了形成具有空腔的基板,在空腔中放置集成电路(IC)和其他的元件,形成将IC和元件互连的导电图案,并用介电层覆盖元件和导电图案。但是,Kozlovski没有教导,将IC嵌入到基板(例如,可光成像的介电材料(PID))中,并且在基板上制作孔或者过孔以将IC(例如,I/O端口)与电路连接,并且电镀导体以形成电路。

授予Baron等人的EP 1622435教导了在基板或者介电材料中制作用于元件或者IC的凹槽以及沟槽或者过孔,并且教导了将元件或者IC插入到凹槽中,并且利用介电材料将元件封装在凹槽中。然后将导体镀到沟槽或者过孔上。然而,Baron没有教导在没有导体图案的情况下嵌入IC,并且没有教导使用PID和光烧蚀来形成构成电路的催化剂图案以及将导体电镀到催化剂上以形成与IC或者电气元件连接的电路的结合。

本文所标识的所有出版物通过引用的方式并入,就如同具体地、单独地指出通过引用将每个单独的出版物或者专利申请并入一样。当在并入的参考文献中术语的定义或者使用与本文提供的该术语的定义不一致或者相反时,本文提供的该术语的定义适用,而参考文献中该术语的定义不适用。

因此,仍然需要用于制造电路的具有电气元件的部分的改进的方法和系统。

发明内容

本发明的主题提供了用于制造电路的部分的装置、系统和方法。第一介电材料层,优选地是可光成像的,沉积在基板上,并且在第一介电材料层中形成第一空腔。将电气元件沉积在第一空腔中,并将第二介电材料层(例如可光成像的)沉积在电气元件上,优选地将电气元件嵌入到介电材料中。在第二介电材料层中形成第二空腔,并将催化剂(例如,Pt、Pd、Ag、Au、Cu、Ni、Co、Rh、In、Sn、合金或者它们的组合等)沉积在第二介电材料层上,优选地,使催化剂的部分与电气元件的至少一部分接触。催化剂沉积在厚度不超过50nm的层(任选地,连续层)上,优选地厚度不超过25nm,更优选地厚度不超过10nm。将导体(例如,Cu、合金等)沉积(例如,无电、电解等)在催化剂的暴露部分上,形成电路的部分。在优选的实施例中,导体与电气元件直接接触,例如与元件的I/O端口直接接触。导体的沉积或镀覆可以任选地通过电解电镀来加速。

可以预期,本发明主题的方法可以用于形成电路的具有嵌入在介电材料中的多个电气元件的部分,无论是否在同一层中(例如,嵌入在第一介电材料层中的第一电气元件和第二电气元件)、在相邻层中(例如,第一层中的第一电气元件、第二层中的第二电气元件等)、或者在单独的不相邻层中(例如,第一介电材料层中的第一电气元件、第三介电材料层中的第二电气元件、以及在第一层与第二层之间的第二介电材料层)。

在一些实施例中,通过在电气元件上沉积第一催化剂、在第一催化剂的部分上形成第一介电材料层、在第一催化剂的暴露部分上沉积第一导体来制造电路的部分。第二催化剂沉积在第一介电材料层上,使得第二催化剂的部分接触第一导体,第二导体沉积在第二催化剂的暴露部分上。可以去除第一介电材料层的部分以形成第一催化剂的暴露部分(例如,电路图案等)上。也可以将第二介电材料层沉积在第二催化剂上,并且去除第二介电材料层的部分,从而形成第二催化剂的暴露部分。

考虑了用于制造电路的部分的另外的方法,例如在基板上沉积第一介电材料层,在第一介电材料层中形成第一空腔,在第一空腔中沉积电气元件。催化剂沉积在电气元件的至少一部分和第一介电材料层上,导体沉积在催化剂的暴露部分上。第二介电材料层也可以沉积在电气元件上,且将第二介电材料层的部分去除以形成催化剂的暴露部分。导体优选地与电气元件直接接触,更优选地与电气元件的I/O端口直接接触。

还设想了通过在电气元件上沉积第一介电材料层、在第一介电材料层中形成第一空腔、在第一介电材料层上沉积催化剂使得催化剂的部分与电气元件的部分接触来制造电路的部分。导体也沉积(例如无电镀)在催化剂的暴露部分上。可以通过在催化剂上沉积第二介电材料层并且去除第二介电材料层的部分来形成催化剂的暴露部分。导体优选地与电气元件直接接触,更优选地与电气元件的I/O端口直接接触。

通过以下对优选实施例的详细描述以及附图,本发明主题的各种目的、特征、方面和优点将变得更加显而易见,在附图中,相同的附图标记表示相同的元件。

附图说明

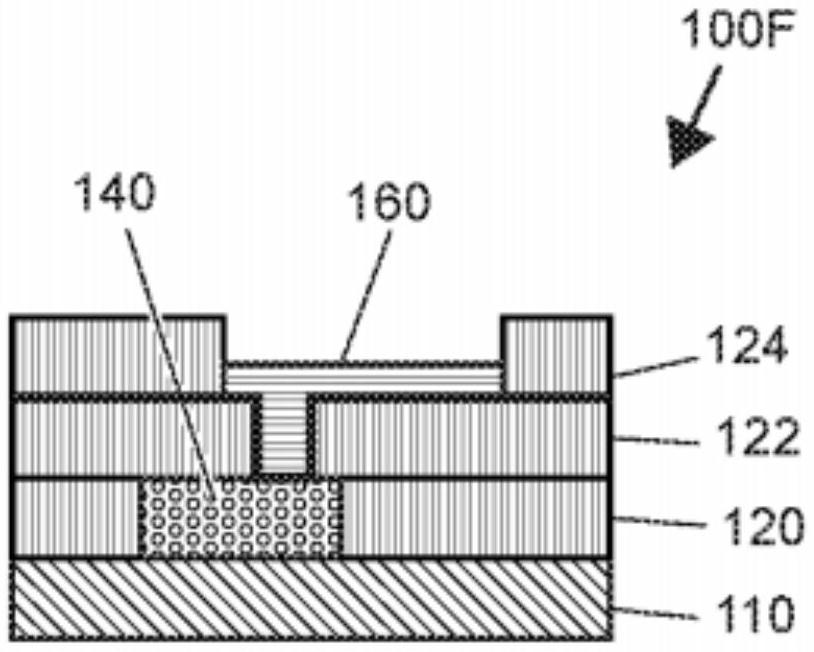

图1A-图1F描绘了本发明主题的过程中的步骤。

图2A-图2D描绘了本发明主题的另一过程中的步骤。

图3A-图3F描绘了本发明主题的又一个方法中的步骤。

图4A-图4F描绘了本发明主题的再一个方法中的步骤。

图5描绘了本发明主题的电路的部分。

图6描绘了本发明主题的另一电路的部分。

图7描绘了本发明主题的又一电路的部分。

图8A-图8E描绘了本发明主题的另一过程中的步骤。

具体实施方式

本发明的主题提供了用于制造电路的部分的装置、系统和方法。第一介电材料层,优选地是可光成像的,沉积在基板上,在第一介电材料层中形成第一空腔。将电气元件沉积在第一空腔中,并且将第二介电材料层(例如可光成像的)沉积在电气元件上,优选地将电气元件嵌入到介电材料中。在第二介电材料层中形成第二空腔,并且将催化剂(例如,Pt、Pd、Ag、Au、Cu、Ni、Co、Rh、In、Sn、合金或者它们的组合等)沉积在第二介电材料层上,优选地使催化剂的部分与电气元件的至少一部分接触。催化剂沉积在厚度不超过50nm的层(任选地,连续层)中,优选地厚度不超过25nm,更优选地厚度不超过10nm。将导体(例如,Cu、合金等)沉积(例如,无电、电解等)在催化剂的暴露部分上,形成电路的部分。在优选的实施例中,导体与电气元件直接接触,例如与元件的I/O端口直接接触。导体的沉积或镀覆可以任选地通过电解电镀来加速。

在一些实施例中,第三介电材料层(例如,可光成像的)沉积在催化剂上,并且去除第三介电材料层的部分以形成催化剂的暴露部分。从另一个角度看,以去除第三介电材料层的部分来以电路图案的形状暴露催化剂的方式,创建电路图案。第二空腔(例如,电路图案)优选地暴露电气元件的至少一部分,例如电气元件的I/O端口。

空腔,无论是第一空腔、第二空腔、还是两者,优选地通过机械烧蚀、热烧蚀或者光刻中的一种来制造,但是也可以通过任何适当的方法或技术来形成。电气元件是集成电路、电阻器、电容器、电感器或者表面安装元件中的一种,但是可以考虑它们的组合或者其他元件。

可以预期,第一介电材料层具有与电气元件大致相同的厚度,例如100μm、75μm、50μm、25μm、10μm或5μm或者更小。然而,不包含电气元件的介电材料层(例如,包含过孔、通孔、导体等的层)通常较薄,例如薄至2μm或者1μm。

在一些实施例中,抗镀层沉积在催化剂的部分上以形成催化剂的暴露部分。从另一个角度看,抗镀层覆盖催化剂的部分,同时留下可用于镀(例如无电镀)导体的催化剂的暴露部分。将导体(和任选的抗镀层)接地(例如,机械接地),使其大致与第二介电材料层齐平。将第二催化剂沉积在第二介电材料层和导体上,并且将第二导体沉积(例如,无电镀)在第二催化剂的暴露部分上。通常通过将第三介电材料层沉积在第二催化剂层上,以及通过去除第三介电材料层的部分来暴露第二催化剂的部分,来形成第二催化剂的暴露部分。从另一个角度看,电路图案是从第三介电材料层中蚀刻出来的,从而以图案的形状暴露催化剂。

可以预期,本发明主题的方法可以用于形成多个电气元件嵌入到介电材料中的电路的部分,无论是否在同一层中(例如,第一电气元件和第二电气元件嵌入到第一介电材料层中)、相邻层中(例如,第一层中的第一电气元件、第二层中的第二电气元件等)、或者单独的不相邻层中(例如,第一介电材料层中的第一电气元件、第三介电材料层中的第二电气元件、以及在第一层与第二层之间的第二层介电材料层)。

例如,在第一介电材料层中形成第三空腔,在第三空腔中沉积第二电气元件,并且在第二电气元件上沉积第二介电材料层。在第二介电材料层中形成第四空腔,并沉积催化剂,使得催化剂的第二部分与第二电气元件的部分接触。导体沉积在催化剂的第二暴露部分上(例如,电路图案)。可以在催化剂上进一步沉积第三介电材料层,并且去除第三介电材料层的部分以形成催化剂的暴露部分和催化剂的第二暴露部分。在优选的实施例中,导体与两个电气元件直接接触,更优选地与I/O端口直接接触。

在一些实施例中,在第二介电材料层中形成第三空腔,在第三空腔中沉积第二电气元件,并且沉积催化剂,使得催化剂的第二部分与第二电气元件的部分接触。导体沉积(例如无电镀)在催化剂的第二暴露部分上。可以通过将第三介电材料层沉积在催化剂上,以及去除第三介电材料层的部分,来形成催化剂的暴露部分,从而形成催化剂的暴露部分。导体优选地与两个电气元件直接接触,更优选地与每个元件的I/O端口直接接触。

类似地,去除第三介电材料层的部分以形成第三空腔,第二电气元件沉积在第三空腔中,第四介电材料层沉积在导体和第二电气元件上。进一步去除第四介电材料层的部分,并在第四介电材料层上沉积第二催化剂,以使第二催化剂与导体的部分和第二电气元件的部分接触。第二导体沉积在第二催化剂的暴露部分上。第二催化剂的暴露部分可以通过将第五介电材料层沉积到第二催化剂上来形成,并且去除第五介电材料层的部分以形成暴露部分。

在一些实施例中,通过将第一催化剂沉积到电气元件上、在第一催化剂的部分上形成第一介电材料层、以及将第一导体沉积到第一催化剂的暴露部分上,来制造电路的部分。第二催化剂沉积在第一介电材料层上,使得第二催化剂的部分与第一导体接触,第二导体沉积在第二催化剂的暴露部分上。可以去除第一介电材料层的部分以形成第一催化剂的暴露部分(例如,电路图案等)。也可以在第二催化剂上沉积第二介电材料层,并且去除第二介电材料层的部分,从而形成第二催化剂的暴露部分。

设想了用于制造电路的部分的其他方法,例如将第一介电材料层沉积到基板上,在第一介电材料层中形成第一空腔,将电气元件沉积在第一空腔中。将催化剂沉积在电气元件的至少一部分和第一介电材料层上,将导体沉积在催化剂的暴露部分上。第二介电材料层也可以沉积在电气元件上,并且去除第二介电材料层的部分以形成催化剂的暴露部分。导体优选地与电气元件直接接触,更优选地与电气元件的I/O端口直接接触。

还设想了通过将第一介电材料层沉积在电气元件上、在第一介电材料层中形成第一空腔、以及在第一介电材料层上沉积催化剂来制造电路的部分,使得催化剂的部分与电气元件的部分接触。导体也沉积(例如无电镀)在催化剂的暴露部分上。可以通过将第二介电材料层沉积在催化剂上并且去除第二介电材料层的部分来形成催化剂的暴露部分。导体优选地与电气元件直接接触,更优选地与电气元件的I/O端口直接接触。

还可以预期,所描述的方法可以应用于电气元件的反面。例如,可以去除基板的放置有电气元件的部分,以暴露电气元件底部的附加端口。如所描述的,可以形成催化剂图案,并且导体被镀覆以形成电路的附加部分。同样地,电气元件放置在介电材料层(例如可光成像的)上时,可以去除电介质层的部分,并形成催化剂图案以镀覆导体,从而形成附加电路。

本发明涉及用于制造电路的具有电气元件的部分的方法、系统和设备。

图1A至图1F描绘了用于制造电路的具有电气元件的部分的步骤。图1A描绘了在基板110上具有电介质层120、在电介质层120中具有空腔130的组件100A。可以想到的是,组件100在制造电路之前被组装。然而,在优选实施例中,组件100是通过将电介质层120沉积在基板110上并且去除电介质层120的部分以形成空腔130的方式形成的。空腔130优选地通过介电材料120的光烧蚀来形成,其优选地是可光成像的(PID)。然而,也可以使用替代技术,例如热消融或铣削。在一些实施例中,基板110可以具有已经沉积在空腔130中的附加导体线,以提供用于电气元件到电路的附加连接性。

图1B描绘了组件100B进一步包括集成电路(IC)140。IC 140沉积在空腔130中。从另一个角度看,空腔130具有最小尺寸,以使IC 140可以装配到空腔130中,且IC 140的顶表面基本上与电介质层120齐平。因此,可以想到,空腔130比IC 140的尺寸稍大,例如1μm或者更小。在一些实施例中,用表面催化剂或者导线对IC 140进行预处理,以实现与电路的附加连接性。

图1C描绘了组件100C,其进一步包括具有空腔132的电介质层122。电介质层122沉积在电介质层120和IC 140上。空腔132通过去除电介质层122的部分以暴露IC 140的部分(例如IC 140的I/O端口)来形成。电介质层122优选地是PID,并且通过在空腔132所需的位置处对电介质层122进行光烧蚀来形成空腔132。

图1D描绘了组件100D,其进一步包括催化剂层150,优选地是连续层。催化剂层150沉积在电介质层122、空腔132的壁和IC 140的暴露部分上,厚度通常不超过50nm。尽管催化剂层通常包含钯或者铂,但是可以考虑其他合适的材料、合金或者组合,包括例如银、金、铜、镍、钴、铑、铟、锡及其合金或者组合。

图1E描绘了组件100E,该组件进一步包括具有空腔134的电介质层124。电介质层124以连续层的形式沉积在催化剂层150上。优选地通过经由PID的光烧蚀去除电介质层124的部分以暴露催化剂150的部分来形成空腔134。催化剂150的暴露部分与IC 140的部分直接接触,并且以其他方式形成电路的部分的图案。

图1F描绘了组件100F,该组件还包括沉积在催化剂150的暴露部分上的导体160,形成了电路的部分。可以想到,导体160通过无电镀沉积到催化剂层150上,但是也可以通过电解电镀来加速镀覆。导体160通常是铜或者其合金,但是也可以考虑使用其他导体。如图所示,导体160与IC 140,通常是IC 140的I/O端口直接接触。

应当理解,所描述的方法可以进一步应用于组件100F,以将电路的部分添加到组件100F上。例如,可以穿过基板110制作过孔,以暴露IC140上的附加端口。一旦暴露,则将附加催化剂层沉积到IC 140的暴露的附加端口上,在催化剂层上创建电路图案,并且镀覆附加导体。

图2A至图2D描绘了用于制造电路的具有电气元件的部分的附加步骤。图2A描绘了包括IC 210和电介质层220的组件200A。IC 210可以如先前公开的那样嵌入在介电材料中,或者可以是独立的。电介质层220进一步包括空腔230。空腔230是通过去除电介质层220的部分,优选地通过PID的光烧蚀而形成的。空腔230暴露IC 210的部分,通常是IC 210的I/O端口。

图2B描绘了进一步包括催化剂层240的组件200B。催化剂层240优选地沉积为连续的催化剂层,例如钯或者铂,沉积在电介质层220、空腔230的壁和IC 210的部分上(例如,I/O端口),但可以使用其他的或者替代的催化剂。

图2C描绘了组件200C,其还包括具有空腔232的电介质层222。电介质层作为连续层沉积在催化剂层240上,并且通常是PID。通过去除电介质层220的部分以暴露催化剂240的部分来形成空腔232,优选地通过PID的光烧蚀来形成。催化剂240的暴露部分通常以设计的电路图案成形。

图2D描绘了组件200D,其还包括沉积在催化剂层240的暴露部分上的导体250,形成电路的导体部分。可以想到,导体250通过无电镀沉积到催化剂层240的暴露部分,但是也可以通过电解电镀来加速镀覆。导体250通常是铜或者其合金,但是也可以考虑使用其他导体。如图所示,导体250直接与IC 210,通常是与IC 210的I/O端口接触。

应当理解,所描述的方法可以进一步应用于组件100F,以将电路的部分添加到组件200D上。例如,催化剂可以沉积在IC 210的下侧,电路图案可以形成在催化剂上,并且导体可以被镀覆。

图3A至图3F描绘了用于制造电路的具有电气元件的部分的其他步骤。图3A描绘了组件300A,其包括IC 310、电介质层320、空腔330和催化剂层340。IC 310可以如先前公开的那样嵌入在介电材料中,或者可以是独立的。组件300A可以如先前公开的那样形成(例如,在IC 310上沉积电介质层320,形成空腔330,并且在电介质层320、空腔330的壁和IC 310的暴露部分上沉积催化剂层320)。

图3B描绘了组件300B,该组件300B还包括抗镀层350。抗镀层沉积在催化剂层340上,使得催化剂层340的位于空腔330内以及与空腔330邻近的部分被暴露。

图3C描绘了组件300C,其进一步包括沉积在催化剂340的暴露部分上的导体360,形成与IC 310的直接接触。可以想到,导体360通过无电镀沉积到催化剂层340的暴露部分,但是也可以通过电解电镀来加速镀敷。导体360通常是铜或者其合金,但是也可以考虑使用其他导体。如图所示,导体360与IC 310,通常是与IC 310的I/O端口直接接触。

图3D描绘了组件300D,其中抗镀层350已被去除,导体360的部分已被去除。通过机械研磨去除抗镀层350和导体360,以使导体360的顶表面与电介质层320基本齐平。催化剂层342进一步沉积在电介质层320和导体360上。

图3E描绘了组件300E,其还包括电介质层322和空腔370。电介质层322沉积在催化剂层342上,并且去除电介质层322的部分从而以电路的部分的图案暴露催化剂层342的部分。通过去除电介质层322的部分,通常通过PID的光烧蚀,来形成空腔342。

图3F描绘了组件300F,其还包括沉积到催化剂层342上的导体362,形成电路的部分。可以想到,导体360通过无电镀沉积到催化剂层342的暴露部分,但是也可以通过电解电镀来加速镀覆。导体360通常是铜或者其合金,但是也可以考虑使用其他导体。如图所示,导体360和导体362构成与IC 310直接接触的电路,通常是与IC 310的I/O端口直接接触的电路。

图4A至图4F描绘了用于制造电路的具有电气元件的部分的附加方法。图4A描绘了组件400A,其包括IC 410和催化剂层420。可以预期的是,IC可以嵌入在电介质层中,如先前所公开的,或者可以是独立的。催化剂层420优选地是连续的,并且包含如前所述的催化剂。

图4B描绘了组件400B,其还包括电介质层430和空腔440。组件400B如先前所公开的那样形成(例如,在IC 410上沉积电介质层430,形成空腔440,例如,通过PID的光烧蚀)。空腔440暴露催化剂层420的在IC410的部分,优选地I/O端口上的部分。

图4C描绘了组件400C,其还包括沉积到催化剂层420的暴露部分的导体450,与IC410形成直接接触。可以想到,导体450通过无电镀沉积在催化剂层420的暴露部分上,但是也可以通过电解电镀来加速。导体450通常是铜或者其合金,但是也可以考虑使用其他导体。如图所示,导体450与IC 410直接接触,通常与IC 410的I/O端口直接接触。

图4D描绘了组件400D,其还包括沉积在电介质层430和导体450上的催化剂层422。催化剂层422优选地是如前所述的催化剂的连续层。

图4E描绘了组件400E,其还包括电介质层432和空腔442。电介质层432沉积在催化剂层422上,并且通过去除电介质层432的部分来以电路的部分的图案暴露催化剂层422的部分。通过去除电介质层432的部分来形成空腔442,通常是通过PID的光烧蚀来形成。

图4F描绘了组件400F,其还包括形成电路的部分的导体452。可以想到,导体452通过无电镀沉积到催化剂层422的暴露部分,但是也可以通过电解电镀来加速镀覆。导体452通常是铜或者其合金,但是也可以考虑使用其他导体。如图所示,导体450和导体452构成与IC 410直接接触的电路,通常与IC 410的I/O端口直接接触。

应当理解,如本文所述的用于制造电路的部分的方法可以用于制造电路的包括多个电气元件的部分,例如包括两个IC的部分。图5描绘了在基板510上具有IC 540和IC 542的组件500,并嵌入到电介质层520和电介质层522中,其中IC 540和IC 542的一部分通过导体550,优选地通过IC 540和IC 542的I/O端口连接。在该实施例中,IC 540和IC 542位于电介质层520中,电介质层524和电介质层526包围导体550。

图6描绘了可以使用本文公开的方法制造的电路的附加部分。组件600具有IC 640和IC 642,其中IC 640在电介质层620中的基板610上,IC 642在电介质层622中。IC 640和IC 642的部分通过导体650连接,优选地,通过IC 640和IC 642的I/O端口连接。在该实施例中,IC 640和IC 642位于两个相邻的电介质层620和电介质层622中,电介质层624和电介质层626包围导体650。

图7描绘了可以使用本文公开的方法制造的电路的附加部分。组件700具有IC 740和IC 742,其中IC 740在电介质层720中的基板710上,IC 742在电介质层724中。IC 740和IC 742的部分通过导体750连接,优选地,通过IC 740和IC 742的I/O端口连接。在此实施例中,IC 740和IC 742位于两个不相邻的电介质层670和电介质层724中,电介质层722、电介质层726、电介质层728和电介质层729包围导体750。

图8A至图8E公开了用于制造电路的具有电气元件的部分的附加方法。图8A描绘了组件800A,其具有基板810、电介质层820和空腔830。空腔830如本文所述形成,例如通过光烧蚀(PID)电介质层820的部分形成。

图8B描绘了组件800B,其还具有IC 840。IC 840沉积在空腔830中,与IC 840的尺寸至少相同,尽管IC 840的边缘与空腔830之间可能存在间隙。

图8C描绘了组件800C,其还包括沉积在电介质层820和IC 840上的催化剂层850。优选地,催化剂层850是本文公开的连续D催化剂层。

图8D描绘了组件800D,其还包括电介质层822和空腔832。电介质层822以连续层的形式沉积在催化剂层850上。通过去除电介质层822D部分,优选地通过PID的光烧蚀以暴催化剂850的部分,来形成空腔832。催化剂850的暴露部分与IC 840的部分直接接触,优选地与I/O端口直接接触,并且以其他方式形成用于电路的部分的图案。

图8E描绘了组件800E,其还包括沉积到催化剂层850上的导体860,形成电路的部分。可以想到,导体860通过无电镀沉积到催化剂层850的暴露部分上,但是也可以或者可选地通过电解电镀来加速镀覆。导体860通常是铜或者其合金,但是也可以考虑使用其他导体。如图所示,导体860与IC 840直接接触,通常是与IC 840的I/O端口直接接触。

该讨论提供了本发明主题的许多示例实施例。尽管每个实施例代表发明元件的单个组合,但是本发明主题被认为包括所公开元件的所有可能的组合。因此,如果一个实施例包括元件A、B和C,第二实施例包括元件B和D,那么即使没有明确地公开,本发明的主题也被认为包括A、B、C或者D的其他剩余组合。

如在此使用的,并且除非上下文另外指出,否则术语“耦合到”旨在包括直接耦合(其中彼此耦合的两个元件彼此接触)和间接耦合(其中至少一个附加元件位于两个元件之间)。因此,术语“耦合到”和“与……耦合”同义地使用。

在一些实施例中,用于描述和要求保护本发明的某些实施例的表示成分数量,例如浓度、反应条件等性质的数字应理解为在某些情况下被术语“大约”修饰。因此,在一些实施例中,在书面说明书和所附权利要求书中阐述的数字参数是近似值,其可以根据特定实施例试图获得的期望特性而变化。在一些实施例中,应该根据所报告的有效数字的数目并通过应用普通的舍入技术来解释数字参数。尽管列出本发明的一些实施例的广泛范围的数值范围和参数是近似值,但是在具体示例中列出的数值被尽可能精确地报告。在本发明的一些实施例中呈现的数值可能包含某些误差,这些误差必定是由它们各自的测试测量中发现的标准偏差引起的。

除非上下文有相反的指示,否则本文阐述的所有范围应解释为包括其端点,并且开放式范围应解释为仅包括商业上实用的值。同样,除非上下文有相反的指示,否则所有值列表都应视为包括中间值。

如在本文的描述和随后的整个权利要求书中所使用的,除非上下文另外明确指出,否则“一个”、“一种”和“该”的含义包括复数形式。另外,如本文的说明书中所使用的,除非上下文另有明确指出,否则“在......中”的含义包括“在......中”和“在......上”。

除非本文另外指出或上下文明显矛盾,否则本文描述的所有方法可以以任何合适的顺序执行。相对于本文的某些实施例提供的任何和所有示例或示例性语言(如“例如”)的使用仅旨在更好地阐明本发明,并且不对以其他方式要求保护的本发明的范围构成限制。说明书中的任何语言都不应被解释为表示对实施本发明必不可少的任何未要求保护的要素。

本文公开的本发明的替代元素或者实施例的分组不应被解释为限制。每个组成员可以单独引用或者要求保护,也可以与该组的其他成员或者此处找到的其他元素组合地引用或者要求保护。出于方便和/或可专利性的原因,一个组中的一个或者多个成员可以包含在组中或者从组中删除。当发生任何这样的包含或者删除时,说明书在本文中被认为包含经修改从而满足所附权利要求中使用的所有马库什组的书面描述的组。

对于本领域的技术人员显而易见的是,在不背离本文的发明构思的前提下,除了已经描述的修改之外,还可以进行更多修改。因此,除了所附权利要求的精神之外,本发明的主题不受限制。此外,在解释说明书和权利要求书时,应以与上下文一致的尽可能广泛的方式解释所有术语。特别地,术语“包括”和“包含”应被解释为以非排他性的方式指代元素、元件或步骤,指示所引用的元素、元件或者步骤可以存在、被利用或者与其他未明确引用的元素、元件或者步骤组合。在说明书的权利要求书提到选自包括A、B、C……和N的组中的至少一个,该文本应解释为仅需要组中的一个元素,而不是A加N或者B加N,等等。

- 用于直接连接到PCB的嵌入式IC芯片的制造方法

- 带IC标签的片材的制造方法、带IC标签的片材的制造装置、带IC标签的片材、IC芯片的固定方法、IC芯片的固定装置、以及IC标签