阵列基板及其制作方法、显示面板

文献发布时间:2023-06-19 12:25:57

技术领域

本发明实施例涉及显示技术领域,尤其涉及一种阵列基板及其制作方法、显示面板。

背景技术

指纹识别技术已广泛应用于中小尺寸的显示面板中,该技术主要包括电容式、超声波式和光学式等几种类型。目前较为成熟的类型是电容式指纹识别技术,其工作原理是利用硅晶圆与导电的皮下电解液形成电场,指纹谷脊的高低不同导致电场的压差不同,从而实现准确的指纹识别。但是,对于电容式指纹识别技术,当手指湿润的时候,其识别效果会显著变差。超声波式指纹识别技术相较于电容式指纹识别技术而言,具有更高穿透能力、更稳定和更精确等优点,但是其成本较高。光学式指纹识别技术的工作原理是利用光的折射和反射原理,照射到手指上的光被手指反射至感光传感器,由于指纹谷脊对光的反射不同,因此感光传感器接收到指纹谷和指纹脊的反射光强不同,从而实现准确的指纹识别。光学式指纹识别技术相较于电容式指纹识别技术而言,具有更高穿透能力、更稳定和更精确等优点,并且,其相较于超声波式指纹识别技术而言,具有更低成本的优点。然而,目前基于光学式指纹识别技术的显示面板的制作过程具有工艺繁琐的缺陷。

发明内容

因此,有必要提供一种阵列基板及其制作方法、显示面板,用以解决现有的基于光学指纹识别技术的显示面板的制作过程工艺繁琐的问题。

第一方面,本发明实施例提供一种阵列基板,包括:

基底,包括控制元件;

第三金属层,设于所述基底上,所述第三金属层包括第一电极,所述第一电极与所述控制元件电连接;

二极管,设于所述第一电极上;

第一绝缘层,设于所述第三金属层和所述二极管上;

第四金属层,设于所述第一绝缘层上,所述第四金属层包括第二电极,所述第二电极与所述二极管对应设置,且与所述二极管电连接;

第二绝缘层,设于所述第一绝缘层和所述第四金属层上。

在一些实施例中,所述第三金属层还包括触控电极线,所述第四金属层还包括与所述第二电极一体设置的公共电极,所述公共电极与所述触控电极线对应设置,且与所述触控电极线电连接。

在一些实施例中,所述基底还包括开关元件,所述阵列基板还包括第五金属层,所述第五金属层设于所述第二绝缘层上,所述第五金属层包括像素电极,所述像素电极与所述开关元件电连接。

在一些实施例中,所述第一绝缘层设置有第一通孔以暴露至少部分所述二极管,所述第二电极通过所述第一通孔与所述二极管电连接。

在一些实施例中,所述第一绝缘层设置有第二通孔以暴露至少部分所述触控电极线,所述公共电极通过所述第二通孔与所述触控电极线电连接。

在一些实施例中,所述基底与所述第三金属层之间设置有平坦层,所述平坦层、所述第一绝缘层和所述第二绝缘层设置有第三通孔,所述像素电极通过所述第三通孔与所述开关元件电连接。

在一些实施例中,所述控制元件为第一薄膜晶体管,所述第一电极与所述第一薄膜晶体管的源极或漏极电连接,所述开关元件为第二薄膜晶体管,所述像素电极与所述第二薄膜晶体管的源极或漏极电连接。

在一些实施例中,所述第一电极在所述基底上的正投影覆盖所述二极管在所述基底上的正投影,所述第二电极在所述基底上的正投影与所述第一电极在所述基底上的正投影至少部分重叠。

在一些实施例中,所述第一电极在所述基底上的正投影和所述第二电极在所述基底上的正投影分别与所述控制元件在所述基底上的正投影至少部分重叠。

在一些实施例中,所述第一薄膜晶体管还包括有源层,所述第一电极在所述基底上的正投影与所述有源层在所述基底上的正投影至少部分重叠。

在一些实施例中,所述二极管为PIN二极管,所述PIN二极管包括第一半导体层和本征半导体层,所述第一半导体层设于所述第一电极上,所述本征半导体层设于所述第一半导体层上。

在一些实施例中,所述PIN二极管还包括第二半导体层,所述第二半导体层设于所述本征半导体层上。

第二方面,本发明实施例提供一种阵列基板的制作方法,包括:

提供基底,所述基底包括控制元件;

在所述基底上制备第三金属层,所述第三金属层包括第一电极,所述第一电极与所述控制元件电连接;

在所述第一电极上制备二极管;

在所述第三金属层和所述二极管上制备第一绝缘层;

在所述第一绝缘层上制备第四金属层,所述第四金属层包括第二电极,所述第二电极与所述二极管对应设置,且与所述二极管电连接;

在所述第一绝缘层和所述第四金属层上制备第二绝缘层。

第三方面,本发明实施例提供一种显示面板,所述显示面板包括第一方面所述的阵列基板。

本发明实施例提供的阵列基板包括:基底,包括控制元件;第三金属层,设于基底上,第三金属层包括第一电极,第一电极与控制元件电连接;二极管,设于第一电极上;第一绝缘层,设于第三金属层和二极管上;第四金属层,设于第一绝缘层上,第四金属层包括第二电极,第二电极与二极管对应设置,且与二极管电连接;第二绝缘层,设于第一绝缘层和第四金属层上。本发明实施例提供的阵列基板,平坦层上的绝缘层仅有第一绝缘层和第二绝缘层这两层绝缘层,相较于现有技术中平坦层上需要设置至少四层绝缘层的方案,本发明实施例减少了平坦层上的绝缘层的数量,从而在阵列基板的制作过程中节省了光罩数量,简化了制作工艺。

附图说明

为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

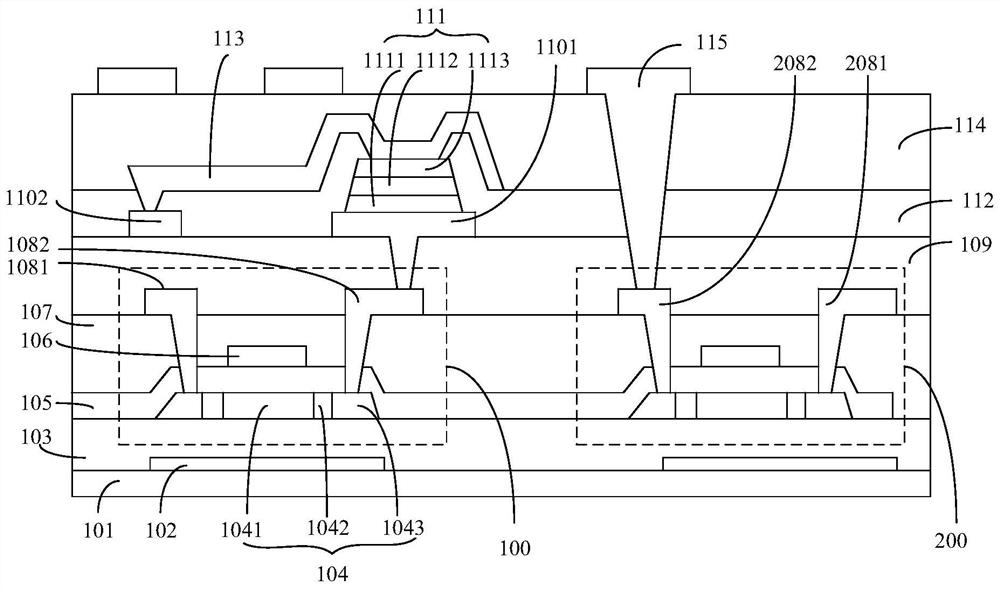

图1为本发明实施例提供的阵列基板的剖面示意图;

图2为本发明实施例提供的阵列基板的制作方法流程图;

图3为本发明实施例提供的阵列基板的制作工艺流程图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

请参阅图1,图1为本发明实施例提供的阵列基板的剖面示意图。图1所示的阵列基板包括基底、第三金属层、二极管111、第一绝缘层112、第四金属层和第二绝缘层114。

基底包括控制元件100,控制元件100优选为薄膜晶体管,将该薄膜晶体管称为第一薄膜晶体管。基底可包括衬底基板101、第一有源层104、栅绝缘层105、第一金属层和第二金属层。此外,基底还可包括遮光层102、缓冲层103和层间介质层107中的任意一种或多种。

衬底基板101可为刚性基板或柔性基板,衬底基板101的材料可包括玻璃、二氧化硅、聚乙烯、聚丙烯、聚苯乙烯、聚乳酸、聚对苯二甲酸乙二醇酯、聚酰亚胺和聚氨酯中的任意一种或多种。

遮光层102设于衬底基板101上,遮光层102的材料可为金属材料。

缓冲层103设于衬底基板101和遮光层102上,缓冲层103的材料可为氮化硅或氧化硅。

第一有源层104设于缓冲层103上且对应遮光层102设置,具体而言,遮光层102在基底上的正投影覆盖第一有源层104在基底上的正投影。第一有源层104包括位于中间的多晶硅区1041、位于两端的N型重掺杂区1043以及位于多晶硅区1041与N型重掺杂区1043之间的N型轻掺杂区1042。

栅绝缘层105设于缓冲层103和第一有源层104上,栅绝缘层105的材料可为氮化硅、氧化硅或有机光阻。

第一金属层设于栅绝缘层105上,第一金属层包括第一栅极106,第一栅极106对应第一有源层104设置,具体而言,第一有源层104在基底上的正投影覆盖第一栅极106在基底上的正投影。第一金属层的材料可为铜、铝或钛。

层间介质层107设于栅绝缘层105和第一金属层上,层间介质层107的材料可为氮化硅或氧化硅。

第二金属层设于层间介质层107上,第二金属层包括第一源极1081和第一漏极1082,第一源极1081对应第一有源层104中位于其中一端的N型重掺杂区1043设置,且与该N型重掺杂区1043电连接,第一漏极1082对应第一有源层104中位于另外一端的N型重掺杂区1043设置,且与该N型重掺杂区1043电连接。第二金属层的材料可与第一金属层的材料相同。

基底与第三金属层之间设置有平坦层109,具体而言,平坦层109设于层间介质层107和第二金属层上,平坦层109的材料可为氮化硅、氧化硅或有机光阻。

第三金属层设于平坦层109上,第三金属层包括第一电极1101,第一电极1101与控制元件100电连接。具体而言,第一电极1101与第一薄膜晶体管的第一源极1081或第一漏极1082电连接,图1所示的第一电极1101与第一薄膜晶体管的第一漏极1082电连接。第三金属层的材料可为钛、铝、钼和铜等金属中的任意一种,还可为钛-铝-钛、钼-铜或钼-铝-钼等金属叠层材料。

二极管111设于第一电极1101上,二极管111优选为PIN二极管,PIN二极管包括第一半导体层1111和本征半导体层1112,第一半导体层1111设于第一电极1101上,本征半导体层1112设于第一半导体层1111上,其中,第一半导体层1111的材料优选为N型非晶硅(N+a-Si),本征半导体层1112的材料优选为非晶硅(a-Si)。此外,PIN二极管还可包括第二半导体层1113,第二半导体层1113设于本征半导体层1112上,第二半导体层1113的材料优选为P型非晶硅(P+a-Si)。

第一绝缘层112设于第三金属层和二极管111上,第一绝缘层112的材料可为氮化硅或氧化硅。

第四金属层设于第一绝缘层112上,第四金属层包括第二电极113,第二电极113与二极管111对应设置且与二极管111电连接。具体而言,第二电极113在基底上的正投影至少与第一电极1101在基底上的正投影部分重叠。第四金属层的材料优选为氧化铟锡。

第二绝缘层114设于第一绝缘层112和第四金属层上,第二绝缘层114的材料可为氮化硅或氧化硅。

需要说明的是,上述第一有源层104、第一栅极106、第一源极1081和第一漏极1082共同组成控制元件100,也即第一薄膜晶体管。上述第一电极1101、PIN二极管和第二电极113共同组成感光传感器。由于PIN二极管中的本征半导体层1112的材料为非晶硅,而非晶硅可以制作得比较厚,因此有利于光的吸收,便于形成高性能的感光传感器,从而提高指纹识别的准确性。

本发明实施例提供的阵列基板,平坦层109上的绝缘层仅有第一绝缘层112和第二绝缘层114这两层绝缘层,相较于现有技术中平坦层109上需要设置至少四层绝缘层的方案,本发明实施例减少了平坦层109上的绝缘层的数量,从而在阵列基板的制作过程中节省了光罩数量,简化了制作工艺。

在一些实施例中,第三金属层还包括触控电极线1102,触控电极线1102与第三金属层中的第一电极1101间隔设置。具体而言,第三金属层包括间隔设置的第一电极1101和触控电极线1102,其中,第一电极1101作为感光传感器的下电极,触控电极线1102用作触控电极的引线。

第四金属层还包括与第二电极113一体设置的公共电极,公共电极与触控电极线1102对应设置且与触控电极线1102电连接。具体而言,第四金属层包括第二电极113以及与第二电极113一体设置的公共电极,其中,第二电极113作为感光传感器的上电极,公共电极用于使显示面板正常显示。

本发明实施例提供的阵列基板,公共电极和第二电极113的引线都采用触控电极线1102,在同一时刻,触控电极线1102只服务于公共电极或第二电极113,相较于现有技术中公共电极和第二电极113分别采用不同的引线的方案,本发明实施例实现了引线复用,减少了阵列基板内空间的占用。

在一些实施例中,基底还包括开关元件200,开关元件200优选为薄膜晶体管,将该薄膜晶体管称为第二薄膜晶体管。第二薄膜晶体管包括第二有源层、第二栅极、第二源极2081和第二漏极2082。其中,第二有源层与第一薄膜晶体管中的第一有源层104同层制作,第二漏极2082位于第三金属层,也即第二薄膜晶体管的第二源极2081和第二漏极2082,与第一薄膜晶体管的第一源极1081和第一漏极1082同层制作。此外,第二薄膜晶体管的第二栅极可与第一薄膜晶体管的第一栅极106同层制作,还可与第一薄膜晶体管的第一栅极106非同层制作,本发明实施例对此不作具体限定。

阵列基板还包括第五金属层,第五金属层设于第二绝缘层114上,第五金属层包括像素电极115,像素电极115与开关元件200电连接,也即像素电极115与第二薄膜晶体管电连接,具体而言,像素电极115与第二薄膜晶体管中的第二源极2081或第二漏极2082电连接,图1所示的像素电极115与第二薄膜晶体管中的第二漏极2082电连接。其中,像素电极115的材料优选为氧化铟锡。

在一些实施例中,第一绝缘层112设置有第一通孔(图1未示出)以暴露至少部分二极管111,第二电极113通过第一通孔与二极管111电连接。

在一些实施例中,第一绝缘层112设置有第二通孔(图1未示出)以暴露至少部分触控电极线1102,公共电极通过第二通孔与触控电极线1102电连接。

在一些实施例中,平坦层109、第一绝缘层112和第二绝缘层114设置有第三通孔(图1未示出),像素电极115通过第三通孔与开关元件200电连接。

本发明实施例提供的阵列基板,用于连接第二电极113与二极管111的第一通孔以及用于连接公共电极与触控电极线1102的第二通孔均为深度较浅的通孔(简称浅孔),这些浅孔均可在制备第四金属层之前制备,用于连接像素电极115与第二薄膜晶体管中的第二漏极2082的第三通孔为深度较深的通孔(简称深孔),该深孔可在制备第二绝缘层114之后制备,相较于现有技术中同时制备深浅孔的方案,本发明实施例避免了深浅孔同时蚀刻带来的制程风险。

在一些实施例中,第一电极1101在基底上的正投影覆盖二极管111在基底上的正投影,第二电极113在基底上的正投影与第一电极1101在基底上的正投影至少部分重叠,从而能够提高感光传感器的灵敏度。

在一些实施例中,第一电极1101在基底上的正投影和第二电极113在基底上的正投影分别与控制元件100在基底上的正投影至少部分重叠,以提高阵列基板的开口率。

在一些实施例中,第一薄膜晶体管还包括第一有源层104,第一电极1101在基底上的正投影与第一有源层104在基底上的正投影至少部分重叠。具体而言,第一电极1101在基底上的正投影至少覆盖部分与第一漏极1082电连接的N型重掺杂区1043在基底上的正投影,从而提高阵列基板的开口率。

请参阅图2和图3,图2为本发明实施例提供的阵列基板的制作方法流程图,图3为本发明实施例提供的阵列基板的制作工艺流程图。结合图2和图3,本发明实施例提供的制作方法包括以下步骤:

S1,提供基底,所述基底包括控制元件100。

具体地,S1包括以下步骤:

S101,提供衬底基板101,衬底基板101可为刚性基板或柔性基板,衬底基板101的材料可包括玻璃、二氧化硅、聚乙烯、聚丙烯、聚苯乙烯、聚乳酸、聚对苯二甲酸乙二醇酯、聚酰亚胺和聚氨酯中的任意一种或多种。

S102,在衬底基板101上制备遮光层102,具体地,使用金属材料覆盖衬底基板101,然后采用曝光蚀刻等方式将金属材料图案化,得到遮光层102。

S103,在衬底基板101和遮光层102上制备缓冲层103,缓冲层103的材料可为氮化硅或氧化硅。

S104,在缓冲层103上制备第一有源层104,具体地,使用单晶硅(a-Si)覆盖缓冲层103,然后对单晶硅进行准分子激光退火,将单晶硅转化为多晶硅(poly Si),然后采用曝光蚀刻等方式将多晶硅图案化,然后对图案化后的多晶硅的两端进行磷(P)离子掺杂形成N型重掺杂区1043,得到第一有源层104。

S105,在缓冲层103和第一有源层104上制备栅绝缘层105,栅绝缘层105的材料可为氮化硅、氧化硅或有机光阻。

S106,在栅绝缘层105上制备第一金属层,具体地,使用金属材料例如铜、钛或铝覆盖栅绝缘层105,然后采用曝光蚀刻等方式将金属材料图案化,得到包含第一栅极106的第一金属层。

S107,对第一有源层104进行N-离子掺杂,在N型重掺杂区1043和多晶硅之间形成N型轻掺杂区1042。

S108,在栅绝缘层105和第一金属层上制备层间介质层107,层间介质层107的材料可为氮化硅或氧化硅。

S109,在层间介质层107和栅绝缘层105中制备通孔,以分别与第一有源层104中位于两端的N型重掺杂区1043对应。

S110,在层间介质层107上制备第二金属层,具体地,使用金属材料例如铜、钛或铝覆盖层间介质层107并使金属材料分别通过层间介质层107和栅绝缘层105中的通孔电连接至第一有源层104中位于两端的N型重掺杂区1043,然后将金属材料图案化,得到包含第一源极1081和第一漏极1082的第二金属层。

需要说明的是,上述步骤中省略了开关元件200的制作过程,但开关元件200的制作过程可与控制元件100的制作过程类似,此处不再赘述,开关元件200可与控制元件100同时制作,也可与控制元件100非同时制作,此处不作限定。但需要说明的是,包含开关元件200的基底的第二金属层还包括第二源极2081和第二漏极2082。

需要说明的是,在步骤S1和S2之间,该制作方法还包括:在层间介质层107和第二金属层上制备平坦层109,平坦层109的材料可为氮化硅、氧化硅或有机光阻,并在平坦层109中制备通孔以与第一漏极1082对应。

S2,在基底上制备第三金属层,第三金属层包括第一电极1101,第一电极1101与控制元件100电连接。

具体地,使用金属材料覆盖平坦层109并使金属材料通过平坦层109中的通孔电连接至第一漏极1082,然后将金属材料图案化,得到包含第一电极1101的第三金属层。其中,金属材料可为钛、铝、钼和铜等金属中的任意一种,还可为钛-铝-钛、钼-铜或钼-铝-钼等金属叠层材料。

需要说明的是,该步骤中的第三金属层还包括触控电极线1102,触控电极线1102与第三金属层中的第一电极1101间隔设置。

S3,在第一电极1101上制备二极管111。

具体地,在第一电极1101上依次制备第一半导体层1111和本征半导体层1112,并将第一半导体层1111和本征半导体层1112图案化,得到PIN二极管。其中,第一半导体层1111的材料优选为N型非晶硅,本征半导体层1112的材料优选为非晶硅。此外,在图案化之前,还可在本征半导体层1112上制备第二半导体层1113,将第一半导体层1111、本征半导体层1112和第二半导体层1113图案化,得到PIN二极管。其中,第二半导体层1113的材料优选为P型非晶硅。

S4,在第三金属层和二极管111上制备第一绝缘层112。其中,第一绝缘层112的材料可为氮化硅或氧化硅。

需要说明的是,在S4之后并在S5之前,还需要在第一绝缘层112中制备第一通孔和第二通孔,其中,第一通孔与PIN二极管对应,第二通孔与触控电极线1102对应。

S5,在第一绝缘层112上制备第四金属层,第四金属层包括第二电极113,第二电极113与二极管111对应设置,且与二极管111电连接。

具体地,使用金属材料例如氧化铟锡覆盖第一绝缘层112并使金属材料通过第一通孔电连接至PIN二极管,然后将金属材料图案化,得到包含第二电极113的第四金属层。需要说明的是,若PIN二极管仅包括第一半导体层1111和本征半导体层1112,则金属材料电连接至本征半导体层1112,若PIN二极管包括第一半导体层1111、本征半导体层1112和第二半导体层1113,则金属材料电连接至第二半导体层1113。

需要说明的是,该步骤中的第四金属层还包括与第二电极113一体设置的公共电极,公共电极通过第二通孔与触控电极线1102电连接。

S6,在第一绝缘层112和第四金属层上制备第二绝缘层114。其中,第二绝缘层114的材料可为氮化硅或氧化硅。

需要说明的是,上述第一有源层104、第一栅极106、第一源极1081和第一漏极1082共同组成控制元件100,也即第一薄膜晶体管。上述第一电极1101、PIN二极管和第二电极113共同组成感光传感器。由于PIN二极管中的本征半导体层1112的材料为非晶硅,而非晶硅可以制作得比较厚,因此有利于光的吸收,便于形成高性能的感光传感器,从而提高指纹识别的准确性。

在S6之后,该制作方法还包括以下步骤:

S7,在平坦层109、第一绝缘层112和第二绝缘层114中制备第三通孔。

S8,在第二绝缘层114上制备像素电极115,所述像素电极115通过第三通孔电连接至第二漏极2082。

具体地,使用金属材料例如氧化铟锡覆盖第二绝缘层114并使金属材料通过第三通孔电连接至第二漏极2082,然后将金属材料图案化,得到包含像素电极115的第四金属层。

本发明实施例还提供一种显示面板,该显示面板包括上述任一实施例所述的阵列基板。该显示面板可为液晶显示面板,该显示面板还包括第二基板,第二基板优选为彩膜基板。第二基板与阵列基板相对设置,阵列基板与第二基板之间还设有液晶层。

本发明实施例提供还提供一种显示装置,该显示装置包括上述任一实施例所述的显示面板、控制电路和壳体。需要说明的是,该显示装置并不限于以上内容,其还可以包括其他器件,比如还可以包括摄像头和天线结构等。

其中,显示面板设置于壳体上。

在一些实施例中,显示面板可以固定到壳体上,显示面板和壳体形成密闭空间,以容纳控制电路等器件。

在一些实施例中,壳体可以为由柔性材料制成,比如为塑胶壳体或者硅胶壳体等。

其中,该控制电路安装在壳体中,该控制电路可以为显示装置的主板,控制电路上可以集成有电池、天线结构、麦克风、扬声器、耳机接口、通用串行总线接口、摄像头、距离传感器、环境光传感器、受话器以及处理器等功能组件中的任意一个或多个。

其中,该显示面板安装在壳体中,同时,该显示面板电连接至控制电路上,以形成显示装置的显示面。该显示面板可以包括显示区域和非显示区域。该显示区域可以用来显示显示装置的画面或者供用户进行触摸操控等。该非显示区域可用于设置各种功能组件。

该显示装置包括但不限定于手机、平板电脑、计算机显示器、游戏机、电视机、显示屏幕、可穿戴设备及其他具有显示功能的生活电器或家用电器等。

最后应说明的是:以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。