用于检查间歇阻抗变化的连接测试装置及方法

文献发布时间:2023-06-19 11:44:10

技术领域

本发明涉及一种用于检查第一和/或第二线路中的间歇阻抗变化的连接测试装置及方法。

背景技术

现有的带连接插头的线缆束,尤其是有许多个体线材或线材网络的那种,通常是用自动连接测试仪在制作和维护期间来检查的。

标准的连接测试仪检查个体线材中的连接或是包括多个个体线材的线材网络中的连接是否以低电阻连接到连接插头的插头触点。这样的连接测试仪还能够检查在非互联的个体线材之间的绝缘是否为高电阻。

这些连接测试仪通常由程序来控制。程序控制测试序列,并记录测试和测试结果。程序一般适合待测试的线缆束以及适合线缆束的连接数据。测试序列有时能够从线缆束的电路图直接生成。

在具有许多个体线材的线缆束中,必须要检查大量的连接。人工检查和记录线缆束容易出错且耗时,并因此已不常见。

根据GB2529456A已知一种用于检测线路中的间歇故障的测试仪以及针对这样的间歇故障的模拟系统。所述模拟系统生成电阻变化,以检查所述测试仪的多个测试通道。

根据GB2531268A已知一种用于监控和显示针对间歇故障的测试装置的状态。

US2010/268507A1描述了一种用于检测电子系统的多线材连接中的故障的方法和装置。所述装置能够检测持续和间歇故障;其包括能够连接到测试目标中的不同测试点的多个端口,具有多个多路复用器的开关模块,以及万用表,其能够经由所述多路复用器连接到各个测试点。

根据WO2020/125996A1已知一种用于检查具有若干网络的线缆束的方法和装置。所述网络包括若干电气模块。该已知的方法包括对所述网络施加AC电压信号,测量被施加以AC电压信号的每个网络的电流和电压,将基于每个所测量的电流和每个所测量的电压而生成的各个网络的I-V曲线与针对对应网络的缺省目标I-V曲线进行比较,以及若基于每个所测量的电流和每个所测量的电压而生成的I-V曲线中的一个偏离所对应的目标I-V曲线大于缺省阈值,则输出错误讯息。

发明内容

因此,本发明的目标在于提供一种连接测试装置,其同时地并且因此快速地检查动态线路故障,所述动态线路故障为个体线路中的以及具有许多线路的线缆束中的间歇阻抗变化的形式,即,该装置缩短了测试时间,并且该装置还能够经济地制作,尤其是无需昂贵的精密测量装置并且无需开关矩阵或多路复用器。

根据本发明,提供一种根据权利要求1的用于检查第一和/或第二线路中的间歇阻抗变化的连接测试装置。根据本发明的所述连接测试装置尤其包括发射器。所述发射器可以包括用于生成测试信号的测试信号发生器,以及用于连接所述第一或第二线路的第一测试点,其中所述测试信号发生器能够将所述测试信号经由所述第一测试点提供给所述第一或第二线路。根据本发明的所述连接测试装置还尤其包括第一接收器。所述接收器实质上包括用于连接所述第一或第二线路的第二测试点,以及经由所述第二测试点接收来自所述第一或第二线路的呼入信号的接收器前端。根据本发明的所述连接测试装置一般还包括评价逻辑,其连接到所述接收器前端并且能够将输入信号与阈值进行比较,以识别所述第一线路和/或所述第二线路中的间歇阻抗变化。

术语“检查”实质上应当包含检验第一线路为无故障的意思。没有故障可以被表达为“存在”或“不存在”,或者更具体地被表达为“间歇阻抗变化存在”或“间歇阻抗变化不存在”,或者还要更具体地被表达为“断开存在”或“断开不存在”或者“短路存在”或“短路不存在”。不同于术语“测量”,术语“检查”可以不包含确定准确测量值的意思。术语“检查”也可以包含“测试”或“确定”的意思。

术语“连接”可以包含“耦合”的意思。特别地,将“连接”理解为意味着“电气连接”“导电连接”或“电气耦合”。本发明中两个相连接的元件,例如评价逻辑与接收器前端,在存在诸如插头、开关、滤波器等等的中间元件时,也尤其应当被视为是互连的。

术语“阻抗”应当尤其包含“AC电阻”的意思;Z=R+jX,其中R为阻抗的实部并且X为阻抗的虚部;

术语“间歇”可以包含“间歇”“递减”“有间断”“按时间间隔出现”和/或“暂时”的意思。

所述第一线路和所述第二线路或者所述第一线材和所述第二线材每个实质上都包括第一线端和第二线端。所述第一线路和所述第二线路每个都可以包括线缆网络,在其中存在多个第一和/或第二线端。所述第一线路和所述第二线路可以包括插入式连接器,其中第一插入式连接器尤其连接到所述第一线端,和/或第二插入式连接器连接到所述第二线端。所述第一测试点可以连接到所述第一线端或者连接到所述第一或第二线路的所述第一插入式连接器。所述第二测试点可以连接到所述第二线端或者连接到所述第一或第二线路的所述第二插入式连接器。所述第一线路和所述第二线路每个一般都具有在所述第一与第二线端之间的阻抗。此外,所述第一和第二线路每个都可以包括绝缘护套。带有绝缘护套的线路可以被称作线缆。多个线缆一起可以形成线缆束。

阻抗可以由于各种原因而改变。这些原因包含错误的焊点、冷焊点、插入式连接器中的一个上错误的压接、所述第一线路中接触第二线路的非绝缘点、线缆破损、绝缘损坏、未完全插入的插入式连接、不良触点,等等。在作用于所述第一线路的具体环境影响下产生的阻抗变化一般被称作暂时的、间歇的或动态的。这样的具体环境影响的例子包含:低温(例如在77.4K以下)、热、光、湿气、水、凝露、腐蚀、机械应力(振动、冲击、震击、加速)、海洋性气候、沙、尘。例如可以将测试台用于使所述第一线路和/或所述第二线路经受人工生成的环境影响,以检查在环境影响期间的阻抗变化。例如,根据本发明的所述连接测试装置因此可以被用于同时检查经受振动的线缆束中所有线路的阻抗。所述连接测试装置可以包括计算机,尤其是连接到所述评价逻辑的那种。所述计算机可以自然地和/或在人工生成的环境影响的强度下接收数据。根据另外的优选实施例,所述计算机尤其分析相对于所述人工生成的环境影响的阻抗变化。所述计算机因此能够确定所述人工生成的环境影响与所述阻抗变化之间的相关性。

所述测试信号实质上是在所述第一线端提供的,并且在所述第二线端通过所述第一线材的所述阻抗被转换成输入信号。

标准测试装置通常仅有一个测量装置,其经由开关矩阵顺序地连接到多个线路。根据本发明的所述连接测试装置可以包括多个发射器和多个接收器,用于并行或同时地并且因此而快速地检查多个线路。

标准测试装置通常依赖于精确且昂贵的万用表或阻抗测量仪器。根据本发明的所述连接测试装置能够整体上或部分地作为IC来制作,例如作为FPGA(现场可编程门阵列)或ASIC(专用集成电路)。根据本发明的所述连接测试装置因此可以得以经济地制作并且可以快速测试许多线路。

根据优选的实施例,所述接收器前端包括RC元件。所述RC元件可以拾取来自所述第二测试点的AC电压信号,其中所述AC电压信号实质上形成所述输入信号。R一般代表欧姆电阻器或端接阻抗并且C代表电容器。所述电阻器或所述端接阻抗以及所述电容器尤其是并联的。流向所述第二测试点并通过所述电阻器的电流尤其引起所述电阻器上的电压降。所述电容器闭锁所述电压降中的DC电压分量,并且实质上仅向所述评价逻辑传送所述电压降中的AC分量,即所述输入信号。作为替代方案,可以用换能器或变压器代替所述RC元件,或是除所述RC元件之外还使用换能器或变压器。

在本发明另外的进展中,所述评价逻辑可以包括至少第一比较器,其将所述输入信号与可设定的第一阈值进行比较。不足所述第一阈值可以指示所述第一或第二线路中的断开。更确切地说,所述第一比较器可以将所述AC电压信号与电压阈值进行比较。如果所述AC电压信号达不到最小电压,这实质上意味着较预期更小的电流流过所述第一或第二线材和所述电阻器。这可以意味着在所述第一或第二线路中阻抗的暂时升高,即,所述第一或第二线路中的断开。所述第一比较器优选地输出二进制比较结果。例如,在所述AC电压信号超过所述阈值的情况中,所述二进制比较结果为0。例如,在所述AC电压信号在所述阈值以下的情况中,所述二进制比较结果为1。所述比较结果可以被存储在存储器中。所述存储器可以依次存储多个比较结果。所述评价逻辑包括时钟。所述时钟可以被配置为连续计数器。所述多个比较结果每个都可以与由所述时钟生成的时间戳一起被存储在所述存储器中。加法器可以加和(即计数)多个比较结果,并把它们存储在所述存储器中。所述FPGA可以包括所述存储器和所述加法器。

也有可能检测所述第一或第二线路中的静态故障,将其与动态故障区分开,并同样对其计数,例如在所述故障仍然存在,但具体可编程时间已因前一信号改变而过去时。

根据优选的设计,所述测试信号尤其包括DC电压。所述第一线材或所述第二线材一般具有初始线路常数或线路浪涌阻抗或阻抗。所述阻抗可以因不同原因和/或环境影响而变化。施加在所述第一或第二线路上的所述DC电压一般会引起所述线材中的DC电流。然而,如果在所施加的DC电压期间发生临时阻抗变化,这实质上导致电流变化,其可以被所述接收器评价为AC分量或非DC分量。

在有利的另外的进展中,所述测试信号发生器包括识别信号发生器,其生成唯一识别信号。所述识别信号可以与所述DC电压加和,或被用于调制所述DC电压,并形成所述测试信号。所述识别信号优选地以叠加形式出现在所述呼入信号中。所述接收器可以解码所述识别信号,并将其分配给所述测试信号发生器或发射器的所述测试信号。如果根据本发明的所述连接测试装置包括用于检查多个线路的多个发射器和接收器,则所述接收器可以使用所述识别信号将所述呼入信号分配给特定测试信号发生器或发射器各自的测试信号。

在另一实施例中,所述测试信号发生器尤其包括混频器和振荡器,其中所述混频器将所述识别信号与由所述振荡器生成的载波信号进行混合,以尤其形成BPSK调制高频信号。特别地,所述测试信号发生器包括用于生成唯一识别码的基带发生器;不归零(NRZ)编码器,其连接到所述基带发生器并将所述唯一识别码编码在AC信号或NRZ信号中;所述混频器,其连接到所述NRZ编码器和振荡器,并且其接收所述NRZ信号和所述载波信号并混合二者以形成所述高频信号;加法器,其加和所述DC电压与所述高频信号,第一功率放大器,其放大所述高频信号,以及第一开关,其可以选择性地将所述第一功率放大器连接到所述第一测试点,并且其选择性地将经放大的高频信号导通到所述第一测试点,其中经放大的高频信号形成所述测试信号。

所述测试信号发生器可以无限循环地向所述第一测试点输出所述识别码。

此外,所述测试信号发生器尤其包括第二开关,所述第二开关禁用所述高频信号和/或所述基带发生器,从而所述测试信号发生器仅生成具有所叠加的识别信号的所述DC电压信号,或仅生成所述DC电压信号,其中具有所叠加的识别信号的所述DC电压信号或所述DC电压信号借助于所述第一功率放大器被放大,并且可以作为测试信号经由所述第一开关被选择性地输出给所述第一测试点。所述DC电压信号尤其适用于检查所述第一或第二线路中是否存在断开或动态阻抗上升。

根据另外的进展,所述接收器尤其包括识别信号解调器。所述识别信号解调器可以包括下变频器,其接收所述输入信号和所述载波信号,并通过所述载波信号的频率将所述输入信号降频转换为下变频器输出信号;积分器,其连接到所述下变频器,接收所述下变频器输出信号,在位周期上对其进行积分并将其输出为积分器输出信号;阈值鉴频器,其连接到所述积分器,接收所述积分器输出信号,将其与位中心的分辨阈值进行比较并输出数字信号,以及基带分析单元,其连接到所述阈值鉴频器,接收所述数字信号,并分析所述数字信号是否包含识别码,以及如果是的话包含哪个识别码。所述基带分析单元可以使用所述识别码将所述呼入信号唯一地分配给所述发射器的所述测试信号,或者在有多个发射器的情况中,将所述呼入信号唯一地分配给所述多个发射器中特定的一个的所述测试信号。

所述接收器还可以包括滤波器,其连接在所述RC元件与所述评价逻辑之间。所述滤波器可以衰减所述呼入信号中的所述识别信号。所述滤波器包括,例如,高通滤波器、带通滤波器或基带滤波器。所述衰减可以防止所述识别信号到达所述评价逻辑而导致在所述评价逻辑处错误的阈值比较。所述滤波器可以并联到旁路通路。第二开关可以连接在该并联电路与所述RC元件之间。所述第二开关可以选择性地将所述呼入信号切换到所述滤波器或切换到所述滤波器周围的所述旁路通路。不加滤波,所述评价逻辑能够维持所述输入信号具有最大带宽。在未将高频信号叠加到所述输入信号的情况中,最大带宽可以是有用的。

可以在由所述旁路通路和所述滤波器组成的所述并联电路与所述评价逻辑之间连接另外的功率放大器,其放大所述输入信号或经滤波的输入信号,并将其作为放大的输入信号提供给所述评价逻辑。

尤其借助于数字调制方法,例如相移键控(PSK)、BPSK或2-PSK,对所述识别信号进行调制。所述发射器尤其可以包括生成所述识别信号的BPSK调制器,并且所述接收器可以包括解码所述识别信号的BPSK解调器。BPSK调制器和BPSK解调器一般容易制作,因为它们可以在FPGA中得以实施,并且对于模拟信号转换而言一般不需要昂贵的模数转换器或数模转换器。

在另外的设计中,有可能将所述载波信号的频率选择为所述第一或第二线路的长度的函数。特别地,所述载波信号的频率与所述第一或第二线路的长度成反比。更优选地,适用下式:

其中

λ:所述载波信号的频率的波长

VK:所述第一线路的短距系数,例如0.66

c

f

L:所述第一线路的最大长度

实质上,这造成被施加高频信号的所述第一线路没有充当天线且没有辐射到所述第二线路中或到所述连接测试装置中。

根据优选的另外的进展,所述测试信号发生器可以将所述DC电压加和到所述高频信号,并由其形成所述测试信号。这实质上产生了调制DC电压。所述调制DC电压可以使用所述功率放大器来放大,并经由所述第一测试点被输出到所述第一线路。

另外的优选在于所述发射器包括所述第一开关,其可以选择性地将所述测试信号发生器与所述第一测试点解耦。特别地,所述发射器和所述接收器完全地或部分地实施在芯片中,并且它们一起形成收发器。术语测试点可以包含线端的连接接口的意思,和/或可以将其理解为与整体收发器同义。所述第一开关可以控制是否将所述收发器配置为组合发射器与接收器,或配置为接收器。所述连接测试装置包括,例如,至少两个收发器,一个被配置为发射器并且另一个被配置为接收器。优选地,有可能在所述芯片中实施10个、100个、1000个、10000个或100000个收发器,以能够并行或同时测试多个线路。

根据优选的另外的进展,所述连接测试装置可以包括用于测试所述第一线路和/或所述第二线路的第二接收器。尤其是在线缆束中,可能由于各种原因以及环境影响的作用而在所述线缆束中的两个线缆或线路之间发生临时短路。临时短路也可能出现在所述线缆束上的插入式连接器中。除了临时断开以外,根据本发明的所述连接测试装置还可以识别临时短路。为此,所述评价逻辑尤其包括第二比较器,其将所述输入信号与第二阈值进行比较,其中超过所述第二阈值可以指示在所述第一线路与所述第二线路之间存在短路。所述第一阈值优选地小于所述第二阈值。所述第一和第二阈值实质上形成阈值电压下限和上限。所述第一阈值与所述第二阈值电压之间的差,连同输入增益,可以限定所述比较器的响应灵敏度。所述相应灵敏度可以限定可测量阻抗变化范围。所述第一线路和/或所述第二线路的额定阻抗优选地位于所述第一阈值与所述第二阈值的中间。所述阈值电压为可设定的并且实质上包括目标值和容差值。所述评价逻辑可以使用所述RC元件中的已知电阻以及所述阈值电压下限和上限,来识别所述第一线路中阻抗在阻抗上限以上的上升,或是所述第一线路的所述阻抗在阻抗下限以下的下降。在所述线缆束中有临时短路的情况中,差异信号水平一般出现在所述第一线路与所述第二线路之间,这取决于极性,极性引起在所述第一接收器的所述电阻器上或在所述第二接收器的电阻器上电流上升。所述电流上升引起电压上升,所述电压上升继而导致超过所述阈值电压上限。借助于所述识别信号,所述接收器可以识别所述识别信号所源于的所述发射器。如果已知哪个发射器连接到所述线缆束中的哪个线缆,就有可能确定哪些线缆临时短路了。对所述高频信号的所述BPSK调制在检查所述第一线路与所述第二线路之间的短路方面是尤其有利的。所述BPSK调制例如避免了在所述第一和第二线路上的信号水平相等,以及还有在所述第一和第二线路上信号水平分布的相等。因此在所述第一和第二线路上的所述信号水平以及所述信号水平分布不相等时,可检测的差异信号水平能够形成。

根据本发明用于检查第一和/或第二线路中的间歇阻抗变化的方法优选地包括步骤:借助于发射器,经由所述第一或第二线路的第一线材端可以连接到的第一测试点,发送测试信号;使所述第一或第二线路经受环境影响,其使所述第一和/或第二线路的阻抗发生变化;用接收器,经由所述第一或第二线路的第二线端可以连接到的第二测试点,接收输入信号;用接收器前端将所述输入信号转换为电压信号;用所述接收器前端对所述输入信号进行滤波,以获得所述输入信号的AC分量;使用评价逻辑将所述AC分量与阈值进行比较,以识别所述第一和/或第二线路中的间歇阻抗变化。

在从属权利要求中指明并在具体实施方式中描述本发明有利的另外的进展。

附图说明

应当参考附图和下文的描述更详细地解释本发明的示例性实施例。其中:

图1示出根据本发明的示例性实施例的连接测试装置的框图,

图2示出根据本发明的示例性实施例的测试方法,

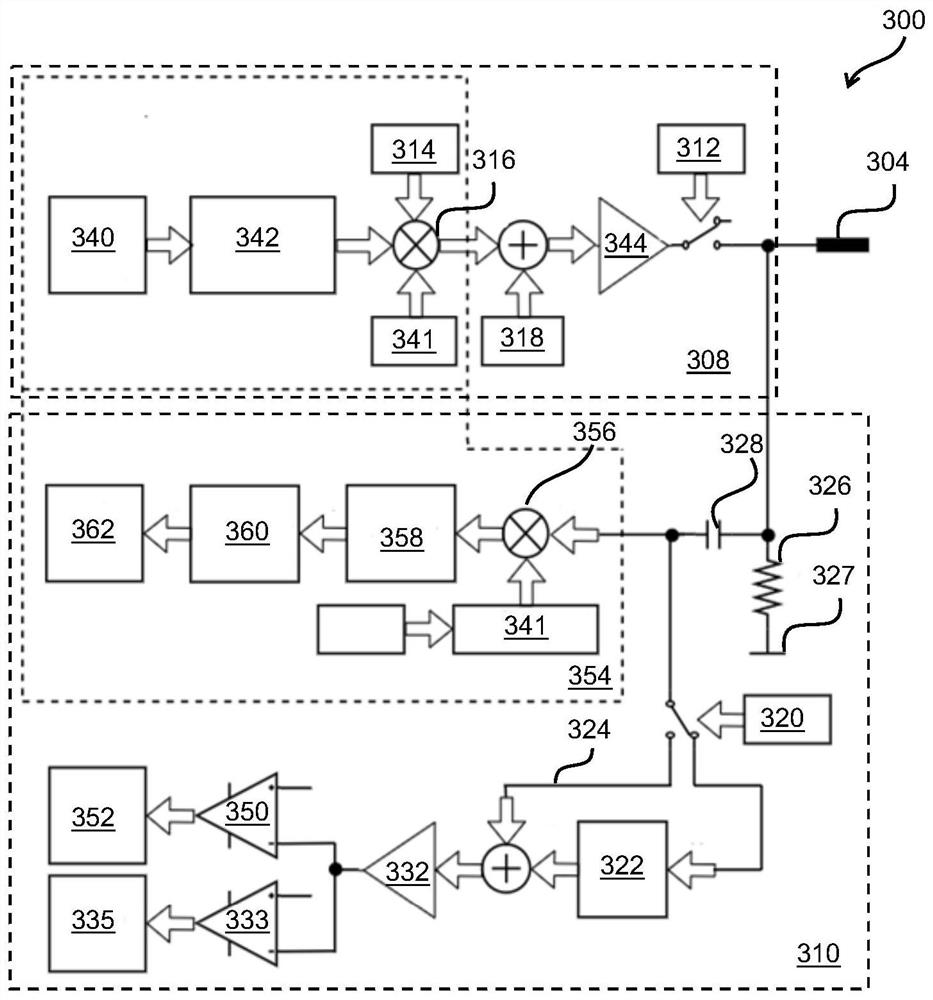

图3A示出根据本发明另外的示例性实施例的连接测试装置的框图,

图3B示出根据本发明另外的示例性实施例的连接测试装置的应用,以及

图3C示出根据本发明另外的示例性实施例的连接测试装置的应用。

具体实施方式

图1中示出根据本发明的示例性实施例的连接测试装置100。连接测试装置100包括发射器102和接收器104。发射器102包括测试信号发生器106,其生成测试信号。发射器102还包括第一测试点108,用于连接第一线路110的第一线端。测试信号发生器106经由第一测试点108将所述测试信号提供给第一线路110。发射器102连同另外的接收器可以形成收发器或测试点。接收器104包括第二测试点112,用于连接第一线路110的第二线端。接收器104还包括接收器前端114,其经由第二测试点112接收来自第一线路的呼入信号;以及评价逻辑116,其连接到接收器前端114。接收器104连同另外的发射器可以形成另外的收发器或另外的测试点。

图2中示出用于检查第一和/或第二线路中的间歇阻抗变化的测试方法200。在第一个步骤202中,发射器发送测试信号到第一或第二线路的第一线端中。在第二个步骤204中,第一线材和/或第二线材暴露于环境影响,例如,低温(77.4K以下)、热、光、湿气、水、凝露、腐蚀、机械应力(振动、冲击、震击、加速)、海洋性气候、沙和/或尘。所述环境影响导致所述第一线路和/或所述第二线路的阻抗的动态变化。在第三个步骤206中,接收器接收来自所述第一或第二线路的第二线端的输入电流信号,其基于被阻抗变化改变的DC电压信号。在第四个步骤208中,接收器前端将所述输入电流信号转换成输入电压。在第五个步骤210中,所述接收器前端对来自所述输入电压的AC部分进行滤波。在第六个步骤212中,评价逻辑将所述AC部分与可设定的第一阈值电压进行比较,可设定的第一阈值电压由最大电压和容差值构成,其中不足所述第一阈值电压指示间歇阻抗上升,即,所述第一线路的动态断开。利用方法200,连接测试装置100能够容易地且快速地检查个体线路中以及具有许多线路的线缆束中呈间歇阻抗变化形式的动态线路故障,而无需使用昂贵的精密测量装置。

图3A中示出根据本发明另外的示例性实施例的连接测试装置300。连接测试装置300检查在测试期间待测试的第一个体线材302中是否发生阻抗上升,参见图3B。待测试的第一个体线材302为线缆束的部分,并且连接到连接测试装置300的至少两个测试点304、306。第一测试点304被配置为发射器308并且向第一测试点304发送测试信号。第二测试点306,参见图3B,被配置为接收器310,在其中借助于收发器开关312关闭其自身的发射信号,并且接收器310接收来自待测试的第一个体线材302的呼入信号。借助于高频开关,以使得发射器308输出由直流电压源318生成的DC电压信号的方式,控制发射器308中的混频器316。功率驱动器344放大所述DC电压信号,并经由收发器开关312将所述DC电压信号提供给第一测试点304。接收器310包括旁路开关320、具有基带滤波器322和旁通线路324的并联电路,其中旁路开关320以旁通基带滤波器322的方式来设置。相应地,接收器310以最大带宽接收来自待测试的第一个体线材302的输入电压信号。离开第一个体线材302的电流经由测量电阻或端接阻抗326,流至供给电压电势327或接地,并将所述电流转换成输入电压信号,经由与所述测量电阻并联的电容器328将所述输入电压信号与DC电压分量分离。通过电容器328的信号代表所述输入电压信号的AC部分。第一个体线材302的线路阻抗330的上升导致所述电流减小,以及因此导致所述输入电压信号的减小。用输入放大器322放大该输入电压信号或其AC分量,并将该输入电压信号或其AC分量提供给截止比较器333,截止比较器333将经放大的AC分量与可设定的截止电压水平进行比较。如果经放大的AC分量落到所述截止电压水平以下,则向分析单元335输出二进制结果信号,其中1代表个体线路302中的断开并且0代表个体线路320中无断开。在FPGA(现场可编辑门阵列)中对该二进制信号的改变进行计数,作为动态开路故障。根据另外的示例性实施例,连接测试装置300也可以区分并计数静态线路故障,其中线路故障仍存在,但由于所述二进制信号的前一改变导致具体的可编程时间已过去。

根据本发明另外的示例性实施例,连接测试装置300可以检测在第一与第二个体线材334之间的动态短路。待测试的第一个体线材302连接到第一和第二测试点304、306,或连接到收发器,如上文所述。术语测试点因此可以包含线端的连接接口的意思,和/或可以被理解为与整体收发器同义。为了能够检查短路,至少第二个体线材334必须连接到第二接收器338的或是包含接收器338的另外的收发器的第三测试点336。第三测试点336因此或被配置为纯接收器338或被配置为收发器。每个发射器具有唯一地址,后者为所述发射器中生成的基带信号340的一部分。FPGA生成该基带信号340并将提供给NRZ(不归零)编码器342。相应地,NRZ编码器342将基带信号340的一或零编码成针对逻辑1的+1和针对逻辑0的-1。在混频器316中将由NRZ编码器342生成的NRZ信号乘以振荡器341的载波信号。以此方式产生的信号为BPSK调制(BPSK=二进制相移键控)。BPSK调制信号,也被称为帧,对于检测两个个体线材的不容许的电气连接(即短路)而言是需要的。如果仅检测到阻抗上升,则可以经由高频开关314禁用BPSK信号,从而发射器308生成DC电压信号。如果激活高频开关314,则发射器308以顺序的方式持续输出BPSK调制信号作为连续数据流。

载波信号的频率f

其中

λ:载波信号的频率的波长

c

f

L:个体线路的最大长度

借助于载波频率与线路长度的比率,确保在连接到测试点304、306的线路302、334的帧内的线路信号水平相异。

在第一测试点304处,逻辑1被定义为:s

在第一测试点304处,逻辑0被定义为:s

其中:

A:载波信号的最大幅度

f

s

DC电压偏置产生调制DC电压,经由功率驱动器344和激活的收发器开关312将调制DC电压提供给第一测试点304。

如果第一测试点304不需要作为发射器而是作为接收器,例如用于在持续短路期间检修是否两个发射器馈送至一电路,收发器开关312关闭调制DC电压信号或发射信号。

如果在第一与第二个体线材302、334之间存在导电连接346或短路,则作为电平差的结果而在个体线路302、334之间发生电流流动。这导致在端接阻抗326或端接阻抗348上(取决于较低的信号水平位于哪个上)的短暂的电平升高,该短暂的电平升高反映在输入信号中。禁用在基带滤波器322上游的旁路开关320,即,将输入信号路由到滤波器,并且来自基带的谱分量被衰减,从而它们不再,或是仅暂时地,被截止比较器333或被短路比较器350评价。可以在BPSK信号的接收器的数字滤波器中去除由收发器自身生成的BPSK信号,其中时间和预期地址对滤波器是已知的。暂时地意味着剩余有源比较器时间满足检测来自第二线材的外来谱分量的需要。经滤波的输入信号被提供给截止比较器,用于与可设定的截止电压水平进行比较,并被提供给短路比较器350用于与可设定的截止电压水平进行比较。如果超过截止电压水平,则输出二进制结果信号给分析单元352,其中1代表在第一与第二个体线路302、334之间没有短路,并且0代表在第一与第二个体线路302、224之间的短路。对该二进制结果信号进行计数,作为FPGA中的动态短路故障。第一和第二接收器310、338每个都具有BPSK解调器354。BPSK解调器354包括下变频器356,其接收输入信号和所述载波信号,并通过所述载波信号的频率减小所述输入信号到下变频器输出信号;积分器358,其连接到下变频器356,接收所述下变频器输出信号,在位周期上对其进行积分作为积分器输出信号;阈值鉴频器360,其连接到积分器358,接收所述积分器输出信号,将其与位中心的区分阈值进行比较并输出数字信号;以及基带分析单元362,其连接到阈值鉴频器360,接收所述数字信号,并评价所述数字信号中是否包含地址,以及如果是的话包含哪个地址。BPSK解调器354可以使用所述地址将所述呼入信号唯一地分配给所述发射器的发射信号,或者在多个发射器的情况中,唯一地分配给所述多个发射器中特定一个的发射信号。

附图标记列表:

100 连接测试装置

102 发射器

104 接收器

106 测试信号发生器

108 第一测试点

110 第一线路

112 第二测试点

114 接收器前端

116 评价逻辑

200 测试方法

202、204、206、208、210、212 步骤

300 连接测试装置

302 第一个体线材

304 第一测试点

306 第二测试点

308 发射器

310 接收器

312 收发器开关

314 高频开关

316 混频器

318 直流电压源

320 旁路开关

322 基带滤波器

324 旁通线路

326 测量电阻

327 供给电压电势

328 电容器

330 线路阻抗

332 输入放大器

333 截止比较器

334 第二个体线材

335 分析单元

336 第三测试点

338 第二接收器

340 基带信号

341 振荡器

342 NRZ编码器

344 功率驱动器

346 导电连接

348 端接阻抗

350 短路比较器

352 分析单元

354 BPSK解调器

356 下变频器

358 积分器

360 阈值鉴频器

362 基带分析单元

- 用于检查间歇阻抗变化的连接测试装置及方法

- 应用于发电机转子交流阻抗测试的连接组件及测试装置