异质集成工作量证明运算芯片的数据动态重构电路及方法

文献发布时间:2023-06-19 09:32:16

技术领域

本发明涉及集成电路技术领域,特别是指一种异质集成工作量证明运算芯片的数据动态重构电路及方法。

背景技术

工作量证明(Proof of Work,简称POW)是以太币等主流加密数字币采用的一种共识机制,其基本特征是需要进行大量的哈希运算,在特定难度值条件下找到符合条件的哈希值。但是,以ETHASH算法为核心的加密数字币在工作量证明过程中需要一个大于1GB的数据集,并需要对该数据集进行频繁访问。

传统方法是在计算芯片外使用独立的外存来存储该数据集,但是该方法的性能较低。因此,对传统方法进行改进,出现了一种异质集成工作量证明运算芯片的技术。该技术是在一片硅片中实现工作量证明算法逻辑,在另一片硅片中设置大容量的存储单元来存储整个数据集,然后利用异质集成工艺将两块硅片键合在一起,以实现大容量的片内存储和高带宽。在该技术中,存储单元由多个独立的子存储单元构成,各个子存储单元之间是相互独立的,在半导体制造或键合过程中,会由于制造缺陷或键合缺陷导致某些子存储单元试下,任意子存储单元失效都会使整个芯片的数据集不完整,从而导致整个芯片失效,降低了芯片的鲁棒性和良率。

发明内容

有鉴于此,本发明的主要目的在于提供一种异质集成工作量证明运算芯片的数据动态重构电路及方法,以能提高工作量证明运算芯片的鲁棒性和良率。

本发明提供的一种异质集成工作量证明运算芯片的数据动态重构电路,包括:依次连接的计算层、地址动态重构层、交叉开关和存储层;其中,所述计算层由多个计算单元构成,所述存储层由多个存储单元构成;

所述计算层用于基于计算任务调用所述存储层所存储的数据,并进行相应计算;

所述地址动态重构层用于当所述工作量证明运算芯片的一个或多个存储单元失效时,根据所述芯片有效的存储单元数量和所述芯片所存储的数据总量进行数据地址重构;

所述交叉开关用于使各个计算单元和各个存储单元互连;

所述存储层用于存储所述工作量证明运算芯片的数据。

由上,通过在工作量证明运算芯片添加地址动态重构层,当存储单元失效时,地址动态重构层将数据重新分配,可以使工作量证明运算芯片正常工作,提高了鲁棒性和良率。

作为第一方面的一种实现方式,所述根据所述芯片有效的存储单元数量和所述芯片所存储的数据总量进行数据地址重构,包括:

按下式将数据x存放在第N个有效的存储单元中:

N=x%(N

按下式确定数据x在第N个有效的存储单元中的位置L:

其中,x为工作量证明运算芯片第x个数据,%为取余运算,N

由上,提供一种向有效的存储单元中分配数据的方式,利用上述公式可以保证有序且完整的存储芯片原有的全部数据。

一种异质集成工作量证明运算芯片的数据动态重构方法,包括:

当工作量证明运算芯片的一个或多个存储单元失效时,根据所述芯片有效的存储单元数量和所述芯片所存储的数据总量进行数据地址重构;

待完成数据地址重构时,关闭失效的存储单元并修改路由表。

由上,利用该方法可以提高工作量证明运算芯片的鲁棒性和良率。

作为第二方面的一种实现方式,所述根据所述芯片有效的存储单元数量和所述芯片所存储的数据总量进行数据地址重构,包括:

按下式将数据x存放在第N个有效的存储单元中:

N=x%(N

按下式确定数据x在第N个有效的存储单元中的位置L:

其中,x为工作量证明运算芯片第x个数据,%为取余运算,N

作为第二方面的一种实现方式,所述修改路由表,包括:

根据数据地址重构后工作量证明运算芯片数据的存储位置建立计算单元至存储单元的访问路径,使其绕过失效的存储单元。

由上,通过重新修改路由表,保证计算单元调用存储数据的有效性。

一种异质集成工作量证明运算芯片的数据动态重构系统,包括:

数据重构模块,用于当工作量证明运算芯片的一个或多个存储单元失效时,根据所述芯片有效的存储单元数量和所述芯片所存储的数据总量进行数据地址重构;

访问路径重构模块,用于待完成数据地址重构时,关闭失效的存储单元并修改路由表。

综上,本发明可以解决下述问题:在满足工作量证明运算性能的前提下,提高工作量证明运算芯片的鲁棒性及良率。

附图说明

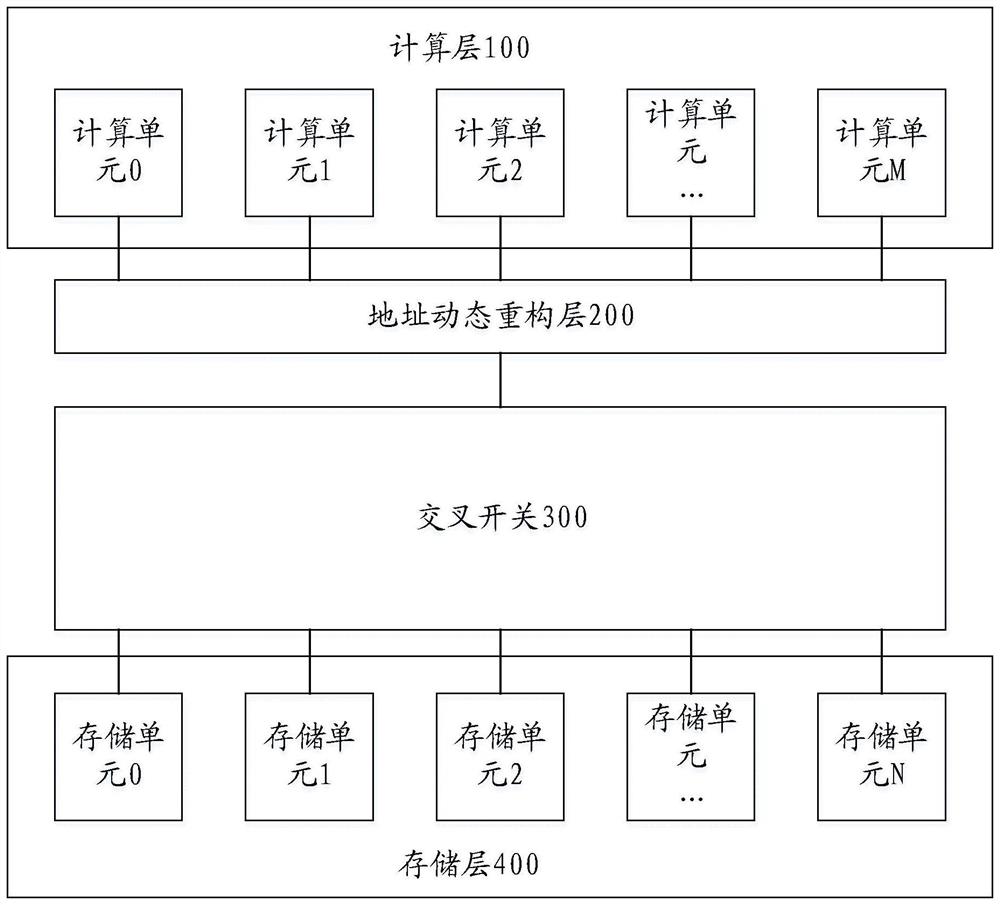

图1为本申请实施例提供的一种异质集成工作量证明运算芯片的数据动态重构电路的结构示意图;

图2为本申请实施例提供的一种异质集成工作量证明运算芯片的数据动态重构方法的流程图;

图3为现有技术中异质集成工作量证明运算芯片的结构示意图;

图4为本申请实施例提供的一种异质集成工作量证明运算芯片的数据动态重构系统的结构示意图。

附图标记:

100-计算层、200-地址动态重构层、300-交叉开关、400-存储层

具体实施方式

为了便于理解本申请,下面将参照相关附图对本申请进行更全面的描述。附图中给出了本申请的首选实施例。但是,本申请可以以许多不同的形式来实现,并不局限于本文所描述的实施例。相反地,提供这些实施例的目的是使本申请的公开内容更加透彻全面。

在以下的描述中,所涉及的术语“第一\第二\第三等”或模块A、模块B、模块C等,仅用于区别类似的对象,不代表针对对象的特定排序,可以理解地,在允许的情况下可以互换特定的顺序或先后次序,以使这里描述的本申请实施例能够以除了在这里图示或描述的以外的顺序实施。

在以下的描述中,所涉及的表示步骤的标号,如S100、S200……等,并不表示一定会按此步骤执行,在允许的情况下可以互换前后步骤的顺序,或同时执行。

除非另有定义,本文所使用的所有的技术和科学术语与属于本申请的技术领域的技术人员通常理解的含义相同。本文中在本申请的说明书中使用的属于只是为了描述具体的实施例的目的,不是旨在限制本申请。本文所使用的术语“和/或”包括一个或多个相关的所列项目的任意的和所有的组合。

如图1所示,本申请的其中一个实施例提供了一种异质集成工作量证明运算芯片的数据动态重构电路,该电路包括:

依次连接的计算层100、地址动态重构层200、交叉开关300和存储层400。其中,该计算层100由多个计算单元构成,该存储层400由多个存储单元构成。需要注意的是,计算单元和存储单元的个数本实施例不做限制,两者的数量可以相同,也可以不同。

计算层100用于基于计算任务所需的数据,调用相应存储层存储的数据,并进行计算。其中,计算任务可以为用户下发的计算任务。

地址动态重构层200用于当工作量证明运算芯片的一个或多个存储单元失效时,根据芯片有效的存储单元数量和芯片所存储的数据总量进行数据地址重构,具体的:

按下式确定存放在第N个有效的存储单元中的数据:

N=x%(N

按下式确定存放在第N个有效的存储单元中第L行的数据:

其中,x为工作量证明运算芯片第x个数据,%为取余运算,N

上述数据地址重构规则为数据的存储规则,同时也是数据的读取规则。

如图2所示,本申请的另一实施例提供一种异质集成工作量证明运算芯片的数据动态重构方法,该方法包括:

S100:当工作量证明运算芯片的一个或多个存储单元失效时,根据所述芯片有效的存储单元数量和所述芯片所存储的数据总量进行数据地址重构。

S200:待完成数据地址重构时,关闭失效的存储单元并修改路由表。

具体的,步骤S100包括:

按下式确定存放在第N个有效的存储单元中的数据:

N=x%(N

按下式确定存放在第N个有效的存储单元中第L行的数据:

其中,x为工作量证明运算芯片第x个数据,%为取余运算,N

步骤S200中修改路由表包括:根据数据地址重构后工作量证明运算芯片数据的存储位置建立计算单元至存储单元的访问路径,使其绕过失效的存储单元。其中,路由表中记录有各计算单元访问各存储单元的路径。

在本实施例中,当异质集成工作量证明运算芯片中存储单元均有效时,从数据存储原地址中读取数据。当异质集成工作量证明运算芯片中有一个或多个存储单元失效时,利用本申请提供的异质集成工作量证明运算芯片的数据动态重构方法确定出数据存储于存储单元的地址,并按照该地址将数据写入。在读取数据时,同样通过本申请提供的异质集成工作量证明运算芯片的数据动态重构方法确定出数据存储于存储单元的地址,按照该地址来读取所需数据。

通过本申请提供的异质集成工作量证明运算芯片的数据动态重构方法,可以使异质集成工作量证明运算芯片在一个或多个存储单元失效时,芯片的整体功能不受影响。

下面,结合图1和图3,说明一种异质集成工作量证明运算芯片的数据动态重构方法的具体实现方式。

如图3所示,为现有技术下异质集成工作量证明运算芯片的电路结构图,该电路结构包括多个计算单元、交叉开关和多个存储单元。本实施例中计算单元的数量为M,存储单元的数量为N,M和N可以为任意的正整数。

该芯片如果可以正常运行,需要满足:

计算单元0能够从存储单元0-N任意单元中获取到正确的数据集;

计算单元1能够从存储单元0-N任意单元中获取到正确的数据集;

计算单元2能够从存储单元0-N任意单元中获取到正确的数据集;

……

计算单元M能够从存储单元0-N任意单元中获取到正确的数据集。

当存储单元0-N中任意单元失效时,导致整个芯片失效。

如图1所示,为本实施例提供的异质集成工作量证明运算芯片的电路结构图,在计算单元和交叉开关之间添加了地址动态重构层。

当该芯片中存储单元均有效时:

计算单元0从存储单元0-N任意单元中获取到正确的数据集进行相关计算;

计算单元1从存储单元0-N任意单元中获取到正确的数据集进行相关计算;

计算单元2从存储单元0-N任意单元中获取到正确的数据集进行相关计算;

……

计算单元M从存储单元0-N任意单元中获取到正确的数据集进行相关计算。

例如:当该芯片中存储单元0失效时:

地址动态重构层将数据集均匀的存储到除存储单元0之外的其他存储单元(1-N),同时计算单元0-M对存储单元0的访问分配到其他存储单元。具体的:

地址动态重构层将数据集的第0个数据存储在存储单元1的地址0处,将数据集的第一个数据存储在存储单元2的地址0处,依次类推,将数据集的第N-1个数据存储在存储单元N的地址0处,将数据集的第N个数据存储在存储单元1的地址1处,将数据集的第N+1个数据存储在存储单元2的地址1处。据此,可以推出对数据集的第x个数据,应存储在第x%(N-1)个有效的子存储单元的第

再例如:当该芯片中存储单元0和存储单元2失效时:

地址动态重构层将数据集均匀的存储到除存储单元0和除存储单元2之外的其他存储单元(1-N),同时计算单元0-M对存储单元0和存储单元2的访问分配到其他存储单元。具体的:

地址动态重构层将数据集的第x个数据没存储在第x%(N-2)个有效的子存储单元的第

再例如:当该芯片中n个存储单元失效时:(其中,n小于芯片中存储单元的总数量)

地址动态重构层将数据集均匀的存储到有效的存储单元中,同时计算单元0-M对失效的n个存储单元的访问分配到其他存储单元。具体的:

按下式确定存放在第N个有效的存储单元中的数据:

N=x%(N

按下式确定存放在第N个有效的存储单元中第L行的数据:

其中,x为工作量证明运算芯片第x个数据,%为取余运算,N

直至存储完整个数据集。在需要读取数据集时使用相同的方法来获得数据集的第x个数据的地址。

如图4所示。本申请的另一实施例提供一种异质集成工作量证明运算芯片的数据动态重构系统,该系统包括:

数据重构模块,用于当工作量证明运算芯片的一个或多个存储单元失效时,根据所述芯片有效的存储单元数量和所述芯片所存储的数据总量进行数据地址重构;

访问路径重构模块,用于待完成数据地址重构时,关闭失效的存储单元并修改路由表。

注意,上述仅为本申请的较佳实施例及所运用技术原理。本领域技术人员会理解,本申请不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整和替代而不会脱离本申请的保护范围。因此,虽然通过以上实施例对本申请进行了较为详细的说明,但是本申请不仅仅限于以上实施例,在不脱离本申请构思的情况下,还可以包括更多其他等效实施例,均属于本申请保护范畴。

- 异质集成工作量证明运算芯片的数据动态重构电路及方法

- 缓存结构、工作量证明运算芯片电路及其数据调用方法