以机器学习针对服务质量优化进行存取控制的方法和设备

文献发布时间:2023-06-19 09:57:26

技术领域

本发明是关于闪存的存取,特别是关于一种借助于机器学习来针对一记忆装置的服务质量(quality of service,QoS)优化(optimization)进行存取控制的方法、相关设备(例如:所述记忆装置及其控制器诸如所述记忆装置中的一存储器控制器)。

背景技术

近年来由于存储器的技术不断地发展,各种可携式或非可携式记忆装置(例如:分别符合SD/MMC、CF、MS、XD及UFS标准的记忆卡;又例如:固态硬盘(solid state drive,SSD);又例如:分别符合UFS及EMMC规格的嵌入式(embedded)记忆装置)被广泛地实施于诸多应用中。因此,这些记忆装置中的存储器的存取控制遂成为相当热门的议题。

以常用的NAND型闪存而言,其主要可包括单阶细胞(single level cell,SLC)与多阶细胞(multiple level cell,MLC)两大类的闪存。单阶细胞闪存中的每一个被当作记忆细胞(memory cell)的晶体管只有两种电荷值,分别用来表示逻辑值0与逻辑值1。另外,多阶细胞闪存中的每一个被当作记忆细胞的晶体管的存储能力则被充分利用,是采用较高的电压来驱动,以通过不同级别的电压在一个晶体管中记录至少两个位(bit;也可称为“比特”)的信息(诸如00、01、11、10)。理论上,多阶细胞闪存的记录密度可以达到单阶细胞闪存的记录密度的至少两倍,这对于曾经在发展过程中遇到瓶颈的NAND型闪存的相关产业而言,是非常好的消息。

相较于单阶细胞闪存,由于多阶细胞闪存的价格较便宜,并且在有限的空间里可提供较大的容量,故多阶细胞闪存很快地成为市面上的记忆装置竞相采用的主流。然而,多阶细胞闪存的不稳定性所导致的问题也一一浮现。为了确保在记忆装置中对闪存的存取控制能符合相关规范,闪存的控制器通常备有某些管理机制以妥善地管理数据的存取。

依据相关技术,具备上列管理机制的记忆装置仍有不足的地方。例如,当三阶细胞(triple level cell,TLC)闪存及四阶细胞(quadruple level cell,QLC)闪存被应用于记忆装置时,会有某些问题诸如增加的位错误率(bit error rate,BER)等。另外,采用三维(three dimensional,3D)NAND快闪架构来实现的闪存的方案已被提出以达到更高的存储容量,却衍生出某些额外的问题诸如随机写入延迟以及随机读取延迟。由于大多数用户行为可对应于随机读取,所以在大多数情况下,随机读取延迟问题可导致较低的服务质量(QoS)。此外,在3D NAND快闪架构的堆栈(stack)中的记忆细胞增加的情况下,基于某些目的诸如易于实现,一浮栅(floating gate,FG)解决方案可被取代为采用电荷捕获(charge-trap,CT)材料的新解决方案,这可能对应地造成有数据保留(data-retention)问题,使得读取数据的延迟时间增加,所以服务质量可能变得更低。尤其,所述数据保留问题可能触发上述管理机制中的一移动读取机制(moving read mechanism)进行一或多个额外读取操作,这造成整体性能下降。因此,需要一种新颖的方法以及相关架构,以在没有副作用或较不会带来副作用的情况下加强整体效能。

发明内容

本发明的一目的在于提供一种借助于机器学习来针对一记忆装置的服务质量优化进行存取控制的方法以及相关设备(例如:所述记忆装置及其控制器诸如所述记忆装置中的一存储器控制器),以解决上述问题。

本发明的另一目的在于提供一种借助于机器学习来针对一记忆装置的服务质量优化进行存取控制的方法以及相关设备(例如:所述记忆装置及其控制器诸如所述记忆装置中的一存储器控制器),以在没有副作用或较不会带来副作用的情况下加强整体效能。

本发明的至少一实施例提供一种借助于机器学习来针对一记忆装置的服务质量优化进行存取控制的方法。所述记忆装可包括一非挥发性存储器(non-volatile memory,NV memory)以及用来控制所述非挥发性存储器的存取的一存储器控制器,以及所述非挥发性存储器可包括至少一非挥发性存储器组件(例如一或多个非挥发性存储器组件)。所述方法可包括:对所述非挥发性存储器进行背景扫描以收集所述非挥发性存储器中的记忆细胞的电压分布的谷信息(valley information),以及依据所述谷信息进行基于一强化学习模型(reinforcement learning model)的机器学习,以通过基于所述强化学习模型的所述机器学习来预先准备多个表,以供用来从所述非挥发性存储器读取数据,其中所述多个表中的每一表包括一组读取电压,以及所述组读取电压是从基于所述强化学习模型的所述机器学习取得;于一第一时间区间内,写入第一数据以及使用所述多个表中的一第一表来读取所述第一数据,其中所述第一表是被选取作为所述第一时间区间内用于所述第一数据的一适当表;以及于一第二时间区间内,使用所述多个表中的一第二表来读取所述第一数据,其中所述第二表是被选取作为所述第二时间区间内用于所述第一数据的所述适当表,以及所述第二时间区间是在一时间轴上的所述第一时间区间的下一个时间区间。

除了以上方法外,本发明亦提供一种记忆装置,且所述记忆装置可包括一非挥发性存储器以及一控制器。所述非挥发性存储器是用来存储信息,其中所述非挥发性存储器可包括至少一非挥发性存储器组件(例如一或多个非挥发性存储器组件)。所述控制器是耦接至所述非挥发性存储器,且所述控制器是用来控制所述记忆装置的运作。另外,所述控制器包括一处理电路,其是用来依据来自一主装置的多个主装置指令来控制所述控制器,以容许所述主装置通过所述控制器存取所述非挥发性存储器。例如:所述控制器对所述非挥发性存储器进行背景扫描以收集所述非挥发性存储器中的记忆细胞的电压分布的谷信息,并且依据所述谷信息进行基于一强化学习模型的机器学习,以通过基于所述强化学习模型的所述机器学习来预先准备多个表,以供用来从所述非挥发性存储器读取数据,其中所述多个表中的每一表包括一组读取电压,以及所述组读取电压是从基于所述强化学习模型的所述机器学习取得;于一第一时间区间内,所述控制器写入第一数据以及使用所述多个表中的一第一表来读取所述第一数据,其中所述第一表是被选取作为所述第一时间区间内用于所述第一数据的一适当表;以及于一第二时间区间内,所述控制器使用所述多个表中的一第二表来读取所述第一数据,其中所述第二表是被选取作为所述第二时间区间内用于所述第一数据的所述适当表,以及所述第二时间区间是在一时间轴上的所述第一时间区间的下一个时间区间。

除了以上方法外,本发明亦提供一种记忆装置的控制器,其中所述记忆装置包括所述控制器以及一非挥发性存储器。所述非挥发性存储器可包括至少一非挥发性存储器组件(例如一或多个非挥发性存储器组件)。另外,所述控制器包括一处理电路,其是用来依据来自一主装置的多个主装置指令来控制所述控制器,以容许所述主装置通过所述控制器存取所述非挥发性存储器。例如:所述控制器对所述非挥发性存储器进行背景扫描以收集所述非挥发性存储器中的记忆细胞的电压分布的谷信息,并且依据所述谷信息进行基于一强化学习模型的机器学习,以通过基于所述强化学习模型的所述机器学习来预先准备多个表,以供用来从所述非挥发性存储器读取数据,其中所述多个表中的每一表包括一组读取电压,以及所述组读取电压是从基于所述强化学习模型的所述机器学习取得;于一第一时间区间内,所述控制器写入第一数据以及使用所述多个表中的一第一表来读取所述第一数据,其中所述第一表是被选取作为所述第一时间区间内用于所述第一数据的一适当表;以及于一第二时间区间内,所述控制器使用所述多个表中的一第二表来读取所述第一数据,其中所述第二表是被选取作为所述第二时间区间内用于所述第一数据的所述适当表,以及所述第二时间区间是在一时间轴上的所述第一时间区间的下一个时间区间。

本发明的方法及相关设备能确保整个系统(例如所述主装置以及所述记忆装置)妥善地运作,以避免相关技术中的问题,诸如位错误率(bit error rate)提高、随机读取延迟增加、以及所述数据保留问题所衍生出的某些相关问题。另外,依据本发明的实施例来实施不会大幅增加额外成本。因此,相关技术的问题能被解决,而整体成本不会增加太多。相较于相关技术,本发明的方法及相关设备能在没有副作用或较不会带来副作用的情况下提升整体效能。

附图说明

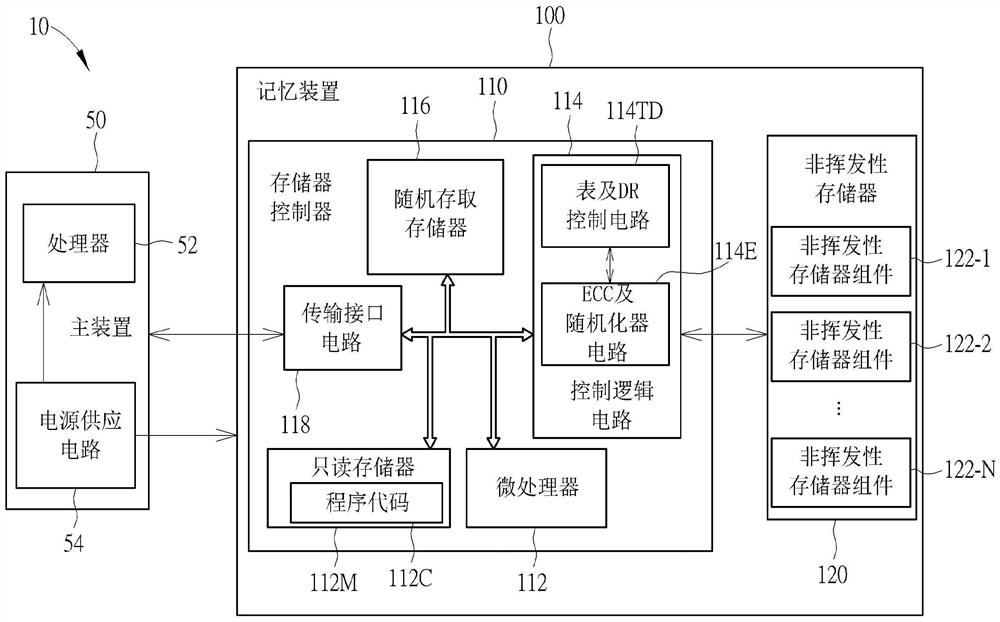

图1为依据本发明一实施例的一电子装置的示意图。

图2为依据本发明一实施例的一三维(three-dimensional,3D)NAND型闪存的示意图。

图3依据本发明一实施例绘示图2所示的三维NAND型闪存的某些局部结构。

图4依据本发明一实施例绘示图2所示的三维NAND型闪存的多个记忆细胞中的一个记忆细胞的某些实施细节。

图5依据本发明一实施例绘示一阈电压(threshold voltage,可简称Vth)追踪控制方案。

图6绘示图5所示的阈电压追踪控制方案的某些实施细节。

图7依据本发明一实施例绘示如图5所示的阈电压追踪控制方案的某些复原层级(recovery stage)以及这些复原层级之间的关系。

图8依据本发明一实施例绘示图5所示的阈电压追踪控制方案的一测试流程。

图9依据本发明一实施例绘示通过图8所示的测试流程而取得的某些测试结果。

图10依据本发明一实施例绘示针对某一耐久交替循环(endurance cycle)诸如150个编程/抹除(program and erase,P/E)交替循环(cycle)的TLC阈电压分布图。

图11依据图10所示实施例绘示针对一较高耐久交替循环诸如5000个编程/抹除交替循环的TLC阈电压分布图。

图12依据本发明一实施例绘示使用一背景扫描控制方案来处理的某些实体区块。

图13依据本发明一实施例绘示针对一噪声容限(noise margin)记录控制方案的一TLC阈电压分布图。

图14绘示对应于图13所示的TLC阈电压分布图的谷位置及高度图。

图15绘示图13所示的TLC阈电压分布图中的一部分的波谷的某些硬解码(hard-decoding,HD)通过范围(pass range)。

图16依据本发明一实施例绘示通过一强化学习(reinforcement learning)控制方案从图10所示的TLC阈电压分布图的谷信息取得的某些最佳读取点。

图17依据图16所示实施例绘示通过所述强化学习控制方案从图11所示的TLC阈电压分布图中的谷信息取得的某些最佳读取点。

图18依据本发明一实施例绘示指出数据保留改善的三组曲线。

图19依据本发明一实施例绘示一种借助于机器学习来针对记忆装置的服务质量优化进行存取控制的方法。

图20是依据本发明一实施例的如图19所示方法的工作流程。

其中,附图标记说明如下:

10 电子装置

50 主装置

52 处理器

54 电源供应电路

100 记忆装置

110 存储器控制器

112 微处理器

112C 程序代码

112M 只读存储器

114 控制逻辑电路

114E ECC及随机化器电路

114TD 表及数据刷新控制电路

116 随机存取存储器

118 传输接口电路

120 非挥发性存储器

122-1、122-2~122-N 非挥发性存储器组件

M(1,1,1)~M(Nx,Ny,Nz) 记忆细胞

MBLS(1,1)~MBLS(Nx,Ny) 上方选择电路

MSLS(1,1)~MSLS(Nx,Ny) 下方选择电路

BL(1)~BL(Nx) 位线

WL(1,1)~WL(Ny,Nz) 字线

BLS(1)~BLS(Ny) 上方选择线

SLS(1)~SLS(Ny) 下方选择线

SL(1)~SL(Ny) 源极线

PS2D(1)~PS2D(Ny) 电路模块

S(1,1)~S(Nx,Ny) 次要电路模块

M(nx,ny,nz) 记忆细胞

Mch 棒段

Md 上侧

Ms 下侧

Mfg 第一管状局部结构

Mcg 第二管状局部结构

Phase(0)~Phase(2) 阶段

S10~S23 步骤

具体实施方式

I.存储器系统

图1为依据本发明一实施例的电子装置10的示意图,其中电子装置10可包括一主装置50以及一记忆装置100。主装置50可包括至少一处理器(例如一或多个处理器),可统称为处理器52,且可还包括耦接至处理器52的一电源供应电路54。处理器52可用来控制主装置50的运作,而电源供应电路54可用来提供电源给处理器52以及记忆装置100,并且输出一或多个驱动电压给记忆装置100。记忆装置100可用来提供存储空间给主装置50,并且自主装置50取得所述一或多个驱动电压以作为记忆装置100的电源。主机50的例子可包括(但不限于):多功能移动电话(multifunctional mobile phone)、平板计算机(tablet)以及个人计算机(personal computer)诸如桌面计算机与膝上型计算机。记忆装置100的例子可包括(但不限于):固态硬盘(solid state drive,SSD)以及各种类型的嵌入式(embedded)记忆装置诸如符合快捷外设互联(Peripheral Component Interconnect Express,PCIe)标准的嵌入式记忆装置等。依据本实施例,记忆装置100可包括一控制器诸如存储器控制器110,且可还包括一非挥发性存储器(non-volatile memory,NV memory)120,其中所述控制器诸如存储器控制器110是用来控制记忆装置100的运作以及存取非挥发性存储器120,而非挥发性存储器120是用来存储信息。非挥发性存储器120可包括至少一非挥发性存储器组件(例如一或多个非挥发性存储器组件),诸如复数个非挥发性存储器组件122-1、122-2、…及122-N,其中“N”可表示大于一的正整数。例如,非挥发性存储器120可为一闪存,而非挥发性存储器组件122-1、122-2、…及122-N可为多个闪存芯片或多个闪存裸晶,但本发明不限于此。

如图1所示,存储器控制器110可包括一处理电路诸如一微处理器112、一存储单元诸如一只读存储器(Read Only Memory,ROM)112M、一控制逻辑电路114、一随机存取存储器(Random Access Memory,RAM)116以及一传输接口电路118,其中这些组件可通过一总线彼此耦接。随机存取存储器116是以一静态随机存取存储器(Static RAM,SRAM)来实施,但本发明不限于此。随机存取存储器116可用来提供内部存储空间给存储器控制器110,例如,随机存取存储器116可用来作为一缓冲存储器以缓冲数据。另外,本实施例的只读存储器112M是用来存储一程序代码(program code)112C,而微处理器112则用来执行程序代码112C以控制对非挥发性存储器120的存取。请注意,在某些例子中,程序代码112C可存储在随机存取存储器116或任何形式的存储器内。此外,控制逻辑电路114可用来控制非挥发性存储器120,且可包括用来保护数据及/或进行错误更正的一数据保护电路,其中所述数据保护电路可包括多个子电路诸如一错误更正码(Error Correction Code,简称ECC)及随机化器(randomizer)电路114E以及一表及数据刷新(data-refresh,DR)控制电路114TD(在图1中分别标示为“ECC及随机化器电路”以及“表及DR控制电路”以求简明),但本发明不限于此。传输接口电路118可符合一特定通讯标准(诸如串行高级技术附件(Serial AdvancedTechnology Attachment,SATA)标准、外设组件互联(Peripheral ComponentInterconnect,PCI)标准、快捷外设互联标准、通用快闪存储(Universal Flash Storage,UFS)标准等),且可依据所述特定通讯标准进行通讯,例如为记忆装置100,和主装置50进行通讯,其中主装置50可包括符合所述特定通讯标准的对应的传输接口电路,来为主装置50,和记忆装置100进行通讯。

在本实施例中,主装置50可传送主装置指令(host command)与对应的逻辑地址至存储器控制器110来存取记忆装置100。存储器控制器110接收主装置指令与逻辑地址,并将主装置指令转译成记忆体操作指令(可简称为操作指令),再以操作指令控制非挥发性存储器120读取、写入(write)/编程(program)非挥发性存储器120当中某些实体地址的记忆单位(例如数据页面),其中实体地址对应于逻辑地址。当存储器控制器110对非挥发性存储器组件122-1、122-2、…及122-N中的任一非挥发性存储器组件122-n进行一抹除(erase)运作时(符号“n”可表示区间[1,N]中的任一整数),非挥发性存储器组件122-n的多个区块(block)中的至少一个区块可被抹除,其中所述多个区块中的每一区块可包括多个页面(例如数据页面),且一存取运作(例如读取或写入)可对一或多个页面进行,但本发明不限于此。

II.非挥发性存储器架构

图2为依据本发明一实施例的一三维(three-dimensional,3D)NAND型闪存的示意图。例如,上述至少一非挥发性存储器组件(例如一或多个非挥发性存储器组件)中的任一存储器组件,诸如非挥发性存储器组件122-1、122-2、…及122-N中的每一存储器组件,可基于图2所示的三维NAND型闪存来实施,但本发明不限于此。

依据本实施例,所述三维NAND型闪存可包括以一三维架构排列的多个记忆细胞,诸如分别被排列于垂直Z轴的Nz层并且对齐分别对应于X轴、Y轴及Z轴的三个方向的(Nx*Ny*Nz)个记忆细胞{{M(1,1,1),…,M(Nx,1,1)},{M(1,2,1),…,M(Nx,2,1)},…,{M(1,Ny,1),…,M(Nx,Ny,1)}}、{{M(1,1,2),…,M(Nx,1,2)},{M(1,2,2),…,M(Nx,2,2)},…,{M(1,Ny,2),…,M(Nx,Ny,2)}}、…、以及{{M(1,1,Nz),…,M(Nx,1,Nz)},{M(1,2,Nz),…,M(Nx,2,Nz)},…,{M(1,Ny,Nz),…,M(Nx,Ny,Nz)}},且可还包括用于选择控制的多个选择器电路,诸如被排列于所述Nz层上面的一上方层(upper layer)的(Nx*Ny)个上方选择器电路{MBLS(1,1),…,MBLS(Nx,1)}、{MBLS(1,2),…,MBLS(Nx,2)}、…及{MBLS(1,Ny),…,MBLS(Nx,Ny)}、以及被排列于所述Nz层下面的一下方层(lower layer)的(Nx*Ny)个下方选择器电路{MSLS(1,1),…,MSLS(Nx,1)}、{MSLS(1,2),…,MSLS(Nx,2)}、…及{MSLS(1,Ny),…,MSLS(Nx,Ny)}。另外,所述三维NAND型闪存可包括用于存取控制的多个位线(bit line)以及多个字线(word line),诸如被排列于所述上方层上面的一顶部层(top layer)的Nx个位线BL(1)、…及BL(Nx)、以及分别被排列于所述Nz层的(Ny*Nz)个字线{WL(1,1),WL(2,1),…,WL(Ny,1)}、{WL(1,2),WL(2,2),…,WL(Ny,2)}、…及{WL(1,Nz),WL(2,Nz),…,WL(Ny,Nz)}。此外,所述三维NAND型闪存可包括用于选择控制的多个选择线,诸如被排列于所述上方层的Ny个上方选择线BLS(1)、BLS(2)、…及BLS(Ny)、以及被排列于所述下方层的Ny个下方选择线SLS(1)、SLS(2)、…及SLS(Ny),且可还包括用于提供多个参考位准的多个源极线,诸如被排列于所述下方层下面的一底部层(bottom layer)的Ny个源极线SL(1)、SL(2)、…及SL(Ny)。

如图2所示,所述三维NAND型闪存可被区分成沿着Y轴分布的Ny个电路模块PS2D(1)、PS2D(2)、…及PS2D(Ny)。为便于理解,电路模块PS2D(1)、PS2D(2)、…及PS2D(Ny)可具有与一平面NAND闪存(其记忆细胞被排列于一单一层)类似的某些电气特征,因此可分别被视为多个虚拟二维(pseudo-2D)电路模块,但本发明不限于此。另外,电路模块PS2D(1)、PS2D(2)、…及PS2D(Ny)中的任一电路模块PS2D(ny)可包括Nx个次要(secondary)电路模块S(1,ny)、…及S(Nx,ny),其中“ny”可表示区间[1,Ny]中的任一整数。例如,电路模块PS2D(1)可包括Nx个次要电路模块S(1,1)、…及S(Nx,1),电路模块PS2D(2)可包括Nx个次要电路模块S(1,2)、…及S(Nx,2),…,以及电路模块PS2D(Ny)可包括Nx个次要电路模块S(1,Ny)、…及S(Nx,Ny)。在电路模块PS2D(ny)中,次要电路模块S(1,ny)、…及S(Nx,ny)中的任一次要电路模块S(nx,ny)可包括Nz个记忆细胞M(nx,ny,1)、M(nx,ny,2)、…及M(nx,ny,Nz),且可包括对应于记忆细胞M(nx,ny,1)、M(nx,ny,2)、…及M(nx,ny,Nz)的一组选择器电路,诸如上方选择器电路MBLS(nx,ny)以及下方选择器电路MSLS(nx,ny),其中“nx”可表示区间[1,Nx]中的任一整数。上方选择器电路MBLS(nx,ny)、下方选择器电路MSLS(nx,ny)以及记忆细胞M(nx,ny,1)、M(nx,ny,2)、…及M(nx,ny,Nz)可由晶体管来实施。例如,上方选择器电路以及下方选择器电路MSLS(nx,ny)可由不具有任何浮栅(floating gate)的普通晶体管来实施,而记忆细胞M(nx,ny,1)、M(nx,ny,2)、…及M(nx,ny,Nz)中的任一记忆细胞M(nx,ny,nz)可由一浮栅晶体管来实施,其中“nz”可表示区间[1,Nz]中的任一整数,但本发明不限于此。举例来说,记忆细胞M(nx,ny,nz)可用采用电荷捕获(charge-trap,CT)材料的电荷捕获晶体管来实作。此外,在电路模块PS2D(ny)中的上方选择器电路MBLS(1,ny)、…及MBLS(Nx,ny)可依据对应的选择线BLS(ny)上的选择讯号来进行选择,而在电路模块PS2D(ny)中的下方选择器电路MSLS(1,ny)、…及MSLS(Nx,ny)可依据对应的选择线SLS(ny)上的选择讯号来进行选择。

图3依据本发明一实施例绘示图2所示的三维NAND型闪存的某些局部结构。所述三维NAND型闪存可设计成具有多个棒状(rod-shaped)局部结构诸如图3所示的棒状局部结构,而所述多个棒状局部结构可分别被安排来穿过次要电路模块{S(1,1),…,S(Nx,1)}、{S(1,2),…,S(Nx,2)}、…及{S(1,Ny),…,S(Nx,Ny)}。为便于理解,所述多个棒状局部结构可分别被视为图2所示的架构中的次要电路模块{S(1,1),…,S(Nx,1)}、{S(1,2),…,S(Nx,2)}、…及{S(1,Ny),…,S(Nx,Ny)}的相关晶体管的通道,诸如用于实施上方选择器电路MBLS(nx,ny)以及下方选择器电路MSLS(nx,ny)的普通晶体管的信道以及用于实施记忆细胞M(nx,ny,nz)的浮栅晶体管的通道。依据某些实施例,所述多个棒状局部结构的数量可等于次要电路模块{S(1,1),…,S(Nx,1)}、{S(1,2),…,S(Nx,2)}、…及{S(1,Ny),…,S(Nx,Ny)}的总数(Nx*Ny),但本发明不限于此。例如,所述多个记忆细胞的排列可予以变化,而所述多个棒状局部结构的数量可相对应地改变。

另外,所述三维NAND型闪存可被设计成具有多个管状(pipe-shaped)局部结构,且所述多个管状局部结构可被安排来环绕(encircle)所述多个棒状局部结构以形成次要电路模块{S(1,1),…,S(Nx,1)}、{S(1,2),…,S(Nx,2)}、…及{S(1,Ny),…,S(Nx,Ny)}的各个组件,尤其是形成图2所示的架构中所述多个记忆细胞的各个控制栅与各个浮栅以及所述多个选择器电路的各个栅极。记忆细胞{{M(1,1,1),M(2,1,1),…},{M(1,1,2),M(2,1,2),…},…}以及字线{WL(1,1),WL(1,2),…}绘示于图3中,且图3所示的管状局部结构可指出有某些额外局部结构围绕所述多个棒状局部结构的每一者,其中针对这些额外局部结构的细节会在后续的实施例中进一步说明。

图4依据本发明一实施例绘示图2所示的三维NAND型闪存的所述多个记忆细胞中的一个记忆细胞的某些实施细节。如图4所示,记忆细胞M(nx,ny,nz)可包括所述多个棒状局部结构中的一者的一部分,诸如对应于次要电路模块S(nx,ny)的棒状局部结构中的一棒段(rod segment)Mch,且可还包括具有相同对称轴的某些管状局部结构。例如,棒段Mch的上侧Md与下侧Ms可用来当作用于实施记忆细胞M(nx,ny,nx)的浮栅晶体管的漏极(drain)与源极,且这些管状局部结构中的一第一管状局部结构Mfg以及一第二管状局部结构Mcg可用来作为这个浮栅晶体管的浮栅以及控制栅。这些管状局部结构中的其它管状局部结构,诸如棒段Mch与所述第一管状局部结构Mfg之间的管状局部结构以及所述第一管状局部结构Mfg与所述第二管状局部结构Mcg之间的管状局部结构,可由一或多个绝缘材料来实施。

依据某些实施例,图2所示的架构中的所述多个选择器电路中的任一选择器电路可藉由修改图4所示的架构来实施。例如,棒段Mch的上侧Md与下侧Ms可用来作为用于实施这个选择器电路的普通晶体管的漏极与源极,而这些管状局部结构中的第二管状局部结构Mcg可用来作为这个普通晶体管的栅极,其中第一管状局部结构Mfg应从所述一或多个绝缘材料移除。因此,棒段Mch与第二管状局部结构Mcg之间只会有一个管状局部结构,但本发明不限于此。

III.闪存基本特性测量

依据某些实施例,存储器控制器110可利用ECC及随机化器电路114E来进行写入程序中的随机化以及ECC编码,以及进行读取程序中的ECC解码以及去随机化(de-randomizing)。举例来说,存储器控制器110可利用ECC及随机化器电路114E来于写入时进行写入随机化操作并且随后进行ECC编码操作,之后,于读取时进行ECC解码操作并且随后进行去随机化操作。在另一例子中,存储器控制器110可利用ECC及随机化器电路114E来于写入时进行ECC编码操作并且随后进行随机化操作,之后,于读取时进行去随机化操作并且随后进行ECC解码操作。尤其,ECC及随机化器电路114E可包括分别用以进行ECC编码操作以及ECC解码操作的一ECC编码器以及一ECC解码器,且ECC及随机化器电路114E可还包括分别用以进行随机化操作以及去随机化操作的一随机化器以及一去随机化器(de-randomizer),但本发明不限于此。在上述随机化操作下,非挥发性存储器120中的位0以及位1的各自的出现的机率可彼此相似或相等。

非挥发性存储器120中的电荷分布可用阈电压(threshold voltage,简称Vth)分布图来绘示,并且可对应于每记忆细胞的位数,其中阈电压(Vth)可用来侦测存储于记忆细胞中的位信息,并且可依据某些观点称为感测电压或读取电压(尤其是关于电压的读取点)。举例来说,用于TLC记忆细胞的一TLC阈电压分布图可具有8个(例如2

图5依据本发明一实施例绘示一阈电压追踪(Vth-tracking,可简称“Vth追踪”)控制方案,以及图6绘示图5所示的阈电压追踪控制方案的某些实施细节。在图5所示的工作流程中,存储器控制器110可尝试依序进行N2处理、N4处理、N6处理以及N8处理(于图6中分别标示为“N2”、“N4”、“N6”,以及“N8”以求简明),直到某条件(例如可更正(correctable)、不可更正(uncorrectable)等)被满足为止。举例来说,存储器控制器110可利用ECC及随机化器电路114E中的一或多个ECC电路(例如一或多个ECC引擎)来进行ECC解码,诸如N2处理、N4处理、N6处理以及N8处理中的至少一部分(例如一部分或全部)的解码,但本发明不限于此。当工作流程进行到N2处理时,存储器控制器110可能已经尝试了阈电压(Vth)的一个候选读取电压(例如图6所示的第一个(1

存储器控制器110可使用第一个候选读取电压的位信息(在图5标示为“+1读取”,以求简明)来进行N2处理,以及进行硬解码,并且检查码字(codeword)是否为可更正,其中若是没有错误的状况则可被视为可更正。若是,进入左下角的步骤;若否,则触发N4处理。存储器控制器110可使用第一个、第二个、第三个候选读取电压的位信息(在图5标示为“+3读取”,以求简明)来进行N4处理,以及进行软解码(soft-decoding),并且检查码字是否为可更正,其中这个位信息可包括一个符号位(sign bit;也可称为“正负号位”)以及一个软位(soft bit)。若是,进入左下角的步骤;若否,则触发N6处理。存储器控制器110可使用第一个、第二个、第三个、第四个、第五个候选读取电压的位信息(在图5标示为“+5读取”,以求简明)来进行N6处理,以及进行软解码,并且检查码字是否为可更正,其中这个位信息可包括一个符号位以及两个软位。若是,进入左下角的步骤;若否,则触发N8处理。存储器控制器110可使用第一个、第二个、第三个、第四个、第五个、第六个、第七个候选读取电压的位信息(在图5标示为“+7读取”,以求简明)来进行N8处理,以及进行软解码,并且检查码字是否为可更正,其中这个位信息可包括一个符号位以及两个软位。若是,进入左下角的步骤;若否,存储器控制器110可调整所述一或多个ECC电路的一或多个解码参数来继续进行N8处理。举例来说,存储器控制器110可尝试多个解码参数的各种组合来进行N8处理,并且检查所述码字是否为可更正。所述多个解码参数的例子可包括(但不限于):感测步进大小(stepsize)、解码器内部系数(decoder internal coefficient)、以及针对动态微调对数似然比(Log-likelihood ratio,LLR)的某些参数。若所述码字是不可更正且执行N8处理的循环(loop)的次数达到一预定数,诸如最大循环数(于图5标示“已达最大循环数”,以求简明),存储器控制器110可判断发生读取失败,并且进入下一复原层级(recovery stage);否则,存储器控制器110则可继续进行N8处理。在左下角的步骤中,存储器控制器110可取得一可更正码字,以及收集到追踪结果。举例来说,这些追踪结果可包括已经尝试过的候选读取电压,诸如绘示于图6所示的N2处理、N4处理、N6处理以及N8处理中的垂直线,其中这些垂直线可被标示为“1

图7依据本发明一实施例绘示如图5所示的阈电压追踪控制方案的某些复原层级以及这些复原层级之间的关系,其中低密度奇偶校验(low-density parity-check,LDPC)解码可被视为所述ECC解码的例子(于图7中以LDPC步进(LDPC Step)来呈现)。复原索引(recovery index;或称为复原指数)1、2、3、4、5等的总数(例如N_max-index,诸如15或20)可对应于所述最大循环数(例如N_max-loop,诸如10或15)。当存储器控制器110在N2处理中以默认(default)的方式保留最后一个读取电压以直接取得所述可更正码字、或在N2处理中进行硬解码以取得所述可更正码字时,所述ECC解码的色彩层级(color stage)可被视为绿色,这可指出最佳状况。当存储器控制器110以Vth追踪来进行N4处理以取得所述可更正码字时,所述ECC解码的色彩层级可被视为黄色。当存储器控制器110以Vth追踪来进行N6处理以取得所述可更正码字时,所述ECC解码的色彩层级可被视为棕色。当存储器控制器110以Vth追踪来进行N8处理以取得所述可更正码字时,例如藉由在所述最大循环数(例如N_max-loop,诸如10或15)内执行N8处理的循环多次,所述ECC解码的色彩层级可被视为橙色。当发生SLC或TLC ECC失败时,例如进入图5左下角的步骤,所述ECC解码的色彩层级可被视为红色,这可指出最坏状况。由于N2处理对应于复原索引1与2,且由于N4处理以及N6处理分别对应于复原索引3与4,所以N8处理可对应于复原索引{5,6,…,(N_max-index-1)}(例如{5,6,…,14}或{5,6,…,19}),且所述SLC或TLC ECC失败可对应于复原索引N_max-index(例如15或20),其中N_max-index=(4+N_max-loop+1)=(N_max-loop+5)。

图8依据本发明一实施例绘示图5所示的阈电压追踪控制方案的一测试流程。依据本实施例,一生产工具(production tool)诸如另一主装置(例如个人计算机,诸如桌面计算机以及膝上型计算机)可进行所述测试流程,以及多个样本可安装于具有与记忆装置100相同的产品型号的多个记忆装置上,但本发明不限于此。举例来说,所述多个样本可代表具有与非挥发性存储器120相同的产品型号的多个非挥发性存储器。在另一例子中,所述多个样本可代表具有与非挥发性存储器组件122-1、122-2、…与122-N相同的产品型号的一组非挥发性存储器组件。

所述测试流程可包括一系列测试程序(test procedure),诸如一致性(Uniformity)、准备区块(Prepare blocks)、读取扰动(Read disturbance)、数据保留(Data retention)、跨温度(Cross temperature)以及耐久度(Endurance),以供测试所述多个样本。在上述一致性的测试程序中,所述生产工具可测试所述多个样本的基本状态的一致性,其中编程/抹除交替循环(Program and Erase(P/E)cycle)可等于5或其他值。于上述准备区块的测试程序中,所述生产工具可准备分别属于交替循环为1、150,500、1000、1500、3000、5000以及10000的多个编程/抹除(P/E)群组的区块(诸如分别经历1、150、500、1000、1500、3000、5000以及10000个交替循环的编程/抹除的八群区块)。在上述读取扰动的测试程序中,所述生产工具可藉由读取来进行测试,例如进行整个区块的读取以及单一页面的读取。在上述数据保留的测试程序中,所述生产工具可在100℃的条件下用各种时间长度诸如0、2、4、6、8、16、20以及24小时来对所述多个样本的数据保留进行测试。在上述跨温度的测试程序中,所述生产工具可用各种温度值诸如0℃至70℃的温度范围内的温度值来对所述多个样本进行测试。在上述耐久度的测试程序,所述生产工具可分别在SLC以及TLC模式下对于所述多个样本进行耐久度的测试,如此一来,所述生产工具便可侦测所述多个样本的操作范围。针对所述多个样本中的任何样本,其操作范围可对应于所述样本以及耦接于所述样本的控制器集成电路(Integrated circuit(IC);尤其是一ECC电路以及其内的一讯号处理模块)的组合。所述生产工具可利用上述操作范围来作为针对服务质量(quality of service,QoS)的量测结果。

依据某些实施例,上述生产工具可被称为一第一生产工具,且所述多个样本的至少一部分(例如一部分或全部)可被安装于耦接至所述第一生产工具的一第二生产工具,诸如具有与记忆装置100相同的产品型号的另一记忆装置,并且所述另一记忆装置可具有一变更的(modified)架构(例如一或多个插槽(socket)等),以供安装所述多个样本的上述至少一部分。

图9依据本发明一实施例绘示通过图8所示的测试流程而取得的某些测试结果。如图9所示,对于耐久度的测试可随着编程/抹除(P/E)交替循环(例如:1、150、500、1000、1500、3000、5000以及10000个交替循环;于图9中以“PE”来表示P/E交替循环)而在垂直方向上有所变化,以及,对于数据保留的测试可随时间(例如:在100℃的条件下分别采用0、2、4、6、8、16、20以及24小时的时间长度)而在水平方向上有所变化。不同程度的阴影(shading)可用以指出各自所达到的最大复原索引,其中百分比可用以指出N2触发率(triggerrate),诸如仅触发N2处理(而不会触发N4处理、N6处理以及N8处理)的比率。对于企业用户而言,对于一组预定条件(例如:耐久交替循环为10000,在55℃下的数据保留为三个月…等),N2触发率的可定义为99.99%,但本发明不限于此。基于此要求,所述数据应在100℃下烘烤2小时的条件下,在一个快闪读取忙碌时间(flash read busy time)tR(例如0.1至0.2毫秒(millisecond,ms)的读取延迟)内正确地回传到主机端。因此,可能需要优化具有小于99.9%的N2触发率的相关操作范围。

图10依据本发明一实施例绘示针对某一耐久交替循环(endurance cycle)诸如150个编程/抹除(program and erase,P/E)交替循环的TLC阈电压分布图,以及图11依据本实施例绘示针对一较高耐久交替循环诸如5000个编程/抹除交替循环的TLC阈电压分布图,其中所示的两个TLC阈电压分布图对应于室温数据保留。图例(legend)诸如DAY00、DAY02、DAY06、DAY09、DAY12和DAY14可对应于沿着时间轴的一系列时间点{0,2,6,9,12,14},以日或24小时为单位。当编程/抹除(P/E)交替循环达到150(在图10中标示为“PE:150”,以求简明),Vth移位的最大或较大移位量可在头两天内发生,接着Vth移位可逐渐达到饱和状态。当编程/抹除(P/E)交替循环达到5000(在图11中标示为“PE:5000”,以求简明),Vth移位的最大或较大移位量可在头两天内发生,接着Vth移位可逐渐达到饱和状态。依据本实施例,存储器控制器110的ECC电路的错误更正能力足以涵盖这两个TLC阈电压分布图中的Vth移位,尤其是通过N2处理来实现,而不需要进行N4处理、N6处理以及N8处理中的任何处理。

IV.背景扫描机制

图12依据本发明一实施例绘示使用一背景扫描控制方案来处理的某些实体区块。依据本实施例,存储器控制器110可对非挥发性存储器120进行背景扫描以读取多个逻辑存取单元(logical access unit,可简称LAU)诸如LAU#0、LAU#1等中的每一逻辑存取单元(LAU)中的区块#0、区块#1、…与区块#4855的每一区块中的页面#0、页面#1、…与页面#1727中的一或多个页面,其中图12所示的这多列(column)区块分别属于这个逻辑存取单元(例如LAU#0)的平面#0、平面#1、平面#2和平面#3。存储器控制器110可用分时多任务(timedivision)的方式来进行所述背景扫描,尤其,可每次读取一小部分数据,并且在一预定时间长度内(例如14天)内完成一次所述背景扫描。举例来说,存储器控制器110可读取所述多个逻辑存取单元诸如LAU#0、LAU#1等中的每一逻辑存取单元(LAU)中的每一区块中的一个页面,且在下一个区块中要读取的页面的编号可不同于在当前区块中要读取的页面的编号,但本发明不限于此。举例来说,所有数据可在所述预定时间长度内(例如14天)内读取一次。

于进行所述背景扫描的期间,存储器控制器110可收集(例如记录)非挥发性存储器120的阈电压分布的波谷(例如介于山状部分之间的谷状部分(valley-like portion))的谷信息以优化读取电压,以供于进行读取时被使用。尤其,当有一或多个错误发生时,存储器控制器110可收集(例如记录)每ECC组块的错误位数量(error bit number per ECCchunk),并且可另进行Vth追踪以决定出最佳读取电压。

图13依据本发明一实施例绘示针对一噪声容限(noise margin)记录控制方案的一TLC阈电压分布图,图14绘示对应于图13所示的TLC阈电压分布图的谷位置及高度图,以及图15绘示图13所示的TLC阈电压分布图中的一部分的波谷(例如:于图13中的用虚线绘示的框内的波谷)的某些硬解码通过范围(hard-decoding pass range,简称HD通过范围),其中编程/抹除(P/E)交替循环可为5000次(于图13中标示为“PE:5000”,以求简明)。图例诸如HR00、HR02、HR04、HR06、HR08、HR16、HR20与HR24可对应于沿着时间轴的一系列时间点{0,2,4,6,8,16,20,24},以小时为单位。

如图14所示,所述谷信息可包括针对图13所示的曲线中的每一曲线的多个波谷中的每一波谷的一谷位置(valley location)以及一谷高度(valley height),其中所述谷位置以及所述谷高度可被记录为一对应点(在图14中标示为圆圈,以用其圆心来清楚表示所述点的位置)的水平以及垂直坐标值。举例来说,所述谷高度可用细胞数量(cell number)诸如所述阈电压分布图中的细胞数量来测量,并而可用沿图14的垂直轴的线性刻度比来说明,但本发明不限于此。在另一例子中,依据某些观点,所述谷高度可被视为错误量。如图15所示,所述谷信息可还包括一谷宽度(valley width),诸如:针对N2处理,从所述谷位置朝向包括这个波谷的曲线(例如电压分布曲线)延伸的一最大可延伸电压范围(maximumextendable voltage range)。在上述最大可延伸电压范围内,存储器控制器110能够仅通过N2处理来取得所述可更正码字,而不需要进行N4处理、N6处理以及N8处理中的任何处理。存储器控制器110可尝试从所述谷位置朝向包括这个波谷的所述曲线延伸一初始可延伸电压范围,尤其,可依据是否有需要进行N4处理、N6处理以及N8处理中的任何处理,进行二元搜寻(binary search),以决定出只需要用到N2处理的所述最大可延伸电压范围。如此一来,存储器控制器110可将所述最大可延伸电压范围记录为所述谷宽度。依据某些观点,所述谷宽度可被视为一HD通过范围。

依据某些实施例,存储器控制器110可将关于非挥发性存储器120内的实体位置(例如实体地址)的属于非挥发性存储器120的谷信息记录至一或多个表中,并且可将所述一或多个表存储至存储器控制器110中的某一存储单元的存储空间中,以供进一步使用。举例来说,存储器控制器110可依据所述谷信息来优化读取电压。

V.通过机器学习的针对读取电压的准确设定

存储非挥发性存储器120中的所有记忆细胞的阈电压分布特性(例如谷信息)将有助于准确地读取非挥发性存储器120中的这些记忆细胞的每一记忆细胞中所存储的位,但此作法需要庞大的存储空间,因此不符合实际需求。藉由依据阈电压分布的波谷的谷信息进行基于一强化学习模型(reinforcement learning model)的机器学习,存储器控制器110能够在进行读取的期间准确地设定读取电压。如此一来,原先所需要的庞大的存储空间可被大幅降低。

在所述背景扫描中,存储器控制器110可加载一阈电压追踪程序(Vth-trackingprocedure)以依据所述阈电压追踪控制方案来进行阈电压追踪。当上述最佳读取电压在所述阈电压追踪中被找到,存储器控制器110可收集多个实体配对页面(physical pairpage)(例如:对一TLC闪存而言,分别对应于最低有效位(least significant bit,LSB)、中间有效位(central significant bit,CSB)以及最高有效位(most significant bit,MSB)的三个逻辑页面)的谷信息,诸如谷位置、谷高度以及谷宽度(例如HD通过范围)。由于所述TLC闪存的一个实体配对页面具有对应于七个波谷的七个读取点,所以会有七组对应的谷信息。存储器控制器110可将谷信息发送至所述强化学习模型,以找出最短解码延迟读取点(例如最佳读取电压)。所述强化学习模型可表示如下:

其中N

在进行大量的背景扫描以后,存储器控制器110可收集到分别对应于各个波谷的谷信息。存储器控制器110可用轮流或同时的方式来进行所述背景扫描以及进行基于所述强化学习模型的所述机器学习。通过所述机器学习,存储器控制器110可取得分别对应于各个波谷的最佳读取电压,诸如优化的(optimized)读取点{t

针对所述机器学习的某些实施细节可说明如下。谷高度VH的值较高时可指出所述读取点是错误的,尤其可指出有较多的错误位。谷高度VH的值较低时可指出所述读取点是正确的或几乎正确的,尤其可指出有较少的错误位。另外,所述谷宽度诸如HD通过范围HD_pass_Win可指出硬解码应该会成功的范围。若HD通过范围HD_pass_Win较高时,则表示所述读取点可具有较大的兼容性,并且可容许此读取点有位移,诸如对应于较小谷宽度的其他输入(例如一或多个其他输入型样(pattern)的读取点)。此外,当谷高度VH为高且谷宽度诸如HD通过范围HD_pass_Win为窄时,权重函数Coef

图16依据本发明一实施例绘示通过一强化学习(reinforcement learning)控制方案从图10所示的TLC阈电压分布图的谷信息取得的某些最佳读取点,以及图17绘示通过本实施例中的所述强化学习控制方案从图11所示的TLC阈电压分布图中的谷信息取得的某些最佳读取点。依据本实施例,微处理器112可控制存储器控制器110依据所述强化学习控制方案来进行操作,尤其,可进行基于所述强化学习模型的所述机器学习以从非挥发性存储器120的阈电压分布的谷信息找出最佳读取点。举例来说,在编程/抹除(P/E)交替循环达到150次的情况下(于图16中标示为“PE:150”,以求简明),存储器控制器110可找出对应于某一长度的数据寿命(data life time)的最佳读取点,诸如对应于数据寿命为14天的最佳读取点,如图16中的于图例DAY14的曲线上的以虚线绘示的圆圈所示。在另一例子中,在编程/抹除(P/E)交替循环达到5000次的情况下(于图17中标示为“PE:5000”,以求简明),存储器控制器110可找出对应于某一长度的数据寿命的最佳读取点,诸如对应于数据寿命为14天的最佳读取点,如图17中的于图例DAY14的曲线上的以虚线绘示的圆圈所示。此外,存储器控制器110可对非挥发性存储器120中的复数个区块进行损耗均衡(wear leveling)以使所述复数个区块中的所有区块的编程/抹除(P/E)交替循环变得平均。无论所述复数个区块的编程/抹除(P/E)交替循环是较高或较低,存储器控制器110可找出对应于某一长度的数据寿命的最佳读取点,诸如对应于数据寿命为14天的最佳读取点,如图16及图17中的任一者所示。

依据某些实施例,微处理器112可控制存储器控制器110依据所述强化学习控制方案来操作,尤其,可进行基于所述强化学习模型的所述机器学习以分别针对不同长度的数据寿命(例如不同范围的数据寿命)来从非挥发性存储器120的阈电压分布的谷信息找出上述最佳读取点。举例来说,存储器控制器110可找出对应于数据寿命落入一第一范围的一第一组最佳读取点,以及藉由使用所述第一组最佳读取点来读取对应于数据寿命落入所述第一范围的数据。另外,存储器控制器110可找出对应于数据寿命落入一第二范围的一第二组最佳读取点,以及藉由使用所述第二组最佳读取点来读取对应于数据寿命落入所述第二范围的数据。此外,存储器控制器110可找出对应于数据寿命落入一第三范围的一第三组最佳读取点,以及藉由使用所述第三组最佳读取点来读取对应于数据寿命落入所述第三范围的数据。

图18依据本发明一实施例绘示指出数据保留改善的三组曲线,其中这三组曲线可包括:对应于原始错误投影(original error projection)的一第一组曲线、对应于正常解码错误投影(normal decoded error projection)的一第二组曲线、以及对应于最佳读取解码错误投影(best read decoded error projection)的一第三组曲线。在水平轴上的码字错误(codeword error)可代表每千字节ECC组块的错误位数(error bit count per 1KBECC chunk),诸如在一千字节(kilobyte,KB)的一ECC组块中的错误位的数量。垂直轴上的帧错误率(frame error rate,FER)可表示如下:

FER=1-Pro(error_bit_count_per_chunk 其中Pro()可代表一投影(projection)诸如映射(mapping),error_bit_count_per_chunk可代表每组块的错误位数(error bit count per chunk)诸如上述每千字节ECC组块的错误位数,以及t可代表水平轴上的坐标值。在图18中,图例诸如1、150、500、1000、1500、3000、5000以及10000可分别对应于编程/抹除(P/E)交替循环的数量,诸如1、150、500、1000、1500、3000、5000以及10000个交替循环(例如分别执行1、150、500、1000、1500、3000、5000以及10000次“编程接着抹除”),以及对应于图例LDPCHd的垂直线(例如图18所示的垂直虚线)可指出低延迟解码的一更正能力阈值(例如仅触发N2处理)。举例来说,其数据寿命的长度可为14天。 假设存储器控制器110可被配置为在读取的期间利用一组默认(default)读取电压(例如固定的读取电压)。在此情况下,所述第一组曲线可延伸至所述更正能力阈值的右侧而远离所述更正能力阈值,这是这三组曲线中的最坏状况。举例来说,对应于图例1的曲线以及对应于图例LDPCHd的垂直线的交点可具有在10 依据本实施例,存储器控制器110可被配置为于读取的期间利用一组最佳读取电压(例如从基于所述强化学习模型的所述机器学习取得的读取电压)。在此情况下,所述第三组曲线中的大部分可位于所述更正能力阈值的左侧,这是这三组曲线中的最佳状况。为了使所述第三组曲线的全部都位于所述更正能力阈值的左侧以避免对应于图例10000的曲线以及对应于图例LDPCHd的垂直线的任何交点的产生,存储器控制器110可减少所述背景扫描的周期。因此,存储器控制器110可保持留在所述低延迟解码(例如仅触发N2处理)并且避免所述高延迟解码。 VI.强健的控制机制 依据某些实施例,所述电子装置10的至少一部分,诸如主装置50(例如其内的处理器52)以及记忆装置100(例如其内的存储器控制器110)中的至少一者,可用来触发记忆装置100中的非挥发性存储器120(尤其是非挥发性存储器组件122-1、122-2、…与122-N)的所述背景扫描以及依据非挥发性存储器120的谷信息来进行基于所述强化学习模型的所述机器学习,以产生或更新多个表,诸如表TB1、TB2以及TB3。所述多个表中的每一表可存储一组读取电压来作为非挥发性存储器120的分别针对不同段(section)数据寿命的最佳读取点,以及这些段数据寿命可包括:一第一段数据寿命、一第二段数据寿命以及一第三段数据寿命,例如,依序从年轻到老。表TB1可存储一第一组读取电压(例如用于TLC记忆细胞的7个读取电压、用于QLC记忆细胞的15个读取电压等)作为非挥发性存储器120的针对所述第一段数据寿命的最佳读取点,表TB2可存储一第二组读取电压(例如用于TLC记忆细胞的7个读取电压、用于QLC记忆细胞的15个读取电压等)作为非挥发性存储器120的针对所述第二段数据寿命的最佳读取点,以及表TB3可存储一第三组读取电压(例如用于TLC记忆细胞的7个读取电压、用于QLC记忆细胞的15个读取电压等)作为非挥发性存储器120的针对所述第三段数据寿命的最佳读取点。另外,于读取具有某数据寿命的数据时,记忆装置100(例如存储器控制器110)可依据对应于这数据寿命的最佳读取点来读取所述数据。举例来说,存储器控制器110可从所述多个表诸如表TB1、TB2以及TB3选取对应于(所述数据的)所述数据寿命的某一表,以从这个表取得对应于(所述数据的)所述数据寿命的最佳读取点,来通过N2处理达到最佳读取效能。 图19依据本发明一实施例绘示一种借助于机器学习来针对记忆装置的服务质量优化进行存取控制的方法,其中以上实施例中的某些实施例中的控制方案(例如:所述阈电压追踪控制方案、所述背景扫描控制方案、所述噪声容限记录控制方案、以及所述强化学习控制方案)可被采用于所述方法中。所述方法可被应用于电子装置10、记忆装置100、以及可用以控制非挥发性存储器120的存取的存储器控制器110。举例来说,记忆装置100(例如存储器控制器110)可依据所述方法来操作。尤其,表及数据刷新控制电路114TD可依据所述方法,于进行读取的期间为存储器控制器110从表TB1、TB2以及TB3中选取一适当表,并且为存储器控制器110管理及更新表TB1、TB2以及TB3。基于所述方法,存储器控制器110可借助于基于所述强化学习模型的所述机器学习来针对记忆装置100的服务质量优化进行存取控制。 如图19所示,存储器控制器110(例如:表及数据刷新控制电路114TD)可进行对应于第1周、第2周、第3周、第4周、第5周、第6周等诸如周#1、周#2、周#3、周#4、周#5、周#6等(例如:以一天或24小时为单位,沿着时间轴,介于时间点{0,7,14,21,28,35,42,…}的一系列连续的时间区间)的一系列的操作,其中用于进行所述系列操作的周期可为一周,但本发明不限于此。举例来说,存储器控制器110可进行背景扫描(于图19中标示为“BS”,以求简明)以通过基于所述强化学习模型的所述机器学习来预先准备表TB1、TB2以及TB3。另外,存储器控制器110可进行背景扫描以于一当前周(例如:周#1、周#2等中的任何周)中通过基于所述强化学习模型的所述机器学习来更新表TB1、TB2以及TB3中的至少一部分(例如一部分或全部),尤其可依照这些表是否会于这周被使用。举例来说,存储器控制器110可进行背景扫描以从第一周诸如周#1开始每周更新表TB1,进行背景扫描以从第二周诸如周#2开始每周更新表TB2,以及进行背景扫描以从第三周诸如周#3开始每周更新表TB3。 于第一周诸如周#1内,存储器控制器110可写入第一数据以及使用表TB1来读取所述第一数据。举例来说,表及数据刷新控制电路114TD可选取表TB1作为这周内用于所述第一数据的适当表。于第二周诸如周#2内,存储器控制器110可使用表TB2来读取所述第一数据,这是因为所述第一数据的数据保留特性可能会恶化。举例来说,表及数据刷新控制电路114TD可选取表TB2作为这周内用于所述第一数据的所述适当表。于第三周诸如周#3内,存储器控制器110可使用表TB3来读取所述第一数据,且可对所述第一数据进行数据刷新,这是因为所述第一数据的数据保留特性可能会更加恶化。举例来说,表及数据刷新控制电路114TD可选取表TB3作为这周内用于所述第一数据的所述适当表。于所述第一数据的所述数据刷新的期间,存储器控制器110(例如表及数据刷新控制电路114TD)可将通过使用表TB3从至少一旧的实体地址(其可指出一或多个旧的实体页、一或多个旧的实体区块等)刚被读取的所述第一数据写入到至少一新的实体地址(其可指出一或多个其他实体页、一或多个其他实体区块等),无效化(invalidate)于上述旧的实体地址的存储单元,以及更新所述第一数据的逻辑地址与实体地址之间的逻辑对实体地址映射关系(logical-to-physicaladdress mapping relationship),以将所述第一数据刷新为位于上述新的实体地址的相同数据(也就是和所述第一数据相同的数据),但本发明不限于此。在另一例子中,于所述第一数据的所述数据刷新的期间,存储器控制器110(例如表及数据刷新控制电路114TD)可使用表TB3来从上述旧的实体地址读取所述第一数据,并且将所述第一数据写入至上述新的实体地址,无效化于上述旧的实体地址的所述存储单元,以及更新这个映射关系,以将所述第一数据刷新为位于上述新的实体地址的所述相同数据(也就是和所述第一数据相同的数据)。 于第二周诸如周#2内,存储器控制器110可写入第二数据以及使用表TB1来读取所述第二数据。举例来说,表及数据刷新控制电路114TD可选取表TB1作为这周内用于所述第二数据的适当表。于第三周诸如周#3内,存储器控制器110可使用表TB2来读取所述第二数据,这是因为所述第二数据的数据保留特性可能会恶化。举例来说,表及数据刷新控制电路114TD可选取表TB2作为这周内用于所述第二数据的所述适当表。于所述第四周诸如周#4内,存储器控制器110可使用表TB3来读取所述第二数据,且可对所述第二数据进行数据刷新,这是因为所述第二数据的数据保留特性可能会更加恶化。举例来说,表及数据刷新控制电路114TD可选取表TB3作为这周内用于所述第二数据的所述适当表。于所述第二数据的所述数据刷新的期间,存储器控制器110(例如表及数据刷新控制电路114TD)可将通过使用表TB3从至少一旧的实体地址(其可指出一或多个旧的实体页、一或多个旧的实体区块等)刚被读取的所述第二数据写入到至少一新的实体地址(其可指出一或多个其他实体页、一或多个其他实体区块等),无效化于上述旧的实体地址的存储单元,以及更新所述第二数据的逻辑地址与实体地址之间的逻辑对实体地址映射关系,以将所述第二数据刷新为位于上述新的实体地址的相同数据(也就是和所述第二数据相同的数据),但本发明不限于此。在另一例子中,于所述第二数据的所述数据刷新的期间,存储器控制器110(例如表及数据刷新控制电路114TD)可使用表TB3来从上述旧的实体地址读取所述第二数据,并且将所述第二数据写入至上述新的实体地址,无效化于上述旧的实体地址的所述存储单元,以及更新这个映射关系,以将所述第二数据刷新为位于上述新的实体地址的所述相同数据(也就是和所述第二数据相同的数据)。 在对应于周#1、周#2、周#3、周#4、周#5、周#6等的所述系列操作中,关于在后续的周#3、周#4、周#5、周#6等内写入的数据的操作可依此类推,同理可得。另外,表及数据刷新控制电路114TD可进行下列操作:于进行读取的期间为存储器控制器110从表TB1、TB2以及TB3中选取上述适当表的操作;为存储器控制器110管理及更新表TB1、TB2以及TB3的操作;以及于某数据的数据寿命达到一预定值诸如14天或336小时时刷新所述数据(例如所述第一数据、所述第二数据等)的操作;但本发明不限于此。依据某些实施例,微处理器112可进行这些操作中的至少一部分(例如一部分或全部)。举例来说,微处理器112可进行这些操作中的所有操作,以及表及数据刷新控制电路114TD可被忽略(例如不需要设置)。基于图19所示的方法,存储器控制器110能确保整个系统(例如主装置50以及记忆装置100)妥善地运作,以避免相关技术中的问题,诸如位错误率(bit error rate)提高、随机读取延迟增加、以及所述数据保留问题所衍生出的某些相关问题。为了简明起见,本实施例与前述实施例相仿的内容在此不重复赘述。 图20是依据本发明一实施例的如图19所示方法的工作流程。为了更好的理解,所述工作流程的某些步骤的操作可被描述为多个阶段Phase(0)、Phase(1)以及Phase(2)中的操作。举例来说,阶段Phase(0)可代表记忆装置100的一生产阶段(production phase),以及阶段Phase(1)以及Phase(2)可代表供用户使用记忆装置100的一用户阶段的多个子阶段,但本发明不限于此。依据某些实施例,阶段Phase(0)以及Phase(1)可代表记忆装置100的一生产阶段的多个子阶段,以及阶段Phase(2)可代表供用户使用记忆装置100的一用户阶段。另外,一系列时间区间诸如{period(1),period(2),…}可被描述为{period(i)},其中索引i可为一正整数。图19所示的实施例中对应于周#1、周#2等的所述系列操作可分别视为所述系列时间区间{period(1),period(2),…}中由存储器控制器110所进行的相关操作的例子。举例来说,于某一时间区间诸如period(i)(例如周#1、周#2等中的任何周)内由存储器控制器110所写入至非挥发性存储器120的所有数据可被统称为数据DATA(i)。在另一例子中,于某一时间区间诸如period(i)内由存储器控制器110所写入至非挥发性存储器120的所有刷新的(refreshed)数据可被统称为数据DATA_RF(i)。 在阶段Phase(0)中,一第一生产工具诸如另一主装置(例如个人计算机,诸如桌面计算机及膝上型计算机)可对多个测试样本进行背景扫描,以及依据所述多个测试样本的谷信息来进行基于所述强化学习模型的所述机器学习,以产生表TB1、TB2以及TB3的各自的初始版本(initial version)。举例来说,所述多个测试样本可代表具有与非挥发性存储器120相同的产品型号的多个非挥发性存储器。在另一例子中,所述多个测试样本可代表具有与非挥发性存储器组件122-1、122-2、…与122-N相同的产品型号的一组非挥发性存储器组件。依据本实施例,所述多个测试样本可被安装于具有与记忆装置100相同的产品型号的多个记忆装置,但本发明不限于此。依据某些实施例,所述多个测试样本的至少一部分(例如一部分或全部)可被安装于耦接至所述第一生产工具的一第二生产工具,诸如具有与记忆装置100相同的产品型号的另一记忆装置,以及所述另一记忆装置可具有一变更的架构(例如一或多个插槽等),以供安装所述多个测试样本的上述至少一部分。 在阶段Phase(1)中,存储器控制器110(例如微处理器112)可对记忆装置100中的非挥发性存储器120(尤其,非挥发性存储器组件122-1、122-2、…与122-N)进行背景扫描以及依据非挥发性存储器120的谷信息进行基于所述强化学习模型的所述机器学习,以产生表TB1、TB2以及TB3的各自的客制化版本(customized version)。如此一来,存储器控制器110(例如微处理器112)可将表TB1、TB2以及TB3的各自的初始版本更新为表TB1、TB2以及TB3各自的客制化版本。 在阶段Phase(2)中,存储器控制器110可进行前景(foreground)以及背景(background)处理。所述前景处理可包括步骤S10至S18的操作,以及所述背景处理可包括步骤S20~S23的操作。为了有更好的理解,对应于C语言的某些伪码(pseudo code)可用来说明这个工作流程,但本发明不限于此。举例来说,伪码“i++”可代表以增量诸如一来增加索引i,以及伪码“i=1”可代表将索引i的初始值设为1。 在步骤S10中,于第一时间区间诸如period(1)内,存储器控制器110可写入数据DATA(i)(例如数据DATA(1)),且使用表TB1来读取数据DATA(i)(例如数据DATA(1))。之后,存储器控制器110可用增量诸如一来增加索引i。 在步骤S11中,存储器控制器110可检查是否i<3。若i<3,则进入步骤S12;否则,进入步骤S13。 在步骤S12中,于当前时间区间诸如period(i)(例如:第二时间区间诸如period(2))内,存储器控制器110可写入数据DATA(i)(例如数据DATA(2)),使用表TB1来读取数据DATA(i)(例如数据DATA(2)),以及使用表TB2来读取数据DATA(i-1)(例如数据DATA(1))。之后,存储器控制器110可用增量诸如一来增加索引i。 在步骤S13中,于当前时间区间诸如period(i)(例如:第三时间区间诸如period(3),或后续时间区间诸如period(4)、period(5)等中的一者)内,存储器控制器110可写入数据DATA(i),使用表TB1来读取数据DATA(i),使用表TB2来读取数据DATA(i-1),以及使用表TB3来读取数据DATA(i-2)。之后,存储器控制器110可用增量诸如一来增加索引i。 在步骤S14中,于当前时间区间诸如period(i)(例如:所述第三时间区间诸如period(3),或后续时间区间诸如period(4)、period(5)等中的一者)内,存储器控制器110可将数据DATA(i-2)刷新为数据DATA_RF(i),以及使用表TB1来读取数据DATA_RF(i)。 在步骤S15中,存储器控制器110可检查是否i<4。若i<4,则进入步骤S13;否则,进入步骤S16。 在步骤S16中,于当前时间区间诸如period(i)(例如:第四时间区间诸如period(4),或后续时间区间诸如period(5)、period(6)等中的一者)内,存储器控制器110可使用表TB2来读取数据DATA_RF(i-1)。 在步骤S17中,存储器控制器110可检查是否i<5。若i<5,则进入步骤S13;否则,进入步骤S18。 在步骤S18中,于当前时间区间诸如period(i)(例如第五时间区间诸如period(5),或后续时间区间诸如period(6)、period(7)等中的一者)内,存储器控制器110可使用表TB3来读取数据DATA_RF(i-2)。请注意,于步骤S15、S17以及S18中的任何步骤至步骤S13的子流程中,存储器控制器110可用增量诸如一来增加索引i。 在步骤S20中,于所述第一时间区间诸如period(1)内,存储器控制器110可进行背景扫描以更新表TB1。之后,存储器控制器110可用增量诸如一来增加索引i。 在步骤S21中,存储器控制器110可检查是否i<3。若i<3,则进入步骤S22;否则,进入步骤S23。 在步骤S22中,于当前时间区间诸如period(i)(例如所述第二时间区间诸如period(2))内,存储器控制器110可进行背景扫描以更新表TB1以及TB2。之后,存储器控制器110可用增量诸如一来增加索引i。 在步骤S23中,于当前时间区间诸如period(i)(例如:所述第三时间区间诸如period(3),或后续时间区间诸如period(4)、period(5)等中的一者)内,存储器控制器110可进行背景扫描以更新表TB1、TB2以及TB3。之后,存储器控制器110可用增量诸如一来增加索引i,接着,进入步骤S23以进行针对下一时间区间的操作。 由于表TB1、TB2以及TB3通过所述背景处理中的背景扫描来被连续地更新,且由于从表TB1、TB2以及TB3选取以供于读取目标数据(例如待读取的数据DATA(i))的期间来使用的表对应于所述目标数据的数据寿命,存储器控制器110可依据这个表来准确地设定读取电压,且因此可在大多数状况中通过N2处理来正确地取得所述目标数据的每一位。为了简明起见,本实施例与前述实施例相仿的内容在此不重复赘述。 为了更好的理解,所述方法可用图20所示的工作流程来说明,但本发明不限于此。依据某些实施例,一或多个步骤可于图20所示的工作流程中增加、删除或修改。 基于所述方法,本发明的设备(例如电子装置10、记忆装置100以及存储器控制器110)能增强整体效能以及避免相关技术中的问题,诸如位错误率提高、随机读取延迟增加、以及所述数据保留问题所衍生出的某些相关问题。 以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 以机器学习针对服务质量优化进行存取控制的方法和设备

- 针对机器学习算法进行算法参数调优的方法及系统