纳米线的选择性蚀刻

文献发布时间:2023-06-19 10:55:46

相关申请的交叉引用

本申请要求于2018年10月3日申请的美国专利申请No.62/740,806的优先权利益,其通过引用合并于此以用于所有目的。

技术领域

本公开内容涉及在半导体晶片上形成半导体装置的方法。更具体来说,本公开内容涉及纳米线的选择性蚀刻。

背景技术

在形成半导体装置时,可通过相对于硅(Si)而选择性地蚀刻硅锗(SiGe),以形成纳米线。也可以通过相对于SiGe而选择性地蚀刻Si,以形成纳米线。

发明内容

为了实现前述内容并且根据本公开的目的,提供了一种在堆叠件中相对于第二材料层而选择性蚀刻第一材料层的方法,其中所述第一材料层与所述第二材料层交替呈现。相对于所述第二材料层部分地蚀刻所述第一材料层。在所述堆叠件上选择性沉积沉积层,其中所述沉积层的覆盖在所述第二材料层上的部分比所述沉积层的覆盖在所述第一材料层上的部分厚。所述选择性沉积包含:提供第一反应物,其中所述第一反应物中的一些沉积在所述堆叠件上;清扫掉所述第一反应物中的一些,其中一些未沉积的第一反应物未被清扫掉;以及提供第二反应物,其中所述未沉积的第一反应物与所述第二反应物结合,其中所结合的所述未沉积的第一反应物与第二反应物便相对于所述第一材料层而选择性沉积在所述第二材料层上,且其中所述第二反应物中的一些与所述沉积的第一反应物反应,以形成所述沉积层的一部分。相对于所述第二材料层选择性地蚀刻所述第一材料层,以完全移除所述第一材料层,其中所述第二材料层受到所述沉积层保护。

在另一表现形式中,提供了一种在堆叠件中相对于硅而选择性地蚀刻硅锗的方法,其中两个硅层之间具有至少一个硅锗层。相对于所述硅而部分地蚀刻所述硅锗。以选择性沉积工艺来涂覆所述堆叠件,其中所述选择性沉积工艺使得在硅上比在硅锗上沉积更多。所述选择性沉积工艺包含:提供硅前体,其中所述硅前体中的一些沉积于所述堆叠件上;清扫掉所述硅前体中的一些,其中一些未沉积的硅前体保留;提供氧化气体,其中所述未沉积的硅前体与所述氧化气体结合,以形成未沉积的硅氧化物,其中所述未沉积的硅氧化物相对于所述硅锗而非保形且优先地沉积于硅上,且其中所述氧化气体中的一些氧化所述沉积的硅前体,以将所述沉积的硅前体转化成硅氧化物。相对于所述硅氧化物而选择性蚀刻所述硅锗,以完全移除所述硅锗。

在另一表现形式中,提供了一种在堆叠件中相对于硅锗而选择性地蚀刻硅的方法,其中两个硅锗层之间具有至少一个硅层。相对于所述硅锗而部分地蚀刻所述硅。以选择性沉积工艺来涂覆所述堆叠件,其中所述选择性沉积工艺使得在硅锗上比在硅上沉积更多。所述选择性沉积工艺包含:提供硅前体,其中所述硅前体中的一些沉积于所述堆叠件上;清扫掉所述硅前体中的一些,其中一些未沉积的硅前体保留;提供氧化气体,其中所述未沉积的硅前体与所述氧化气体结合,以形成未沉积的硅氧化物,其中所述未沉积的硅氧化物相对于所述硅而非保形且优先地沉积于所述硅锗上,且其中所述氧化气体中的一些氧化所述沉积的硅前体,以将所述沉积的硅前体转化成硅氧化物。相对于所述硅氧化物而选择性蚀刻所述硅,以完全移除所述硅。

本发明的这些特征和其它特征将在下面在本发明的具体实施方式中并结合以下附图进行更详细的描述。

附图说明

在附图中以示例而非限制的方式示出了本公开,并且附图中类似的附图标记表示相似的元件,其中:

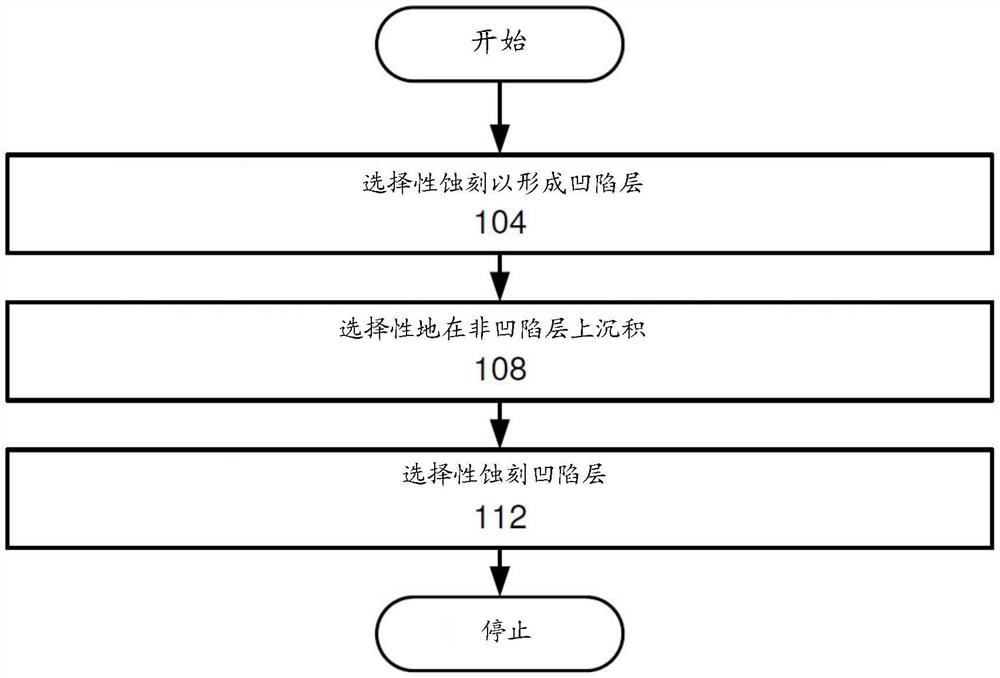

图1是一实施方案的高阶流程图;

图2A-D为根据一实施方案进行处理的堆叠件的横截面示意图;

图3为选择性蚀刻工艺的更详细的流程图;

图4为选择性沉积工艺的更详细的流程图;

图5A-D为根据另一实施方案进行处理的堆叠件的横截面示意图;

图6为可以用于一实施方案中的处理室的示意图;

图7是可用于实践一实施方案的计算机系统的示意图。

具体实施方式

现在将参考附图中所示的几个示例性的实施方案来详细描述本公开。在下面的描述中,阐述了许多具体细节以便提供对本公开内容的彻底理解。然而,对于本领域技术人员显而易见的是,本公开内容可以在没有这些具体细节中的一些或全部的情况下实施。在其他情况下,未详细描述公知的工艺步骤和/或结构,以免不必要地使本公开内容不清楚。

图1为一实施方案的高阶流程图。在该实施方案中,具有交替的第一材料层和第二材料层的堆叠件被选择性地蚀刻以形成第一材料凹陷层(步骤104)。在该示例中,第一材料是SiGe,而第二材料是Si。图2A为晶片上的堆叠件200的部分横截面示意图。在该实施方案中,堆叠件200包含第一Si层208,第一Si层208在第一SiGe层212的第一侧上与第一SiGe层212邻接。在第一SiGe层212的第二侧上,第一SiGe层212邻接第二Si层216。第一Si层208和第二Si层216位于第一SiGe层212上的相对两侧。第二SiGe层220则邻接于第二Si层216。第二Si层216位于第二SiGe层220的第一侧上。第一SiGe层212和第二SiGe层220位于第二Si层216的相对侧上。在第二SiGe层220的第二侧上,第二SiGe层220邻接于第三Si层224。第二Si层216和第三Si层224位于第二SiGe层220的相对侧上。

Si层208、216、224以及SiGe层212、220可以在电触点或其他结构(未显示)之间延伸并与其连接。如果SiGe层212、220被选择性地蚀刻掉,则Si层208、216、224便维持在电触点之间延伸并可以被使用作为纳米线。类似地,如果Si层208、216、224被选择性地蚀刻掉,如此SiGe层212、220便维持在电触点之间延伸且可以被使用作为纳米线。Si层208、216、224以及SiGe层212、220的尺寸非常的小,以至于蚀刻应具有高度选择性。Si层208、216、224以及SiGe层212、220可以是水平的层、或竖直的层或提供其它角度的层。

在示例性实施方案中,部分地选择性蚀刻堆叠件以形成凹陷层(步骤104)。在该实施方案中,第一SiGe层212和第二SiGe层220是相对于第一Si层208、第二Si层216和第三Si层224而被部分地选择性蚀刻。在该示例中,该蚀刻是使用循环性的蚀刻工艺的原子层蚀刻(ALE)。图3是使用ALE进行选择性部分蚀刻以形成凹陷层(步骤104)的更详细的流程图。ALE显示为至少一个循环。每一循环的ALE工艺包含氧化阶段(步骤312)、第一次清扫(步骤316)、蚀刻阶段(步骤320)以及第二次清扫(步骤324)。

在一示例中,在氧化阶段期间(步骤312),将堆叠件200暴露于氧化气体(例如O

图2B为堆叠件200在第一SiGe层212和第二SiGe层220相对于第一Si层208、第二Si层216和第三Si层224而被部分地选择性蚀刻之后的横截面示意图。所有的层均被蚀刻。然而,第一SiGe层212和第二SiGe层220比第一Si层208、第二Si层216和第三Si层224被蚀刻的更多。在该示例中,第一SiGe层212和第二SiGe层220相比于第一Si层208、第二Si层216和第三Si层224的蚀刻的比例为约9:1。层的蚀刻并未按比例绘制。如此产生了从第一Si层208过渡到第一SiGe层212的下陷228或凹陷。

选择性地在堆叠件200的非凹陷层上沉积层(步骤108)。图4为选择性沉积工艺(步骤108)的更详细的流程图。该选择性沉积工艺(步骤108)包含至少一个循环,其提供第一反应物(步骤412)、提供局部清扫(步骤414)、提供第二反应物(步骤416)、以及提供第二次清扫(步骤418)。

将第一反应物提供给堆叠件200(步骤412)。在该实施方案中,第一反应物是液态含硅前体。前体被气化并以蒸气形式输送到堆叠件200。供应蒸气给堆叠件200直至饱和,从而在堆叠件200上形成一前体层。在该示例中,前体具有通式为C(x)H(y)N(z)O(a)Si(b)的组成。在一些实施方案中,前体具有以下组成之一:N,N,N',N',N”,N”-六甲基硅烷三胺(C

一旦堆叠件200被投配前体,则前体蒸气的输送便停止。接着提供局部清扫步骤(步骤414)以清扫出残留在处理室中的一些未沉积的前体。N

提供第二反应物(步骤416)。在该实施方案中,所述提供第二反应物包含:向处理室提供含1000sccm至2000sccm的氧气(O

图2C为已沉积选择性沉积层232(步骤108)之后的堆叠件200的横截面图。选择性沉积层232在第一Si层208、第二Si层216和第三Si层224比在第一SiGe层212和第二SiGe层220上方形成较厚的层。沉积层232在堆叠件200上方形成涂层。不受理论的束缚,相信选择性沉积工艺(步骤108)在凹陷区域上沉积较少。一个原因可能是因为选择性沉积工艺(步骤108)因下陷228所产生的弯曲而在凹陷层上沉积较少。选择性沉积层232的厚度并没有按比例绘制,而是被放大以提供更佳清晰度及说明。

返回参照图1,凹陷层被选择性蚀刻(步骤112)。在该实施方案中,使用原子层蚀刻工艺而相对于第一Si层208、第二Si层216和第三Si层224选择性地蚀刻第一SiGe层212和第二SiGe层220。用于部分地选择性蚀刻堆叠件200以形成凹陷层(步骤104)的原子层蚀刻工艺配方可以用于选择性蚀刻凹陷层(步骤112)。在该示例中,覆盖Si层208、216、224的选择性沉积层232厚到足以保护这些层208、216、224在第一SiGe层212和第二SiGe层220被完全蚀刻掉之前不受到选择性蚀刻影响。

图2D为第一SiGe层212和第二SiGe层220被完全蚀刻掉之后的堆叠件200的横截面图。所产生的Si层208、216、224可被用作为水平纳米线而用于n型金属氧化物半导体(NMOS)装置。在这样的装置中,Si层208、216、224可悬于电触点结构之间。本实施方案提供大于20:1的蚀刻选择比,以相对于Si而蚀刻SiGe。此外,因为在处理期间的氧化作用或蚀刻而会损失小于

在多种实施方案中,蚀刻气体包含含氟成分。在多种实施方案中,含氟成分为氟碳化合物(例如CF

在一些实施方案中,选择性沉积层232被完全移除。可以在所得的Si层208、216、224周围沉积保护层。在一实施方案中,可以通过沉积含硅层的原子层沉积工艺来形成保护层。这种含硅层的示例可以是硅氧化物或硅氮化物层。保护层会防止所得的Si层208、216、224被氧化。所得的Si层208、216、224的氧化将进一步使硅层减少。结果,蚀刻的选择性甚至会更低。

在另一实施方案中,相对于SiGe层而选择性地蚀刻Si层。第一材料为Si,第二材料为SiGe。图5A为晶片上的堆叠件500的部分横截面示意图。在该实施方案中,堆叠件500包含与第一Si层512的第一侧上的第一Si层512邻接的第一SiGe层508。在第一Si层512的第二侧上,第一Si层512邻接第二SiGe层516。第一SiGe层508和第二SiGe层516位于第一Si层512的相对侧上。第二Si层520则邻接第二SiGe层516。第二SiGe层516位于第二Si层520的第一侧上。第一Si层512和第二Si层520位于第二SiGe层516的相对侧上。在第二Si层520的第二侧上,第二Si层520邻接第三SiGe层524。第二SiGe层516和第三SiGe层524系位于第二Si层520的相对侧上。SiGe层508、516、524以及Si层512、520可在电触点或其它结构(未显示)之间延伸并与其连接。

在一示例性实施方案中,堆叠件500被部分选择性地蚀刻以形成凹陷层(步骤104)。在该实施方案中,第一Si层512和第二Si层520是相对于第一SiGe层508、第二SiGe层516以及第三SiGe层524而被部分选择性地蚀刻。这种选择性蚀刻的示例性配方包含:提供含有10sccm的CF

图5B为堆叠件500在第一Si层512和第二Si层520相对于第一SiGe层508、第二SiGe层516以及第三SiGe层524而被部分选择性地蚀刻之后的横截面示意图。所有的层均被蚀刻。然而,第一Si层512和第二Si层520比第一SiGe层508、第二SiGe层516以及第三SiGe层524被蚀刻的更多。这样产生了从第一SiGe层508过渡到第一Si层512的下陷528或凹陷。

选择性地在堆叠件的非凹陷层上沉积层(步骤108)。图4为选择性沉积工艺(步骤108)的更详细的流程图。该选择性沉积工艺(步骤108)包含至少一个循环,其提供第一反应物(步骤412)、提供局部清扫(步骤414)、提供第二反应物(步骤416)、以及提供第二次清扫(步骤418)。

将第一反应物提供给堆叠件500(步骤412)。在该实施方案中,第一反应物是液态含硅前体。该液态含硅前体被气化并且以蒸气形式输送到堆叠件500。液态含硅前体投配至堆叠件500直至饱和,从而在堆叠件500上形成前体层。在该示例中,该前体包含双(叔丁基氨基)硅烷(C

一旦堆叠件500被投配前体,前体蒸气的输送就停止。接着提供局部清扫步骤(步骤414)以清扫出残留在处理室中的一些未沉积的前体。一些未沉积的前体可能保留在处理室中。

提供第二反应物(步骤416)。在该实施方案中,提供第二反应物包含:向处理室提供含1000sccm至2000sccm的氧气(O

图5C为已沉积选择性沉积层532之后的堆叠件500的横截面图。选择性沉积层532在第一SiGe层508、第二SiGe层516和第三SiGe层524上方比在第一Si层512和第二Si层520上方形成较厚的层。选择性沉积层532的厚度并没有按比例绘制,而是被放大以提供更佳的清晰度和说明。

返回参照图1,凹陷层被选择性蚀刻(步骤112)。在该实施方案中,相对于第一SiGe层508、第二SiGe层516和第三SiGe层524选择性地蚀刻第一Si层212和第二Si层220。这种选择性蚀刻的示例配方包含:提供含有10sccm的CF

图5D为第一Si层512和第二Si层520被完全蚀刻掉之后的堆叠件500的横截面图。所产生的SiGe层508、516、524可被用作为水平的纳米线以用于p型金属氧化物半导体(PMOS)装置。本实施方案提供大于20:1的蚀刻选择比,以相对于SiGe而蚀刻Si。此外,因为在处理期间的氧化作用或蚀刻而会损失小于

在相对于SiGe而选择性地蚀刻Si的另一实施方案中,可使用包含SF

图6为可在一实施方案中使用的处理室600的示意图。在一或多个实施方案中,处理室600在室壁612包围的反应器室610内包含提供一气体入口的喷头606以及静电卡盘(ESC)608。在反应器室610中,晶片614位于静电卡盘608上方。气体源616连接至远程等离子体产生器620。远程等离子体产生器620则通过喷头606而连接到反应器室610。射频(RF)源630提供一或多个频率(27兆赫(MHz)、13.56MHz、60MHz、2MHz、或400kHz)下的RF功率到远程等离子体产生器620、喷头606所提供的上部电极、或ESC 608所提供的下部电极。RF源630可以提供功率至线圈。射频功率用于产生电感耦合等离子体。卡盘温度控制器640控制冷却器644。冷却器644会冷却冷却剂648。冷却剂648被提供给卡盘冷却系统650。控制器635可控地连接到RF源630、排气泵652、卡盘温度控制器640与气体源616。

图7是示出适用于实现在实施方案中使用的控制器635的计算机系统700的高级框图。计算机系统700可以具有从集成电路、印刷电路板和小型手持设备到大型超计算机的许多物理形式。计算机系统700包括一个或多个处理器702,并且还可以包括电子显示装置704(用于显示图形、文本和其他数据)、主存储器706(例如随机存取存储器(RAM))、存储装置708(例如,硬盘驱动器)、可移动存储装置710(例如,光盘驱动器)、用户界面装置712(例如,键盘、触摸屏、小键盘、鼠标或其他指点装置等)和通信接口714(例如,无线网络接口)。通信接口714允许通过链路在计算机系统700和外部装置之间传送软件和数据。系统还可以包括与上述装置/模块连接的通信基础设施716(例如,通信总线、交叉连接杆或网络)。

经由通信接口714传送的信息可以呈信号的形式,例如电子信号、电磁信号、光学信号或能够经由通信链路由通信接口714接收的其它信号,通信链路携带信号并可以使用导线或电缆、光纤、电话线、蜂窝电话链路、射频链路和/或其他通信信道实现。利用这样的通信接口714,可以预期一个或多个处理器702可以在执行上述方法步骤的过程中从网络接收信息,或者可以向网络输出信息。此外,方法实施方案可以仅在处理器上执行,或者可以通过诸如因特网之类的网络与共享处理的一部分的远程处理器结合执行。

术语“非瞬态计算机可读介质”通常用于指代介质,诸如主存储器、辅助存储器、可移动存储装置、和存储装置,诸如硬盘、闪存存储器、磁盘驱动存储器、CD-ROM以及其他形式的持久性存储器,并且不应当被解释为涵盖瞬态标的物,如载波或信号。计算机代码的示例包括机器代码(诸如由编译器产生的)和含有由计算机使用解释器执行的较高级代码的文档。计算机可读介质也可以是由包含在载波中的计算机数据信号向处理器发送的计算机代码。

虽然已经根据几个示例性的实施方案描述了本发明,但是存在落在本发明的范围内的改变、修改、置换和各种替代等同方案。还应当注意,存在实现本公开的方法和装置的许多替代方式。因此,以下所附权利要求旨在被解释为包括落在本公开的真实精神和范围内的所有这样的改变、修改、置换和各种替代等同方案。

- 纳米线的选择性蚀刻

- 对包含银纳米线的基质的选择性蚀刻