一种恒定建立时间数字AGC环路的并行实现装置及方法

文献发布时间:2023-06-19 10:55:46

技术领域

本发明涉及电子信息技术领域,尤其涉及一种恒定建立时间数字AGC环路的并行实现装置及方法。

背景技术

现有的数字AGC处理过程主要有两类:第1类是将输出电平减去参考电平获得误差电压,然后对该误差信号进行积分产生控制电压,最后根据控制电压进行线性增量增益调整,使输出电压稳定在参考电平附近:第2类是根据恒定建立时间AGC环路基本原理,采用功率误差检测法获得误差电压,然后对该误差电压进行积分产生控制电压,最后根据控制电压进行线性对数增量增益调整,使输出电平稳定在参考电平附近。第1类实现方式简单,但其建立时间与输入信号电平相关;第2类建立时间恒定,但由于需要进行对数与指数运算,运算资源消耗较大。

第2类恒定建立时间数字AGC环路如图1所示,可见,VGA中含有指数运算,而ED中含有对数运算,均为非线性运算,运算量比较大,在FPGA中实现时,采用查表法实现成本比较高,而采用浮点实现无法处理高速数字信号数据流。上述AGC处理需FPGA使用浮点运算对高速数字信号数据流进行对数,指数等运算,资源消耗大,运算实现复杂。

发明内容

本发明要解决的技术问题就在于:针对现有技术存在的技术问题,本发明提供一种恒定建立时间数字AGC环路的并行实现装置及方法,通过并行处理在保证精度的同时达到降低时钟频率的要求。

一种恒定建立时间数字AGC环路的并行实现装置,包括:

串转并模块,用于将高速数字信号数据流按照预设的支路数量N分为N路并行的低速数字信号数据流;

AGC计算模块,用于计算低速数字信号数据流对应的增益因子;

AGC应用模块,用于根据增益因子对低速数字信号数据流进行AGC处理;

并转串模块,用于将经AGC处理后的低速数字信号数据流合并为经AGC处理后的高速数字信号数据流;

所述AGC计算模块、AGC应用模块分别与支路一一对应,所述串转并模块的输出端和AGC计算模块的输入端连接,所述AGC计算模块的输出端和对应的AGC应用模块的输入端连接,所述AGC应用模块的输出端和并转串模块的输入端连接。

本发明还提出一种恒定建立时间数字AGC环路的并行实现方法,应用于所述的恒定建立时间数字AGC环路的并行实现装置,包括以下步骤:

步骤1)串转并模块将输入的高速数字信号数据流a分为N路并行低速数字信号数据流b

步骤2)低速数字信号数据流b

步骤3)各AGC应用模块从对应的AGC计算模块获取增益因子和低速数字信号数据流,对低速数字信号数据流的数据根据对应的增益因子进行AGC处理得到AGC处理后的低速数字信号数据流c

步骤4)并转串模块将AGC处理后的低速数字信号数据流c

进一步的,步骤1)中,步骤1)中,低速数字信号数据流的函数表达式如下:

上式中,a

进一步的,步骤2)中AGC计算模块计算增益因子的步骤具体包括:采用功率误差检测法获得误差电压,然后对该误差电压进行积分产生控制电压,最后根据控制电压进行线性对数增量增益调整,使输出电平稳定在参考电平附近。

进一步的,步骤3)中AGC处理后的低速数字信号数据流的函数表达式如下:

c

上式中,k

与现有技术相比,本发明的优点在于:

本发明通过将高速数字信号数据流分为并行的低速数字信号数据流,使得增益计算过程中的时钟频率要求与现有技术要求相比大大降低,同时FPGA的时钟速率仍能满足所选FPGA器件的时序要求。

附图说明

图1为现有技术中恒定建立时间数字AGC环路示意图。

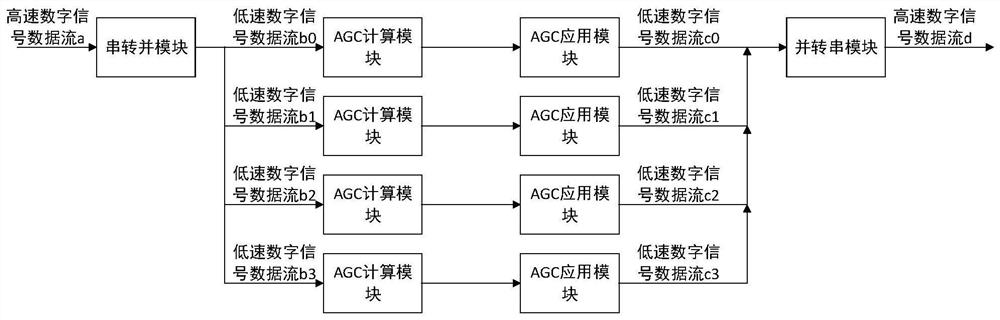

图2为本发明实施例的装置结构及工作流程示意图。

具体实施方式

以下结合说明书附图和具体优选的实施例对本发明作进一步描述,但并不因此而限制本发明的保护范围。

我们针对现有技术之缺失与不便之处,研究出一种恒定建立时间数字AGC环路的并行实现方案,如图2所示,本发明提出一种恒定建立时间数字AGC环路的并行实现装置,包括:

串转并模块,用于将高速数字信号数据流按照预设的支路数量N分为N路并行的低速数字信号数据流;

AGC计算模块,用于计算低速数字信号数据流对应的增益因子;

AGC应用模块,用于根据增益因子对低速数字信号数据流进行AGC处理;

并转串模块,用于将经AGC处理后的低速数字信号数据流合并为经AGC处理后的高速数字信号数据流;

所述AGC计算模块、AGC应用模块分别与支路一一对应,所述串转并模块的输出端和AGC计算模块的输入端连接,所述AGC计算模块的输出端和对应的AGC应用模块的输入端连接,所述AGC应用模块的输出端和并转串模块的输入端连接。

本实施例中,N=4,通过上述结构,本实施例将高速数字信号数据流按照支路数量分为4路并行的低速数字信号数据流,每一支路的信号的AGC处理相比于原始信号进行AGC处理在增益计算过程中的时钟频率要求大大降低,克服现有技术对FPGA时钟频率要求高、对数,指数运算对浮点计算资源消耗大的不足,同时对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以对恒定建立时间数字AGC环路的并行实现装置做出若干变形和改进,例如,AGC计算模块、AGC应用模块分别为8个或16个,从而使得恒定建立时间数字AGC环路8倍并行或者16路并行,只需相应的改变串转并模块和并转串模块的串并转换路数即可。

本实施例还提出一种恒定建立时间数字AGC环路的并行实现方法,应用于所述的恒定建立时间数字AGC环路的并行实现装置,包括以下步骤:

步骤1)串转并模块将输入的高速数字信号数据流a分为N路并行低速数字信号数据流b

数字信号数据流可以视为数字信号数据的集合,集合中的元素为数字信号数据,因此有:

a={a

在相同时间内,低速数字信号数据流b

上式中,a

通过步骤1),每一支路的数字信号数据流b

步骤2)低速数字信号数据流b

对于每条支路,计算增益因子采用现有方法进行计算,即本实施例的步骤2)中AGC计算模块计算增益因子的步骤具体包括:采用功率误差检测法获得误差电压,然后对该误差电压进行积分产生控制电压,最后根据控制电压进行线性对数增量增益调整,使输出电平稳定在参考电平附近,最终得到增益因子与数字信号数据流的函数关系表达式如下:

k

上式中,k

步骤3)各AGC应用模块从对应的AGC计算模块获取增益因子和低速数字信号数据流,对低速数字信号数据流的数据根据对应的增益因子进行AGC处理得到AGC处理后的低速数字信号数据流c

AGC处理后的低速数字信号数据流的函数表达式如下:

c

上式中,k

步骤4)并转串模块将AGC处理后的低速数字信号数据流c

高速数字信号数据流d中的数据即为低速数字信号数据流c

d={c

由式(1)和(2)可得:

a={b

由式(4)和(5)可得:

d={b

从式(6)和(7)可知,高速数字信号数据流d中的数据也就是高速数字信号数据流a中所有数字信号数据经过AGC处理后的结果。

从上述步骤可以看出,本实施例的方法通过恒定建立时间数字AGC环路的并行处理,通过串并转换将高速数字信号数据流分割为并行的低速数字信号数据流,对每个支路的低速数字信号数据流分别进行AGC处理,然后将处理结果进行合并最终得到AGC处理后的高速数字信号数据流,对于每一支路的低速数字信号数据流,由于相比原始高速数字信号数据流单位时间内的数据量大大减少,因此进行AGC处理在增益计算过程中的时钟频率要求大大降低,使得最终结果在保证精度的同时达到降低时钟频率的要求。

上述只是本发明的较佳实施例,并非对本发明作任何形式上的限制。虽然本发明已以较佳实施例揭露如上,然而并非用以限定本发明。因此,凡是未脱离本发明技术方案的内容,依据本发明技术实质对以上实施例所做的任何简单修改、等同变化及修饰,均应落在本发明技术方案保护的范围内。

- 一种恒定建立时间数字AGC环路的并行实现装置及方法

- 一种环路滤波的并行实现方法