采样开关电路

文献发布时间:2023-06-19 12:14:58

技术领域

本发明涉及可以被称为采样电路系统的采样开关电路和电路系统。根据本发明的采样开关电路可以被称为采样保持电路或采样保持开关电路。

背景技术

一般而言,已知电压模式采样和电流模式采样,并且采样保持电路可以被认为是电压模式采样电路的示例。现在将以介绍的方式探索先前考虑的自举方法(bootstrappingmethod)。

在典型的电压模式采样器中,采样晶体管例如场效应晶体管(FET)充当简单的开关,该开关在采样(跟踪)阶段期间导通(ON)并且在保持阶段期间关断(OFF)。器件(采样晶体管)的导通电阻取决于输入电压(例如,在FET的情况下,为栅极-源极电压),这转而产生谐波失真,即与输入相关的失真。在电压模式采样器位于模数转换器(ADC)的前端的情况下,谐波失真可能限制ADC的动态范围。

自举电路可以用于(在采样阶段或跟踪阶段期间)在开关的栅极-源极上提供或施加恒定电压,该恒定电压至少在理论上与输入信号无关。这使采样开关的与输入相关的导通电阻变化最小化。

图1是采样开关电路1的示意图,用于全面理解自举概念。输入信号V

通常,如所示出的,V

电路1的操作如下。当CLK为高(并且-CLK为低)时,采样开关M

图2示出了先前考虑的自举电路10,作为电路1的详细实现,在自举电路10中电压源V

电路10的操作如下。

当采样时钟为高(即,CLK=高)时,晶体管M

当采样时钟为低(即,CLK=低)时,晶体管M

此外,在图2中,所有开关(晶体管)的端子两端的电压始终等于或小于供电电压V

为了更好地理解图2中的自举电路10的速度,在预充电阶段和跟踪模式下对该电路进行了更详细的分析。

图3是电路10的示意图,在该示意图中,某些元件被突出显示(未以虚线形式示出)而另一些元件未被突出显示(以虚线形式示出)以帮助理解预充电/保持阶段(当CLK=高时)。

如之前所描述的,在该阶段期间,电容器C

首先,以以下时间常数将图3中的节点G放电至地:

T

然后,以以下时间常数对电容器C

T

其中,R

C

其它晶体管对M

T

通常,节点G的放电比预充电发生得快得多(由于开关M

T

图4A和图4B是电路10的示意图,在该示意图中某些元件被突出显示(未以虚线示出)而另一些元件未被突出显示(以虚线示出)以帮助理解跟踪阶段(当CLK=低)。

当时钟信号CLK变低时,晶体管M

T

其中,R

C

接下来,并且当M

T

其中,R

图4A和图4B分别示出了在时间常数T

总跟踪时间常数可以被计算为:

T

因此,可以如下使用上面计算的时间常数的总和来计算最大采样时钟频率:

ω

由于C

ω

实际上,取决于所需分辨率,需要几个时间常数来达到适当的建立时间。因此,最大采样频率通常是(11)中估计的f

要注意的是,电路10从图4A中示出的状态向图4B中示出的状态的转换包括如下时间间隔:在该时间间隔中,节点G上的电压升高到M

发明人还考虑如上所述的图2中的电路10关于超高采样频率的操作。特别地,在实践中,电路10具有限制其最大频率操作的如下三个主要问题。

首先,存在相对大的电容器C

其次,由于大的晶体管数量(如图2所示)会产生大量寄生电容,因此在超高速采样频率处,晶体管的数量非常重要。在图2中,针对采样开关M

第三,当时钟信号改变其状态(从高到低或从低到高)时,晶体管M

因此,考虑到上述内容,在将采样频率朝向较高频率推动时,开始出现三种破坏性/失效机制,这些破坏性/失效机制会如下破坏电路10的高频操作。

首先,由于预充电时间(参见等式(2))的相对大的时间常数,因此在高频下电容器C

其次,存储在电容器C

第三种失效机制是由于节点Z上的电压而引起的。如前所述,在跟踪阶段开始时,节点Z上的电压通过M

电压模式ADC(具有这样的采样开关电路作为电压模式采样器前端)通常使用自举技术以增强转换器的动态范围。对于网络应用,由于该技术领域中的应用的低分辨率性质,很可能可以避免这种情况。然而,对于需要高速和高分辨率的5G应用,如上所述,当前的自举技术似乎不切实际。

期望解决以上问题中的一个或更多个问题,并且特别地,期望提供例如在较高操作速度下具有改善的性能的采样开关电路。期望提供改进的可以用作ADC的电压模式采样器前端的采样开关电路,例如用于直接RF应用中。

发明内容

根据本发明的第一方面的实施方式,提供了一种采样开关电路,包括:输入节点,其被连接成接收待被采样的输入电压信号;采样晶体管,其包括栅极端子、源极端子和漏极端子,源极端子连接至输入节点;分压器电路,其连接至输入节点和跟踪-控制节点,以在跟踪-控制节点处提供依赖于输入电压信号的跟踪-控制电压信号;保持-控制节点,其被连接成接收保持-控制电压信号;输出节点,其连接至采样晶体管的漏极端子;以及切换电路系统,其被配置成根据时钟信号将采样晶体管的栅极端子连接至跟踪-控制节点或保持-控制节点。

这样的采样开关电路可以被称为例如采样电路、采样器电路、采样器前端电路、ADC前端电路、采样保持电路或采样保持开关电路。分压器电路基于输入电压信号至少在跟踪-控制节点处提供跟踪-控制电压信号,使得该跟踪-控制电压信号可用于控制采样晶体管(例如,在不需要对电容器例如图2电路系统中的C

将理解,本文的连接可以是电路连接,例如导电连接(并且可以包括DC(直流)连接和/或经由电容器的AC(交流)连接)。节点处所提供的电压可以被施加于该节点或者在该节点处生成。

分压器电路可以被配置成使得:当采样晶体管的栅极端子连接至跟踪-控制节点时,采样晶体管导通并且采样晶体管的漏极端子处和/或输出节点处的电压跟踪采样晶体管的源极端子处的电压。

采样开关电路可以包括采样电容器,该采样电容器连接至输出节点,可选地连接在输出节点与接地供电节点之间。这样的采样电容器可以用于保持输出节点处的电压电平。当采样晶体管的栅极端子连接至保持-控制节点时,采样晶体管可以关断,并且可以至少暂时维持或保持采样晶体管的漏极端子处和/或输出节点处的电压。

分压器电路可以是以下至少之一:阻抗电路;电阻器电路;电阻器网络;无源电路;以及线性电路。电阻器电路/电阻器网络可以包括电阻器(除了其他部件之外)或者其部件可以全部是电阻器。

跟踪-控制电压信号可以具有至少由输入电压信号限定的跟踪-控制AC分量和至少由分压器电路限定的跟踪-控制DC分量。分压器电路可以被配置成维持跟踪-控制节点处的跟踪-控制电压信号,其中可选地将跟踪-控制AC分量维持成至少由输入电压信号限定并且将跟踪-控制DC分量维持成至少由分压器电路限定,可选地将跟踪-控制电压信号维持为连续信号并且可选地与时钟信号无关。

分压器电路可以连接至采样节点以在采样节点处提供采样电压信号,该采样电压信号具有至少由输入电压信号限定的采样AC分量和至少由分压器电路限定的采样DC分量,采样晶体管的源极端子连接至采样节点并且经由采样节点连接至输入节点。采样电压信号可以代表输入电压信号,例如(例如,直接地)与输入电压信号成比例。分压器电路可以被配置成维持采样节点处的采样电压信号,可选地将采样AC分量维持成至少由输入电压信号限定并且将采样DC分量维持成至少由分压器电路限定,可选地将采样电压信号维持为连续信号并且可选地与时钟信号无关。

分压器电路可以被配置成使得跟踪-控制DC分量和采样DC分量在电压电平上彼此不同。跟踪-控制DC分量的电压电平与采样DC分量的电压电平之间的差可以大于或等于采样晶体管的阈值电压。当栅极端子连接至跟踪-控制节点时,跟踪-控制DC分量的电压电平与采样DC分量的电压电平之间的差可以足以使采样晶体管导通,可选地完全导通。

分压器电路可以连接至第一参考节点和第二参考节点,第一参考节点被连接成接收具有第一参考DC分量的第一参考电压信号,并且第二参考节点被连接成接收具有第二参考DC分量的第二参考电压信号。第一参考DC分量和第二参考DC分量可以被配置成使跟踪-控制DC分量的电压电平与采样DC分量的电压电平之间的差大于或等于采样晶体管的阈值电压。

第一参考电压信号和/或第二参考电压信号可以是DC电压信号。第一参考节点可以连接至电压供电节点,该电压供电节点例如具有不同于(高于)V

分压器可以包括:第一阻抗,其连接在输入节点与跟踪-控制节点之间;第二阻抗,其连接在跟踪-控制节点与第一参考节点之间;第三阻抗,其连接在输入节点与采样节点之间;以及第四阻抗,其连接在采样节点与第二参考节点之间。

第一阻抗至第四阻抗可以由电阻器组成、可以是电阻器或者可以包括电阻器。

第一阻抗可以被实现为电阻器或电阻器与电容器的串联连接,或者被实现为电阻器与电容器的并联连接,或者被实现为阻抗的并联组合与电容器的并联连接,阻抗的并联组合包括电阻器与电容器的并联连接。

第二阻抗可以被实现为电阻器,或者被实现为电阻器与电感器的串联连接。

第三阻抗可以被实现为电阻器,或者被实现为电阻器与电容器的并联连接。

第四阻抗可以被实现为电阻器,或者被实现为阻抗的并联组合与电阻器的串联连接,该阻抗的并联组合包括电阻器与电容器的并联连接,可选地,其中,所述阻抗的并联组合连接至第二参考节点。

保持-控制电压信号可以具有保持-控制DC分量,并且保持-控制DC分量的电压电平与采样DC分量的电压电平之间的差可以小于采样晶体管的阈值电压。当栅极端子连接至保持-控制节点时,保持-控制DC分量的电压电平与采样DC分量的电压电平之间的差可以足以使采样晶体管关断。保持-控制电压信号可以是DC电压信号。保持-控制电压信号可以是接地供电信号。保持-控制节点可以连接至电压供电节点例如接地供电节点。

切换电路系统可以包括:第一开关,其连接在采样晶体管的栅极端子与跟踪-控制节点之间;以及第二开关,其连接在采样晶体管的栅极端子与保持-控制节点之间。第一开关和第二开关可以被连接成由所述时钟信号控制,使得在这两个开关中的一个开关导通时另一个开关关断。第一开关和第二开关可以由晶体管实现。

第一开关可以和在采样晶体管的栅极端子与跟踪-控制节点之间的电阻串联连接,可选地,其中,该电阻由一个或更多个晶体管实现。第二开关可以和在采样晶体管的栅极端子与保持-控制节点之间的电阻串联连接,可选地,其中,该电阻由一个或更多个晶体管实现。

采样开关电路可以被配置成具有多个通道(每个通道可以对应于多相时钟信号的不同相)。每个通道可以包括其自己的采样晶体管、输出节点、切换电路系统和时钟信号。对于每个通道,采样晶体管的源极端子可以连接至输入节点,输出节点可以连接至采样晶体管的漏极端子,并且切换电路系统可以被配置成根据时钟信号将采样晶体管的栅极端子连接至跟踪-控制节点或保持-控制节点。

根据本发明第二方面的实施方式,提供了一种采样开关电路,该采样开关电路包括:采样开关晶体管,其连接在输入节点与输出节点之间;采样电容器,其连接在输出节点与接地节点之间;第一晶体管,其连接在采样开关晶体管的栅极与中间节点之间;第二晶体管,其被设置在采样开关晶体管的栅极与接地节点之间;以及电阻器电路,其连接在输入节点与参考电压节点之间,并且被配置成基于输入电压和中间节点处的参考电压来生成用于驱动采样开关晶体管的电压,其中,第一晶体管的栅极和第二晶体管的栅极分别连接至时钟输入节点,使得第一晶体管和第二晶体管交替导通和关断。

根据本发明的第三方面的实施方式,提供了一种模数转换器,该模数转换器包括根据本发明的前述第一方面或第二方面的采样开关电路。

根据本发明的第四方面的实施方式,提供了一种集成电路系统,例如IC(集成电路)芯片,该集成电路系统包括根据本发明的前述第一方面或第二方面的采样开关电路或根据本发明的前述第三方面的模数转换器。

附图说明

现在将通过示例的方式参照附图,在附图中:

图1如上所述是先前考虑的采样开关电路的示意图;

图2示出了先前考虑的自举电路作为图1电路的详细实现;

图3是图2电路的用于理解预充电阶段/保持阶段的示意图;

图4A和图4B是图2电路的用于理解跟踪阶段的示意图;

图5是体现本发明的采样开关电路的示意图;

图6示出了表示图5中的电路的节点A上的电压的简化电路模型;

图7是与图6等效但指示出AC(交流)电力流动和DC(直流)电力流动的示意图;

图8示出了表示图5中的电路的节点B上的电压的简化电路模型;

图9是表示图5的着重于其分压器电路的简化电路模型的示意图;

图10是与图9类似但明确示出寄生电容的示意图;

图11是与图5等效但指示相应电力流动的示意图;

图12和图13是有助于更好地理解图5的电路的等效电路的示意图;

图14是体现本发明的采样开关电路的示意图;

图15是体现本发明的采样开关电路的示意图;

图16是体现本发明的采样开关电路的示意图;

图17是体现本发明的采样开关电路的示意图;

图18是体现本发明的采样开关电路的示意图;

图19是体现本发明的采样开关电路的示意图;

图20是表示用于将图2的电路的操作与图18的电路的操作进行比较的测试台的示意图;

图21是示出图2的电路和图18的电路的导通电阻变化量的图;

图22是示出图2的电路和图18的电路的采样开关的有效带宽(EBW)的图;

图23是用于仿真的体现本发明的采样开关电路的示意图;

图24是与图23相对应的时钟信号的示意图;

图25至图27分别针对正轨(positive rail)电路和负轨(negative rail)电路两者示出了节点A(图25)和节点G(图26)上的波形,以及与图23电路的仿真有关的所有四个相的输出(图27);

图28示出了与图27相对应的FFT频谱;

图29是体现本发明的ADC的示意图;以及

图30是体现本发明的集成电路系统的示意图。

具体实施方式

本发明的实施方式试图解决以上问题。

特别地,通过概述并回顾对图2至图4的讨论,在实施方式中,通过从切换路径去除大电容器C

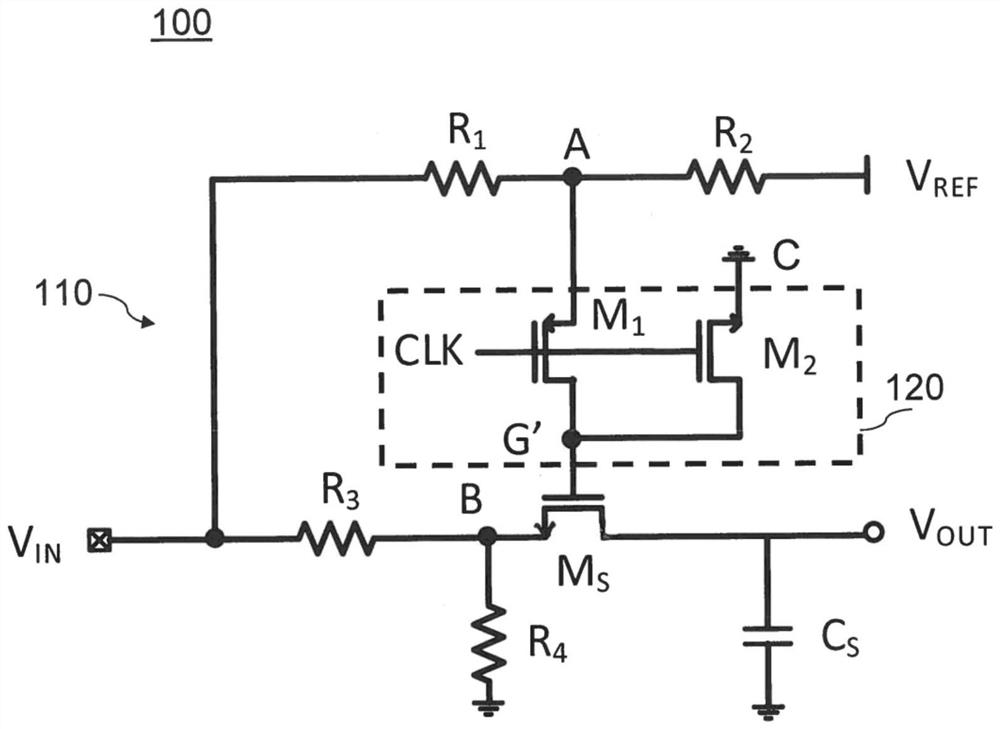

图5是体现本发明的采样开关电路100的示意图。采样开关电路100可以被称为例如采样电路、采样器电路、采样器前端电路、ADC前端电路、采样保持电路或采样保持开关电路,并且本公开内容将相应地被理解。同样体现本发明的采样开关电路100的变型将稍后在下文中考虑。与采样开关电路10相比,消除了对相当大的电容器(即,C

采样开关电路100包括输入节点(标为V

输入节点被连接成接收待被采样的输入电压信号V

在图5中,分压器电路110包括电阻器R

因此,分压器电路110连接至跟踪-控制节点(节点A)以提供跟踪-控制电压信号,跟踪-控制电压信号具有至少由输入电压信号V

切换电路系统120包括晶体管M

晶体管M

输出节点连接至采样晶体管M

为了更好地理解电路100的操作,将更详细地考虑节点A和节点B处的电压。

首先,将考虑节点A上的电压(跟踪-控制电压信号)。图6示出了表示电路100的节点A上的电压的简化电路模型。在图6中,R

C’

乍看之下,如在(12)中所见,节点G'上的电容(C'

等效电阻R

R

其中,f

R

其中,>>是“大得多”的符号,并且||意指并联。

等式(14)证实了图5中电路100的方面。使电阻器R

根据图6的电路,我们得出:

V

其中,g

∑g

可以在如图8所示的等效电路中计算图5中节点B上的电压(采样电压信号),其中,R

根据图8,节点B处的电压可以估算为:

V

其中,g

∑g

在跟踪模式或跟踪阶段期间,采样开关M

V

利用与自举开关相同的构思,即,为了具有线性采样开关M

g

在这种情况下,(19)中的栅极-源极电压被减小至(至少近似):

V

该栅极-源极电压是恒定的并且与输入信号V

应当注意,结合图5至图8,假定输入信号V

从输入阻抗匹配的角度来看,图5的电路100也具有优点。

特别地,被实现为如先前说明的电阻器网络或电阻器电路的分压器电路100提供了可以被用于高速应用中的阻抗匹配的等效输入阻抗。参照图9,图9是示出表示电路100的着重于分压器电路110的简化电路模型的示意图。

在输入节点处看到的等效输入阻抗Z

Z

随着输入频率(f

参考图10,图10是与图9类似但明确示出节点B处的寄生电容C

Z

为了在示例设计方案中考虑反射而又不失去任何通用性,将在示例应用中假定针对时钟分支设计的电阻(即,R

(R

这意味着

Z

在低输入频率处,(25)中的输入阻抗减小为:

Z

在高输入频率处:

Z

在低输入频率处,示例应用中将(26)中的输入阻抗设计为等于特性阻抗Z

Z

在这种情况下,在高输入频率处,反射度量/反射系数或S参数S

S

将(27)和(28)代入(29)得出:

S

R

在(30)中计算的S

与图2的自举电路10相比,现在将考虑电路100的速度。在电路100中,时钟路径中的主电容器是采样开关M

在跟踪模式/跟踪阶段期间,图5中的M

T

类似地,在保持阶段(不存在预充电阶段),可以根据图13计算等效RC时间常数。

T

与(10)相似,最大采样频率可以被计算为:

ω

将(31)和(32)代入(33)得到:

ω

为了对两种结构的速度进行比较,将(34)除以(11)得出:

f

根据图7和图11,电阻器R

f

其中,假定所有器件的导通电阻也都等于R

期望对于通过采样开关M

V

在图14中示意性示出的作为图5的电路100的变型的另一电路布置100A中,如所示出的,可以通过作为第二参考信号施加的参考电压V

在如图15中示意性示出的作为电路布置100A的替选方案并且是图5的电路100的变型的另一电路布置100B中,可以如图15所示在图5的电路100的结构中(在R

图16是另一电路布置100C的示意图,电路布置100C被配置成包括针对时间交错操作而布置的多个通道。应当理解,这样的配置可以用作时间交错ADC的前端。

为简单起见,图5的电路100已经被用作布置100C的基础,其中,输入节点、节点A和节点B、第一参考信号节点和第二参考信号节点以及分压器电路110是不同通道共用的(即,在不同通道之间共享)。

然后,每个通道都有其自己的晶体管M

应当理解,如果时钟信号CLK

当然,尽管将图5的电路100用作布置100C的基础,但应理解,本文所公开的任何其他单通道布置(例如,以上描述的100A或100B,或者下文将描述的100D、100E或100F)均可以以类似的方式用作多通道布置的基础。

为了利用采样开关M

V

这意味着参考电压V

V

将(38)代入(15)得出:

V

这意味着节点A上的电压将超过核心供电电压。在这种情况下,图5中的器件M

图17是作为图5的电路100的变型的另一电路布置100D的示意图,电路布置100D被配置成解决该过大应力问题。添加晶体管M

图17中的电路100D也可以用在与如前所述的图16中示出的时间交错结构等效的时间交错结构中。

应当注意,在CLK为低时,图17中的传输门(即,晶体管M

图18是作为图5的电路100的变型的另一电路装置100E的示意图,电路装置100E被配置作为电路布置100D的简化版本。在图18的电路100E中,晶体管M

图18中的电路100E也可以用在与如前面提及的图16中示出的时间交错结构等效的时间交错结构中。

在高输入频率处,传递通过采样开关(通过图18中的节点B)以及传递通过时钟路径(通过节点A)的输入信号功率的量减少。这限制了采样电路100E的带宽并且最终限制包括采样电路100E的ADC的带宽。

图19是作为图17的电路100D的变型的另一电路布置100F的示意图,电路布置100F被配置用于补偿该带宽限制。如所示出的,已经将两个电容器(C

在这种情况下,可以通过如下修改(15)来计算节点A(在s域中)上的电压:

V

另一方面,可以通过如下修改(17)来计算图19中节点B(在s域中)上的电压:

V

其中,Σg

在高输入频率(即s=∞)处,等式(41)和(42)被简化为:

V

将(43)中的V

G=(g

该增益量充当均衡器,该均衡器可以增强图19中的采样器电路100F的带宽并且因此增强包括采样器电路100E的ADC的带宽。

当然,可以以类似的方式在电路100和电路100A至100E(或下面描述的100G)的任何一个中采用C

取决于实际实现中的应用和采样开关电路所需要的规格,可能需要将参考电压V

图20是表示用于将电路100E(图18)与电路10(图2)的操作进行比较的测试台的示意图。因此,在测试中设置了“时钟方案”,以7nM FinFet CMOS技术对电路100E和电路10的操作进行仿真。测量采样开关M

图21是针对两种时钟方法(即,电路10和电路100E)示出导通电阻变化量(由于输入电压摆幅而引起)相对于采样时钟频率的图。如图20所示,时钟频率为f

值得一提的是,图21中示出的变化是针对不同采样频率相对于输入电压而言的。较大的变化会导致较高的谐波失真并最终导致较低的有效位数(ENOB)、无杂散动态范围(SFDR),并且总体上会降低包含相关电路的ADC的动态性能。

图22是示出采样开关M

FBW=(1/2π)×1/(R

其中,R

如图22的结果中可以看出的,与图2的技术相比,所提议的切换方法(图18)示出了更好的有效带宽。值得一提的是,取决于所需的分辨率(和ENOB),有效带宽(其代表开关M

图23是另一电路布置100G的示意图,电路布置100G与图16的电路布置等效,但是基于图18而不是图5的电路,被用于进一步仿真。电路100G是图18中的配置的四相结构(例如,作为时间交织采样器前端结构使用),其中,<3:0>表示并联连接的通道子电路中的四个分量的阵列。与图16中一样,输入节点、节点A和节点B、第一参考信号节点和第二参考信号节点以及分压器电路110对于不同通道是共用的(即,在不同通道之间共享)。

在图23中,CLK<3:0>和CLKN<3:0>是四相时钟,其中,CLKN<3:0>的占空比为0.25,并且CLK<3:0>的占空比为0.75。时钟信号CLKN<3:0>在图24中示出(CLK<3:0>与其相同但是进行了反向)。在这种情况下,V

图25至图27分别针对正轨电路和负轨电路示出了节点A(图25)和节点G(图26)上的波形以及所有四个相的输出V

将图27中的四个相输出信号重组为单个信号并计算其FFT频谱,并且在图28中示出。在该示例仿真中,发现ENOB约为10位,这表明了所提出的技术(图18)在高采样频率处的有效性。

总之,本文所公开的实施方式使得能够实现:从开关路径中去除大电容C

去除预充电阶段是有利的。在跟踪阶段使用的电压V

如上所述,体现本发明的采样开关电路可以实现为ADC的一部分,例如作为ADC的前端,以便以如前所述的时钟信号CLK所定义的采样率来生成输入信号V

本文所公开的任何电路系统可以被实现为集成电路系统或集成电路,例如,被实现为诸如倒装芯片的IC芯片(或作为其一部分)。图30是体现本发明的集成电路系统2000的示意图。集成电路系统2000可以包括ADC 1000和/或本文所公开的采样开关电路100以及采样开关电路100A至100G中的任何采样开关电路,为简单起见在图30中指示为100。

集成电路系统2000可以表示IC芯片的一些或全部。本发明扩展到如上所述的集成电路系统和IC芯片、包括这样的IC芯片的电路板、以及包括这样的电路板的通信网络(例如,互联网光纤网络和无线网络)和这种网络的网络设备。

在所附权利要求的精神和范围内,可以根据以上公开内容以许多不同的方式来体现本发明。

- 双路正端电流采样模块、采样电路、开关电路及采样方法

- 一种电流采样电路、一种开关电路及电流采样方法