一种基于SOC硬件标识码的嵌入式软件加密设计方法

文献发布时间:2023-06-19 12:10:19

技术领域

本发明涉及一种基于SOC硬件标识码的嵌入式软件加密设计方法。

背景技术

随着通信系统不断发展,数据存储量在嵌入式系统中大幅增加,大量敏感信息存储在嵌入式系统,如何确保这些敏感信息不被他人窃取成了当前一个重要问题。

当前,很多在嵌入式平台上实现的功能都未进行加密设计或者仅仅在实现功能的文件里面加入简单的加密算法,其他人很容易通过反向手段获取该功能文件用于其他嵌入式平台上,造成个人知识产权损失,严重的可能导致重大的泄密事故,因此仅仅通过简单软件加密或者不加密的方式无法满足现代嵌入式平台设计需求。

现场可编程逻辑门阵列(FPGA)与ARM结合在一起,可以组成一个片上系统(SOC),SOC作为新一代的嵌入式平台被大量广泛的使用;SOC中的FPGA可以根据用户需求进行反复编程,而且具有高速并行处理能力,与ARM(ARM处理器是英国Acorn有限公司设计的低功耗成本的第一款RISC微处理器。全称为Advanced RISC Machine)结合在一起,实现对运行在该平台的数据(实现某种功能、算法)进行加解密,从而保护个人的隐私或知识产权。

发明内容

发明目的:针对现有技术的不足,本发明提供了一种基于片上系统SOC硬件标识码的嵌入式软件加密设计方法,其具有FPGA+ARM的结构,能够实现对运行在该平台的数据进行高速处理并实现加解密。所述方法包括一片现场可编程逻辑门阵列FPGA和两个ARM以及外围硬件电路;

所述FPGA对自身携带的硬件标识码Device DNA(设备身份标识)以及由ARM读取外围电路中FLASH硬件标识码这两种硬件标识码进行自定义加密算法处理得到一串密钥,从而对运行在该嵌入式平台数据进行加密处理;上位机通过网口或者串口与ARM通信,上位机将事先准备好的正确的密钥进行处理,生成一种特定格式(例如XX.enc)的文件后,将所述特定格式的文件上传到ARM里面,两个ARM相互协同工作,提前做好解密算法(该算法为前续自定义加密算法的逆向算法),只对所述特定格式的文件进行校验与解密,得到所述特定格式文件进行解密后的密钥,ARM对FPGA产生的密钥与所述特定格式文件进行解密后的密钥进行对比,如果对比正确,则ARM给FPGA一个正确的反馈信号,从而对数据进行正确输出,否则,ARM给FPGA一个错误的反馈信号,从而使数据无法正确输出。

进一步地,所述FPGA自带一个Device DNA,Device DNA由57位二进制编码组成,FPGA根据Device DNA进行加密算法得到一串密钥。

进一步地,所述FPGA自带一个Device DNA,Device DNA由57位二进制编码组成,由于同一生产的批次中,超过32片FPGA后,Device DNA就会出现重复,FPGA根据Device DNA与其他硬件标识码(例如FLASH的硬件标识码)进行组合加密算法得到一种密钥,使密钥具有唯一性。

有益效果:本发明对数据进行加解密,确保形成一个安全的运行环境,确保个人的隐私安全或者保护个人知识产权不被盗用;另外不需要单独的保密模块进行加解密,降低加解密成本。

附图说明

下面结合附图和具体实施方式对本发明做更进一步的具体说明,本发明的上述或其他方面的优点将会变得更加清楚。

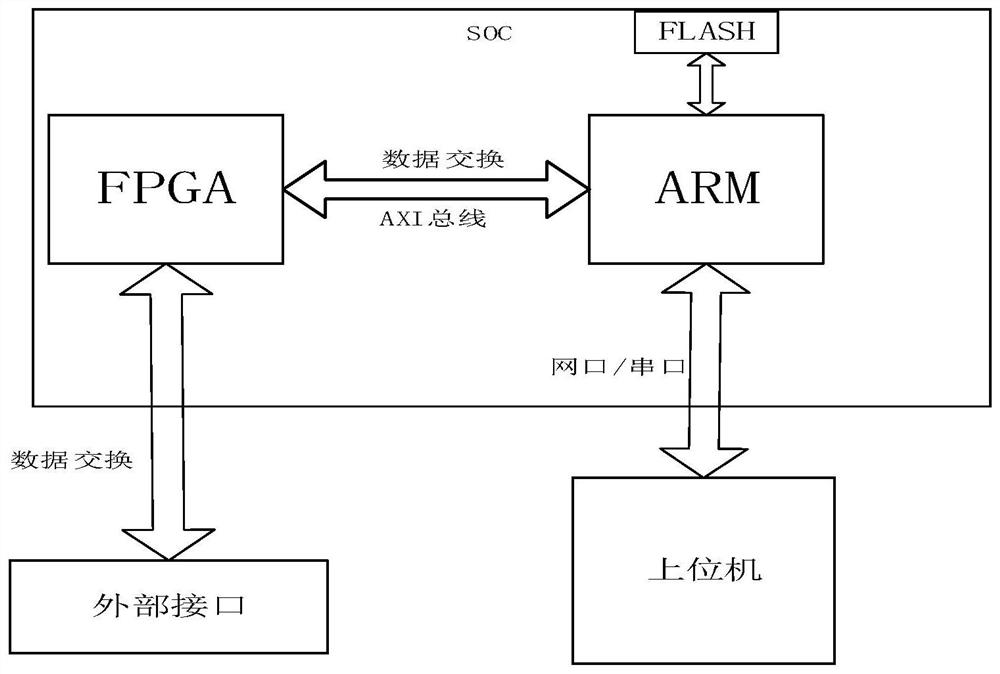

图1是本发明架构图。

具体实施方式

下面结合附图及实施例对本发明做进一步说明。

本发明提供了一种基于SOC硬件标识码的嵌入式软件加密设计方法,选用工业级的ZYNQ-7100芯片;FPGA通过对硬件标识码进行加密算法处理得到一串密钥,从而对运行在该平台数据进行高速加密处理;上位机通过网口或者串口与ARM通信,上位机利用加密工具将正确的密钥进行处理,生成一种特定格式的文件后,将这种特定格式的文件上传到ARM里面,ARM提前做好解密算法,只对该格式的文件进行校验与解密,把特定文件进行解密后得到正确的密钥,ARM对FPGA产生的密钥与上位机输入的特定格式文件进行解密后的密钥进行对比,对比正确后对其进行解密,从而实现对数据的加解密,具体原理框图见图1。

一种基于SOC硬件标识码的嵌入式软件加密设计,该硬件标识码可以是一种,也可以是多种;例如每个可编程逻辑门阵列FPGA芯片都有自带一个Device DNA,Device DNA由57位二进制编码组成,通过根据Device DNA进行一种加密算法得到一串密钥,也可以是根据Device DNA生成一种文件(包含各种不同格式的数据,例如.bit或者.txt等多种格式的文件);也可以是对Device DNA与其他硬件标识码进行组合加密算法得到一种文件(包含各种不同格式的数据,例如.bit或者.txt等多种格式的文件)。

图1所示是本发明原理框图,其主要由三部分组成,分别FPGA部分与ARM部分以及外围硬件电路。

SOC平台具有FPGA+ARM的结构,首先FPGA读取自身独特的身份证号Device DNA,该身份证号是生产FPGA芯片时固化在芯片一个寄存器当中,具有不可修改的属性;获取到该Device DNA后,FPGA内部通过并行处理算法对Device DNA进行加密得到一种密钥文件;由于Device DNA不具备唯一性,ARM可以读取到外围硬件电路中FLASH的硬件标识码,然后通过AXI总线送到FPGA中,FPGA对Device DNA以及FLASH的硬件标识码进行组合加密生成密钥文件,该密钥文件包含在用户数据中。

上位机利用加密工具将正确的密钥进行处理,生成一种特定格式的文件后,将这种特定格式的文件上传到ARM里面,ARM提前做好解密算法,只对该格式的文件进行校验与解密,把特定文件进行解密后得到正确的密钥;ARM通过AXI总线读取FPGA生成的密钥文件,通过对比两组密钥文件,生成标识符,如果两组对比正确,则ARM给FPGA一个正确的反馈信号,从而对数据进行正确输出,如果两组密钥文件不相同,则ARM给FPGA一个错误的反馈信号,从而使数据无法正确输出(无法正确运行其功能或者算法)。这样就可以实现对数据进行加解密,同时也对密钥文件进行加密处理,双重方式确保数据安全。

本发明提供了一种基于SOC硬件标识码的嵌入式软件加密设计方法,具体实现该技术方案的方法和途径很多,以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。本实施例中未明确的各组成部分均可用现有技术加以实现。

- 一种基于SOC硬件标识码的嵌入式软件加密设计方法

- 一种SoC芯片安全设计方法及硬件平台