半导体芯片及其制备方法和半导体器件

文献发布时间:2023-06-19 11:39:06

技术领域

本发明涉及半导体技术领域,具体的,涉及半导体芯片及其制备方法和半导体器件。

背景技术

WAT测试(Wafer Acceptance Test),即晶圆允收测试,是半导体硅片在完成所有制程工艺后,针对半导体硅片上的各种测试结构进行的电性测试,通过对WAT测试数据的分析,可以发现半导体制程工艺中的问题,帮助制程工艺进行调整。但是,目前的WAT测试准确率和稳定性并不理想,由测试过程导致的不良率较高。

因而,目前半导体制备和测试相关工艺仍有待改进。

发明内容

本发明旨在至少在一定程度上解决相关技术中的技术问题之一。为此,本发明的一个目的在于提出一种WAT测试准确度和稳定性均可有效提升的制备半导体芯片的方法。

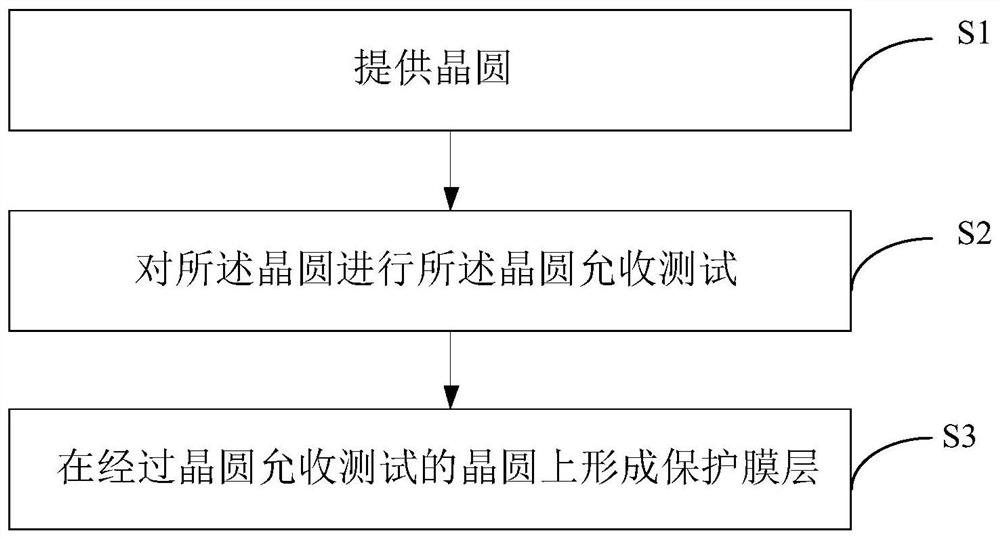

在本发明的一个方面,本发明提供了一种制备半导体芯片的方法。根据本发明的实施例,该方法包括:提供晶圆,所述晶圆上具有多个间隔分布的芯片,相邻的所述芯片之间设有划片道,所述划片道中设有至少一个用于晶圆允收测试(WAT测试)的待测器件;对所述晶圆进行所述晶圆允收测试;在经过所述晶圆允收测试的所述晶圆上形成保护膜层。该方法中,先进行WAT测试然后再形成保护膜层,避免了相关技术中保护膜层残留对测试准确度和稳定性的影响,大大提高了制造效率和良品率,且对测试探针的磨损显著降低,测试成本有效降低。

在本发明的另一方面,本发明提供了一种半导体芯片。根据本发明的实施例,该半导体芯片是利用前面所述的方法制备获得的。该半导体芯片制备过程中WAT测试准确率高,因测试参数异常导致的不良大大降低,良品率明显提高,成本降低。

在本发明的又一方面,本发明提供了一种半导体器件。根据本发明的实施例,该半导体器件包括前面所述半导体芯片。该半导体器件具有前面所述的半导体芯片的全部特征和优点,在此不再一一赘述。

附图说明

图1是相关技术中WAT测试时晶圆表面的平面结构示意图。

图2是本发明一个实施例的制备半导体芯片的方法的流程示意图。

图3是本发明一个实施例的晶圆的平面结构示意图。

图4是本发明一个实施例的WAT测试时晶圆表面的平面结构示意图。

图5是本发明一个实施例的WAT测试的立体结构示意图。

图6是本发明一个实施例的WAT测试的剖面结构示意图。

图7是本发明另一个实施例的制备半导体芯片的方法的流程示意图。

具体实施方式

下面详细描述本发明的实施例。下面描述的实施例是示例性的,仅用于解释本发明,而不能理解为对本发明的限制。实施例中未注明具体技术或条件的,按照本领域内的文献所描述的技术或条件或者按照产品说明书进行。所用试剂或仪器未注明生产厂商者,均为可以通过市购获得的常规产品。

本发明是基于发明人的以下发现和认识而完成的:

发明人在实际生产过程中,发现WAT测试中测试准确度和稳定性并不理想,进一步深入研究后,发明人发现,相关技术中,参照图1(图中近似圆形的黑色轮廓线为保护膜层去除后的边界,黑色轮廓线内的保护膜层被去除,其他部分均设有保护膜层,为了方便展示具体结构,图1中保护膜层下面的结构可以透过保护膜层看到),通常在晶圆的划片道内设有用于WAT测试的测试结构,包括监测工艺流程的各种待测器件(DUT)50,而为了保护晶圆中的芯片,在芯片的制程结束之后,会在晶圆的表面上形成一整层保护膜层40,因此进行WAT测试时需要去除覆盖测试结构连接端的保护膜层,以使得测试结构连接端暴露出来以和WAT测试探针接触,测试时测试仪器输出电信号,施加于探针和测试结构连接端上,得到DUT的电信号反馈后,又通过测试结构连接端和探针导回到测试仪器收集分析,因此探针和测试结构连接端之间的良好接触在整个测试过程中显得很关键,保持良好稳定的接触才能确保测试结果的真实性和稳定性。但由于目前工艺限制,保护膜层不可避免会有少量残留,经测试验证已影响了探针的正常滑动和探针卡与测试结构之间的接触性能,进而影响了测试结果的真实性和稳定性,具体如测试结果不稳定和不真实、针卡探针损耗严重等。具体原因可能有:1、测试结构与探针接触的部分尺寸较小,导致探针可滑动行程较短,影响探针接触性能;2、保护膜层去除不干净且形状不规则,导致探针与测试结构接触不好;两者都会使探针卡的针尖容易弯曲变形和针尖磨损严重,严重降低了探针卡的使用寿命,同时针尖处会累积保护膜层残留物质,导致探针卡测试WAT电性参数时接触不好,参数呈现明显漂移。针对上述问题,发明人尝试从多个方面进行解决,一种可能的方式是增加测试结构与探针接触部分的尺寸,但同时划片道尺寸也会增加,晶圆的芯片图形面积利用率会降低;另一种可能的方式是更换探针卡种类,加粗探针并提高硬度,但因此会增加较多额外成本和浪费更多芯片图形面积,而且没有从根本上解决问题,同时会有重测率偏高问题。经过多方尝试和试验验证,发明人发现在形成保护膜层之前进行WAT测试可以从根本上解决上述问题。

有鉴于此,在本发明的一个方面,本发明提供了一种制备半导体芯片的方法。根据本发明的实施例,参照图2,该方法包括以下步骤:

S1:提供晶圆,参照图3和图4,所述晶圆上设有多个间隔分布的芯片10,相邻的所述芯片10之间设有划片道20,所述划片道20中设有至少一个用于晶圆允收测试的待测器件50。

需要说明的是,本文中采用的描述方式“晶圆”是指在芯片载体上通过外延、离子注入、沉积等等工艺形成芯片后得到的产品,参照图3,一个晶圆上可以形成多个芯片10,相邻的芯片10之间设有划片道20,后续可以沿着划片道进行切割,以得到一颗一颗的芯片。具体的,芯片载体可以为单晶硅圆片等,而芯片具体可以参照常规半导体器件结构,例如包括但不限于IGBT(Insulated Gate Bipolar Transistor,绝缘栅双极型晶体管)芯片、CMOS(Complementary Metal Oxide Semiconductor,互补型金属氧化物半导体)芯片、MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor,金属-氧化物半导体场效应晶体管)芯片、CMOS(Complementary Metal Oxide Semiconductor,互补金属氧化物半导体)芯片、FRD(快恢复二极管)芯片和SBD(肖特基二极管)芯片中的至少一种,以IGBT为例,其可以包括衬底、漂移区、阱区、源区、接触区、绝缘介质层、正面金属、背面金属等等,在此不再一一赘述。

根据本发明的实施例,参照图4,为了进行晶圆允收测试,会在划片道中形成用于晶圆允收测试的待测器件(DUT)50,该待测器件50和芯片10同步形成,通过检测待测器件50的电性能,即可反应芯片10制程工艺中的问题。而将测试结构设在划片道中,可以充分利用芯片图形面积,降低成本。

一些具体实施例中,参照图4,所述划片道20中还可以设有多个在所述划片道的长度方向上间隔设置的焊盘(PAD)30,所述待测器件50设在多个所述焊盘30之间的间隙(包括相邻两个焊盘之间和每个焊盘的四周)处,且所述待测器件50与焊盘电连接,所述焊盘30用于晶圆允收测试插针。由此,可以通过面积相对较大的焊盘与探针接触,便于插针操作,且有利于提高接触效果,进而提高测试准确度和稳定性。

可以理解,焊盘的尺寸越大,越容易与探针接触,操作难度越低,接触效果也会更好,但是焊盘尺寸增大的话,划片道的尺寸也会相应增大,会浪费芯片图形面积,提高成本,通过本发明的方法,可以在焊盘尺寸较小的情况下,依然保证较好的接触效果,保证WAT测试的准确性和稳定性。通常情况下,扎针时探针的滑动方与焊盘的长度方向平行,因此探针的滑动尺寸主要受焊盘的长度限制。一些具体实施例中,焊盘的长度可以小于等于80微米,具体如80微米、75微米、70微米、65微米、60微米等。由此,可以同时保证接触效果和芯片图形面积利用率。

S2:对所述晶圆进行所述晶圆允收测试。

根据本发明的实施例,WAT测试是利用测试仪器的探针卡将探针扎到焊盘上,测试时测试仪器输出电信号,施加于探针和焊盘上,得到DUT的电信号反馈后,又通过PAD和探针导回到测试仪器收集分析。具体的,参照图5和图6,WAT测试仪器包括测试基座1、探针卡2、探针3和测试机(图中未示出,与探针卡相连),测试进行时,被测晶圆100放置在测试基座1上,测试基座与被测晶圆背面接触,通过探针卡2下压使探针3往针尖前方滑行,与DUT50上的金属PAD30形成紧密接触,即将探针扎到PAD上,然后测试机通过探针卡将所需的电信号施加于DUT和测试基座,再经过探针卡收集DUT反馈回来的电信号,传输至测试机处理而获得测试结果,完成测试。

根据本申请的实施例,在进行WAT测试过程中,需要将探针扎到PAD上,可能会产生金属碎屑粘在晶圆的表面,而该金属碎屑会影响后续保护膜层的质量,在存在金属碎屑的位置,保护膜层会形成孔洞,降低保护膜层的保护效果。为了避免上述不利影响,参照图7,在WAT测试之后,且在形成保护膜层之前,该方法可以包括S4:对晶圆进行清洁处理,以去除所述晶圆允收测试导致的金属碎屑。一些具体实施例中,该清洁处理可以包括对所述晶圆依次进行水洗、刷洗和甩干。具体可以为先利用水对晶圆进行冲洗,然后采用刷子刷洗晶圆表面,优选采用软毛刷子进行刷洗,由此在去除金属碎屑的同时不会损伤晶圆,接着对晶圆进行甩干。上述清洁处理可以采用冲刷机进行,由此,设备和步骤简单,可以与相关技术中半导体的清洗步骤采用同样的设备和步骤进行,与相关技术兼容性高,不需要额外的设备,易于实现工业化生产,且成本较低。

S3:在经过所述晶圆允收测试的所述晶圆上形成保护膜层。

根据本发明的实施例,形成保护膜层的具体方法和步骤没有特别限制,可以参照本领域常规步骤进行,例如包括但不限于物理气相沉积或者化学气相沉积等方法,具体如蒸发、溅射等等。

根据本发明的实施例,该保护膜层的具体材质也可以根据实际需要灵活选择。一些具体实施例中,保护膜层可以包括聚酰亚胺膜(PI膜)、氮化硅(SiN

可以理解,本发明的该方法中还可以包括形成芯片的其他步骤,例如形成晶圆的具体步骤、形成保护膜层后还可以进行切割、封装以及其他测试步骤,均可参照常规工艺进行,在此不再一一赘述。

本发明的上述方法中,调整工艺顺序将WAT测试放到生长保护膜层之前,测试时晶圆表面是还未生长有保护膜层的,因此完全消除了保护膜层对WAT测试的影响,包括扎针时探针的滑行和针尖的接触等方面;另外也解决了探针卡因IGBT芯片WAT测试损耗大的问题,使得IGBT芯片能和其它CMOS(Complementary Metal Oxide Semiconductor,互补型金属氧化物半导体)等产品WAT测试共用且通用统一探针卡,减少探针卡更换中的拔插动作。

本发明的方法在不需加大划片道及PAD尺寸设计和不需重新定制特殊探针卡等情况下,做到不增加生产的外部成本,且简单和可行性高,能有效解决WAT测试数据结果不真实准确和不稳定等问题。而且与相关技术相比,本发明的方法对产品本身的工艺基本没有影响,能明显提升测试效率,不影响探针卡的正常使用寿命,能减少探针和PAD接触不好导致的重测,能降低重测对晶圆外观影响的风险等。虽然有些具体实施例中增加了清洁工序,但该操作简单易行,采用现有设备即可实现,增加的生产成本很少。

在本发明的另一方面,本发明提供了一种半导体芯片。根据本发明的实施例,该半导体芯片是利用前面所述的方法制备获得的。该半导体芯片制备过程中WAT测试准确率高,因测试参数异常导致的不良大大降低,良品率明显提高,成本降低。

在本发明的又一方面,本发明提供了一种半导体器件。根据本发明的实施例,该半导体器件包括前面所述半导体芯片。该半导体器件具有前面所述的半导体芯片的全部特征和优点,在此不再一一赘述。

根据本发明的实施例,该半导体器件的具体种类没有特别限制,具体可以为电路控制器件、功率模块等,也可以理解,除了前面描述的芯片之外,该半导体器件还可以包括其他结构,具体均可以参照常规工艺进行,在此不再一一赘述。

下面详细描述本发明的实施例。

实施例1

1、通过常规工艺制备IGBT晶圆;

2、对IGBT晶圆进行WAT测试;

3、在WAT测试后的晶圆表面形成PI膜。

其中,WAT测试中每片晶圆测试5个点的电性参数(具体为金属线条电阻值(CONTI_M,全名为continuity of Metal),此参数用于测试金属线条连续性的电阻值,用于判断金属布线工艺的质量,因为电阻值对扎针接触比较敏感,所以可用于监测WAT测试时探针和金属PAD的接触状态),统计测试24片晶圆的CONTI_M异常率(CONTI_M异常的点的数量/测试的点的总数量),结果显示测试结果全部正常,CONTI_M异常率为0%。

实施例2

1、通过常规工艺制备IGBT晶圆;

2、对IGBT晶圆进行WAT测试;

3、对WAT测试后的晶圆依次进行水洗、刷洗和甩干;

4、在甩干后的晶圆表面形成PI膜。

其中,WAT测试中每片晶圆测试5个点的CONTI_M,统计测试24片晶圆的CONTI_M异常率(CONTI_M异常的点的数量/测试的点的总数量),结果显示测试结果全部正常,CONTI_M异常率为0%。

对比例1

1、通过常规工艺制备IGBT晶圆;

2、在IGBT晶圆表面形成PI膜;

3、去除部分PI膜,并通过去除PI膜后暴露出的待测器件对IGBT晶圆进行WAT测试。

其中,WAT测试中每片晶圆测试5个点的CONTI_M,统计测试24片晶圆的CONTI_M异常率(CONTI_M异常的点的数量/测试的点的总数量),结果显示测试结果全部正常,CONTI_M异常率约为20%。

在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不必须针对的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任一个或多个实施例或示例中以合适的方式结合。此外,在不相互矛盾的情况下,本领域的技术人员可以将本说明书中描述的不同实施例或示例以及不同实施例或示例的特征进行结合和组合。

尽管上面已经示出和描述了本发明的实施例,可以理解的是,上述实施例是示例性的,不能理解为对本发明的限制,本领域的普通技术人员在本发明的范围内可以对上述实施例进行变化、修改、替换和变型。

- 倒装芯片型半导体发光器件、用于制造倒装芯片型半导体发光器件的方法、用于倒装芯片型半导体发光器件的印刷电路板、用于倒装芯片型半导体发光器件的安装结构、以及发光二极管灯

- 倒装芯片型半导体背面用膜、半导体背面用切割带集成膜、半导体器件的生产方法和倒装芯片型半导体器件