一种适用MLVDS驱动器的冷备份和压摆率控制电路

文献发布时间:2023-06-19 19:38:38

技术领域

本发明涉及一种MLVDS输出级电路,特别是一种具备冷备份和压摆率控制的输出级电路,属于高速接口电路设计领域。

背景技术

LVDS通过使用低摆幅差分信号技术,使得信号可以在差分PCB线或平衡双绞线上高速传输,因其具备抗干扰能力强,功耗低、可靠性高、传输速率快等优势在点对点之间数据传输领域得到广泛应用。然而LVDS不适用于总线多点应用,为满足多点系统间通信的需求在LVDS的基础上衍生了MLVDS技术。

当信号在总线上传输时,由于总线分支的的存在导致传输线阻抗不连续,进而带来严重的信号反射问题,而较缓的压摆率可以有效降低电磁干扰问题,因此对于MLVDS驱动器电路,必须具备输出压摆率控制功能,保证信号在总线上正确传输。

在总线应用时,若电路不具备冷备份功能,在LVDS端口加载信号的条件下,电源就不能完成掉电,造成系统错误,因此电路LVDS端口需增加冷备份功能。

发明内容

本发明的目的在于:提供一种适用MLVDS驱动器的冷备份和压摆率控制电路。该电路可以控制驱动器输出差分电压的转换时间,满足协议要求;在电源掉电或者浮空条件下,可以切断从端口到电源的通路,满足冷备份需求,可以用于MLVDS驱动器的设计。

本发明的技术方案是:一种适用MLVDS驱动器的冷备份和压摆率控制电路,包括预驱动电路、冷备份电路和MLVDS输出级电路;

预驱动电路:预驱动电路的输出端连接MLVDS输出级电路,用于产生8相等延迟开关信号,相邻两相开关信号的延迟差为TD,8相等延迟开关信号分别控制MLVDS输出级电路中不同尺寸的MOS管是否导通;

冷备份电路:在电源正常上电时,保证MLVDS输出级电路正常工作;在电源掉电或者浮空条件下,切断MLVDS输出端与电源的寄生通道,实现冷备份功能;

MLVDS输出驱动电路:提供驱动能力,同时受预驱动电路输出信号控制在外部负载电阻两端产生差分信号。

预驱动电路包括组合逻辑单元Q0、Q1、Q2、Q3、Q4、Q5、Q6、Q7、Q8、反相器INV2以及与非门NAND1;

逻辑单元Q0的输入端A1与NAND1输入端连接,输入端A2与逻辑单元Q2输入端连接,输入端A3与使能信号EN连接;逻辑单元Q1的输入端A1与逻辑单元Q0的输出端连接,输入端A2与逻辑单元Q2输入端连接,输入端A3与使能信号EN连接;逻辑单元Q2的输入端A1与逻辑单元Q1的输出端连接,输入端A2与逻辑单元Q3输入端连接,输入端A3与使能信号EN连接;逻辑单元Q3的输入端A1与逻辑单元Q2的输出端连接,输入端A2与逻辑单元Q4输入端连接,输入端A3与使能信号EN连接;逻辑单元Q4的输入端A1与逻辑单元Q3的输出端连接,输入端A2与逻辑单元Q5输入端连接,输入端A3与使能信号EN连接;逻辑单元Q5的输入端A1与逻辑单元Q4的输出端连接,输入端A2与逻辑单元Q6输入端连接,输入端A3与使能信号EN连接;逻辑单元Q6的输入端A1与逻辑单元Q5的输出端连接,输入端A2与逻辑单元Q7输入端连接,输入端A3与使能信号EN连接;逻辑单元Q7的输入端A1与逻辑单元Q6的输出端连接,输入端A2与逻辑单元Q8输入端连接,输入端A3与使能信号EN连接;逻辑单元Q8的输入端A1与逻辑单元Q7的输出端连接,输入端A2与开关信号SW连接,输入端A3与使能信号EN连接;反相器INV2输入端与逻辑单元Q0输入端连接,INV2输出端接与非门NAND1的输入端连接;与非门NAND1的第一输入端与INV2输出端连接,与非门NAND1的第二输入端与开关信号SW连接,与非门NAND1的输出端与逻辑单元Q0的输入端A1连接,逻辑单元Q0、Q1、Q2、Q3、Q4、Q5、Q6、Q7、Q8的输入端A3互相连接,且与使能信号EN连接;预驱动电路产生相位依次延迟8路控制信号SN1、SN2、SN3、SN4、SN5、SN6、SN7、SN8。

冷备份电路包括PMOS管P1-P8、NMOS管N1-N4、电流源I0以及尾电阻Rtail;

PMOS管P1的漏极同时连接PMOS管P4的漏极、PMOS管P3的源极、PMOS管P2的漏极和NMOS管N2的漏极,PMOS管P1的源极同时连接电流源I0和PMOS管P5的源极,PMOS管P1的栅极同时连接NMOS管N1的漏极和PMOS管P4的源极;PMOS管P2的漏极同时与PMOS管P1的漏极、PMOS管P4的漏极、PMOS管P3的源极和NMOS管N2的漏极连接,PMOS管P2的栅极接VDD;PMOS管P3的漏极接OUTP,PMOS管P3的源极同时与PMOS管P1的漏极、PMOS管P4的漏极、PMOS管P2的漏极和NMOS管N2的漏极连接,PMOS管P3的栅极接使能信号ENN;PMOS管P4的漏极同时与PMOS管P1的漏极、PMOS管P2的漏极、PMOS管P3的源极和NMOS管N2的漏极连接,PMOS管P4的源极与PMOS管P1的栅极和NMOS管N1的漏极连接;NMOS管N1的漏极与PMOS管P1的栅极和PMOS管P4的源极连接,NMOS管N1的源极接开关信号SN,NMOS管N1栅极接VDD;NMOS管N2的漏极同时与PMOS管P1的漏极、PMOS管P2的漏极、PMOS管P3的源极和PMOS管P4的漏极连接,NMOS管N2的源极与NMOS管N4的源极和电阻Rtail连接,NMOS管N1的源极接开关信号SN;PMOS管P1、P2、P4做在同一个N阱FW1中,PMOS管P2的源极与所述N阱FW1连接;

PMOS管P5的漏极同时连接PMOS管P6的漏极、PMOS管P7的源极、PMOS管P8的漏极和NMOS管N4的漏极,PMOS管P5的源极同时连接电流源I0和PMOS管P1的源极,PMOS管P5的栅极同时连接NMOS管N3的漏极;PMOS管P6的漏极同时与PMOS管P5的漏极、PMOS管P8的漏极、PMOS管P7的源极和NMOS管N4的漏极连接,PMOS管P6的栅极接VDD;PMOS管P7的漏极接OUTP,PMOS管P7的源极同时与PMOS管P5的漏极、PMOS管P8的漏极、PMOS管P7的漏极和NMOS管N4的漏极连接,PMOS管P7的栅极接使能信号ENN;PMOS管P8的漏极同时与PMOS管P5的漏极、PMOS管P6的漏极、PMOS管P7的源极和NMOS管N4的漏极连接,PMOS管P8的源极与PMOS管P5的栅极和NMOS管N3的漏极连接;NMOS管N3的漏极与PMOS管P5的栅极和PMOS管P8的源极连接,NMOS管N1的源极接开关信号SP,PMOS管N3栅极接VDD;NMOS管N4的漏极同时与PMOS管P5的漏极、PMOS管P6的漏极、PMOS管P7的源极和PMOS管P8的漏极连接,NMOS管N4的源极与NMOS管N2的源极和电阻Rtail连接,NMOS管N4的源极接开关信号SP;PMOS管P5、P6、P8做在同一个N阱FW2中,PMOS管P6的源极与所述N阱FW2连接。

PMOS管P5、P6、P8的N阱FW1与PMOS管P1、P2、P3的N阱FW2是两个相互独立的N阱。

输出驱动电路包括PMOS管P11、P12、P13、P14、P15、P16、P17、P18、P55、P52、P53、P54、P55、P56、P57、P58,NMOS管N21、N22、N23、N24、N25、N26、N27、N28、N41、N44、N43、N44、N45、N46、N47、N48,电流源I0以及尾电阻Rtail;

PMOS管P11、P12、P13、P14、P15、P16、P17、P18、P55、P52、P53、P54、P55、P56、P57、P58的源极相互连接且与电流源I0连接,PMOS管P11、P12、P13、P14、P15、P16、P17、P18的漏极均与PMOS管P3源极连接,PMOS管P55、P52、P53、P54、P55、P56、P57、P58的漏极均与PMOS管P7源极连接;NMOS管N21、N22、N23、N24、N25、N26、N27、N28、N41、N44、N43、N44、N45、N46、N47、N48的源极相互连接且与尾电阻Rtail连接,NMOS管N21、N22、N23、N24、N25、N26、N27、N28的漏极与PMOS管P3源极连接,NMOS管N41、N44、N43、N44、N45、N46、N47、N48的漏极均与PMOS管P7源极连接。

PMOS管P11、P12、P13、P14、P15、P16、P17、P18,PMOS管P55、P52、P53、P54、P55、P56、P57、P58,NMOS管N21、N22、N23、N24、N25、N26、N27、N28,NMOS管N41、N44、N43、N44、N45、N46、N47、N48宽长比依次递增,且为等差数列。

PMOS管P11、P12、P13、P14、P15、P16、P17、P18和NMOS管N21、N22、N23、N24、N25、N26、N27、N28分别由等延迟的8相控制信号SN1~SN8控制,PMOS管P55、P52、P53、P54、P55、P56、P57、P58和NMOS管N41、N44、N43、N44、N45、N46、N47、N48分别由相等间隔8相控制信号SP1~SP8控制,SN与SP为一对相位相反的控制信号。

同一个控制信号所接的PMOS管的宽长比为NMOS管宽长比的2倍。

本发明与现有MLVDS驱动器相比具有如下优点:

(1)本发明的预驱动电路由数字逻辑门级联组成,预驱动电路和驱动级组合实现压摆率控制,具有延迟时间可控、拓展性强、可移植性强、设计简单等优势;

(2)本发明在满足输出信号压摆率控制的同时,通过浮阱结构在电源掉电或者浮空条件下,切断了从端口到电源的通路,支持电路冷备份使用,使用范围更加宽泛。

(3)电路输出端可以耐负压,避免了MLVDS驱动器与接收器共地不良条件下电路出现损伤。

附图说明

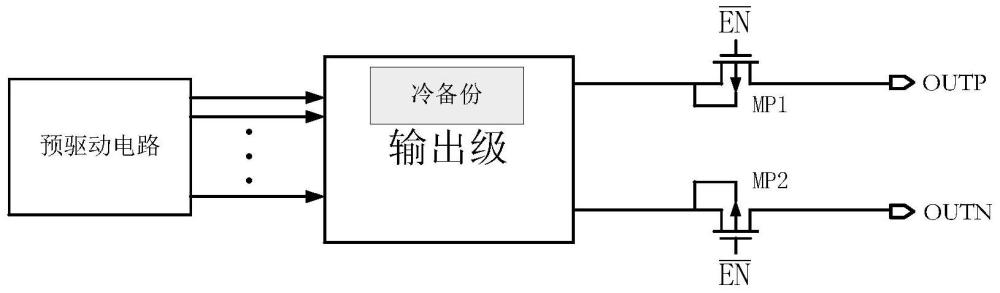

图1为电路结构框图;

图2为预驱动电路图;

图3为冷备份电路图;

图4为输出驱动电路图;

具体实施方式

下面结合附图对本发明的具体实施方式做详细的说明,但本发明的保护范围不局限与以下所述。

本发明中通过等延迟差的多相开关信号控制宽长比依次递增的开关管,从而实现输出差分信号的压摆率控制,可用于MLVDS驱动器的电路设计中。

本发明电路包括预驱动电路、冷备份电路和MLVDS输出级电路。预驱动电路输出8相等延迟开关信号,相邻两相开关信号的延迟差为TD,用于控制输出驱动级电路不同宽长比的开关管延迟开启,输出级电路输出相位相反的差分信号;所述冷备份电路实现在电源浮空或接地条件下,输出端口耐正高压/负压漏电。

如图1所示,一种适用MLVDS驱动器的冷备份和压摆率控制电路包括预驱动电路、冷备份电路和MLVDS输出级电路。预驱动电路输出端连接了输出级电路,冷备份电路可以看出输出级电路的一部分,输出级电路输出正端连接了由使能控制信号

如图2所示,所述的预驱动电路包括组合逻辑单元Q0、Q1、Q2、Q3、Q4、Q5、Q6、Q7、Q8、反相器INV2以及与非门NAND1。其中逻辑单元Q0的输入端A1与NAND1输入端连接,输入端A2与Q2输入端连接,输入端A3与使能信号EN连接;逻辑单元Q1的输入端A1与Q0的输出端连接,输入端A2与Q2输入端连接,输入端A3与使能信号EN连接;逻辑单元Q2的输入端A1与Q1的输出端连接,输入端A2与Q3输入端连接,输入端A3与使能信号EN连接;逻辑单元Q3的输入端A1与Q2的输出端连接,输入端A2与Q4输入端连接,输入端A3与使能信号EN连接;逻辑单元Q4的输入端A1与Q3的输出端连接,输入端A2与Q5输入端连接,输入端A3与使能信号EN连接;逻辑单元Q5的输入端A1与Q4的输出端连接,输入端A2与Q6输入端连接,输入端A3与使能信号EN连接;逻辑单元Q6的输入端A1与Q5的输出端连接,输入端A2与Q7输入端连接,输入端A3与使能信号EN连接;逻辑单元Q7的输入端A1与Q6的输出端连接,输入端A2与Q8输入端连接,输入端A3与使能信号EN连接;逻辑单元Q8的输入端A1与Q7的输出端连接,输入端A2与与开关信号SW连接,输入端A3与使能信号EN连接;反相器INV2输入端与逻辑单元Q0输入端连接,INV2输出端接与非门NAND1的输入端连接。与非门NAND1的输入端一个与INV2输出端连接,一个与开关信号SW连接,与非门NAND1的输出端与Q0的输入端A1连接,逻辑单元Q0、Q1、Q2、Q3、Q4、Q5、Q6、Q7、Q8的输入端A3互相连接,且与使能信号EN连接。

在图2中逻辑单元Q0、Q1、Q2、Q3、Q4、Q5、Q6、Q7、Q8电路结构一样,由反相器INV1、或非门NOR1以及或非门NOR2组成,其中反相器INV1输入端为A1,输出端与或非门NOR2的1输入端连接;或非门NOR1输入端为A2和A3,输出端与或非门NOR2的2输入端连接;NOR2的1输入端与反相器INV1输出端连接,NOR2的2输入端与或非门NOR1输出端连接,NOR2的输出端为Q。

预驱动电路通过利于反相器延迟及组合逻辑使得输出信号SN1与SN2相位延迟差为TD,SN2与SN3相位延迟TD,SN3与SN4相位延迟TD,SN4与SN5相位延迟TD,SN5与SN6相位延迟TD,SN6与SN7相位延迟TD,SN7与SN8相位延迟TD,相位延迟TD的大小可以通过调节反相器INV1来调节。

如图3所示,所述的冷备份电路包括PMOS管P1、P2、P3、P4、P5、P6、P7、P8、NMOS管N1、N2、N3、N4、电流源I0以及尾电阻Rtail。P1的漏极同时连接P4管的漏极、P3管的源极、P2管的漏极和N2管的漏极,P1管的源极同时连接电流源I0和P5管的源极,P1管的栅极同时连接N1管的漏极;P2的漏极同时与P1管的漏极、P4管的漏极、P3管的源极、和N2管的漏极连接,P2的栅极接VDD;P3管的漏极接OUTP,P3管的源极同时与P1管的漏极、P4管的漏极、P2管的漏极、和N2管的漏极连接,P3管的栅极接使能信号ENN;P4管的漏极同时与P1管的漏极、P2管的漏极、P3管的源极和N2管的漏极连接,P4管的源极与P1管的栅极和N1管的漏极连接;N1管的漏极与P1管的栅极和P4管的源极连接,N1管的源极接开关信号SN,N1管栅极接VDD;N2管的漏极同时与P1管的漏极、P2管的漏极、P3管的源极和P4管的漏极连接,N2管的源极与N4管的源极和电阻Rtail连接,N1管的源极接开关信号SN;,PMOS管P1、P2、P4做在同一个N阱FW1中,PMOS管P2的源极与所述N阱连接。P5的漏极同时连接P6管的漏极、P7管的源极、P8管的漏极和N4管的漏极,P5管的源极同时连接电流源I0和P1管的源极,P5管的栅极同时连接N3管的漏极;P6的漏极同时与P5管的漏极、P8管的漏极、P7管的源极、和N4管的漏极连接,P6的栅极接VDD;P7管的漏极接OUTP,P7管的源极同时与P5管的漏极、P8管的漏极、P7管的漏极、和N4管的漏极连接,P7管的栅极接使能信号ENN;P8管的漏极同时与P5管的漏极、P6管的漏极、P7管的源极和N4管的漏极连接,P8管的源极与P5管的栅极和N3管的漏极连接;N3管的漏极与P5管的栅极和P8管的源极连接,N1管的源极接开关信号SP,N3管栅极接VDD;N4管的漏极同时与P5管的漏极、P6管的漏极、P7管的源极和P8管的漏极连接,N4管的源极与N2管的源极和电阻Rtail连接,N4管的源极接开关信号SP;,PMOS管P5、P6、P8做在同一个N阱FW2中,PMOS管P6的源极与所述N阱连接。

PMOS管P5、P6、P8的N阱FW1与P1、P2、P3的N阱FW2是两个相互独立的N阱。

在电源正常上电,假设开关信号SP为高电平、SN为低电平,此时N1、P1导通,N阱FW1通过P2管寄生的PN节充电至高电平,保证P1、P2和P4管正常工作。MLVDS漏电包括两种:一是电源加电,使能关闭,输出耐正高压/负压漏电。端口OUTP或OUTN加正高压时,使能关闭,ENN信号为电源电平,P3管阈值电压>0.8V,P3和P4管关闭,漏电隔离;端口OUTP或OUTN加负电压时,使能关闭,P3和P4管关闭,实现整体漏电隔离。二是电源浮空或接地(VDD=0V~1.5V),输出端口耐正高压/负压漏电。端口OUTP或OUTN加正高压时,P2和P3管导通,FW1和FW2阱电位充电至端口电位一致,由于P4和P8管导通,此时开关管P1和P5的VGS=0V即关闭状态,因此漏电隔离。当输出端口加负电压时,因电源浮空或接地,ENN信号为低,P3和P7管关闭,实现漏电隔离。

如图4所示,所述的输出驱动电路包括PMOS管P11、P12、P13、P14、P15、P16、P17、P18、P55、P52、P53、P54、P55、P56、P57、P58,NMOS管N21、N22、N23、N24、N25、N26、N27、N28、N41、N44、N43、N44、N45、N46、N47、N48,电流源I0以及尾电阻Rtail。PMOS管P11、P12、P13、P14、P15、P16、P17、P18、P55、P52、P53、P54、P55、P56、P57、P58的源极相互连接且与电流源I0连接,PMOS管P11、P12、P13、P14、P15、P16、P17、P18的漏极均与P3管源极连接,PMOS管P55、P52、P53、P54、P55、P56、P57、P58的漏极均与P7管源极连接;NMOS管N21、N22、N23、N24、N25、N26、N27、N28、N41、N44、N43、N44、N45、N46、N47、N48的源极相互连接且与尾电阻Rtail连接,NMOS管N21、N22、N23、N24、N25、N26、N27、N28的漏极与P3管源极连接,NMOS管N41、N44、N43、N44、N45、N46、N47、N48的漏极均与P7管源极连接。

具体地,PMOS管P11、P12、P13、P14、P15、P16、P17、P18,PMOS管P55、P52、P53、P54、P55、P56、P57、P58,NMOS管N21、N22、N23、N24、N25、N26、N27、N28,NMOS管N41、N44、N43、N44、N45、N46、N47、N48宽长比依次递增,且为等差数列。PMOS管P11、P12、P13、P14、P15、P16、P17、P18和NMOS管N21、N22、N23、N24、N25、N26、N27、N28分别由等延迟的8相控制信号SN1~SN8控制,PMOS管P55、P52、P53、P54、P55、P56、P57、P58和NMOS管N41、N44、N43、N44、N45、N46、N47、N48分别由相等间隔8相控制信号SP1~SP8控制,SN与SP为一对相位相反的控制信号。4组开关管均遵循先开小尺寸,先闭大尺寸原则,通过控制开关信号的时间间隔TD,可以实现对输出差分信号压摆率的控制。相互对应PMOS管宽长比约为NMOS管宽长比的2倍。

本发明中预驱动电路由数字逻辑门级联组成,利用门延迟及组合逻辑实产生延迟差为TD的多相开关信号,延迟差为TD便于调节且不易受温度、内部信号干扰,具备拓展性强、可移植性强、设计简单等优势。输出驱动级的开关宽长比依次递增,且为等差数列,预驱动电路输出8相延迟差为TD开关信号分别控制输出驱动级电路中不同尺寸的MOS管延迟导通,进而实现对输出差分信号压摆率的控制,降低反射,保证信号完整性。

本发明电路所用PMOS的N阱不直接与电源相连,在电源正常上电时,该结构可以对N阱进行充电,保证输出级电路正常工作;在电源掉电或浮空条件下,N端下拉管均为NMOS,不存在从N端到电源端的漏电通道;电路采用浮阱结构,N阱不直接与电源端连接,隔绝了P端到电源端的漏电;电路具备冷备份功能。

以上所述,仅为本发明最佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。