一种三维相变存储器亚阈值数据读出电路及读出方法

文献发布时间:2024-01-17 01:24:51

技术领域

本发明涉及微电子技术领域,特别是涉及一种三维相变存储器亚阈值数据读出电路及读出方法。

背景技术

三维相变存储器的存储单元由双向阈值选通管OTS和相变单元PCM串联组成,通过在垂直方向上堆叠存储器单元来实现更多的存储容量,是存储级内存的最佳选择之一。传统读操作时,若选中的1S1R存储单元是低阻状态,OTS就会被选通,利用极大的电流开关比读取数据。而传统的读操作会损耗选通管的循环次数,缩短了三维相变存储器的使用寿命,因此,业界提出了亚阈值区域读取的方法来弥补传统读的不足。

亚阈值读操作无需打开选通管就可以进行读操作,极大地提高了三维相变存储器的操作循环次数。但亚阈值读操作时,低阻状态的存储单元的亚阈值电流较小,导致低高阻的电流比并不大,同时,由于单元电流小,亚阈值读无法忽视三维相变存储器V/2偏置带来的泄漏电流的影响,极小的读窗口裕度限制着存储阵列的容量。目前关于三维相变存储器亚阈值读操作的具体电路研究较少,因此亟需提出一种适用于三维相变存储器亚阈值读的读出电路及读出方法。

发明内容

本发明提供一种三维相变存储器亚阈值数据读出电路及读出方法,解决了三维相变存储器亚阈值读操作时因读窗口裕度小限制了存储阵列大小的问题。

本发明解决其技术问题所采用的技术方案是:提供一种三维相变存储器亚阈值数据读出电路,包括:

灵敏放大器电路,通过位线与所述相变存储阵列连接,用于比较位线电流和参考位线电流,并输出数据读出电压信号;

钳位电压生成电路,与所述灵敏放大器电路连接,用于向所述灵敏放大器电路提供钳位电压,通过所述钳位电压对所述相变存储阵列的位线的电压进行钳位;

字线半偏置电压生成电路,与所述相变存储阵列连接,用于向所述相变存储阵列提供字线半偏置电压;

电流复制电路,与所述字线半偏置电压生成电路以及所述灵敏放大器电路连接,用于抵消所述相变存储阵列产生的泄漏电流;

单元参考电流生成电路,与所述电流复制电路以及所述灵敏放大器电路连接,用于生成单个单元参考电流。

所述灵敏放大器电路包括读电流感应电路和比较电路;

所述读电流感应电路连接位线和参考位线,用于收集所述位线电流和所述参考位线电流,并将所述位线电流和所述参考位线电流转换成差分电压信号;

所述比较电路包括电平位移电路,自偏置电压比较器和输出反相器;所述电平位移电路与所述读电流感应电路连接,用于将所述差分电压信号转换到所述自偏置电压比较器能够处理的数值;所述自偏置电压比较器与所述电平位移电路连接,用于对处理后的差分电压信号进行比较;所述输出反相器与所述自偏置电压比较器连接,用于将所述自偏置电压比较器的比较结果转换成读出电压信号。

所述度电流感应电路包括:

第一PMOS管,所述第一PMOS管的源极连接电源电压输入端;

第二PMOS管,所述第二PMOS管的源极连接电源电压输入端;

第一NMOS管,所述第一NMOS管的漏极连接所述第一PMOS管的漏极,栅极连接所述钳位电压生成电路;

第二NMOS管,所述第二NMOS管的漏极连接所述第二PMOS管的漏极,栅极连接所述第一NMOS管的栅极;

第三NMOS管,所述第三NMOS管的源极连接所述第一PMOS管的漏极,漏极连接所述第一PMOS管的栅极,栅极连接外部第一读使能信号RE1;

第四NMOS管,所述第四NMOS管的源极连接所述第二PMOS管的漏极,漏极连接所述第二PMOS管的栅极,栅极连接所述外部第一读使能信号RE1;

第一电容,所述第一电容的第一端口连接所述第二PMOS管的栅极,第二端口连接所述第一PMOS管的漏极;

第二电容,所述第二电容C2的第一端口连接所述第一PMOS管的栅极,第二端口连接所述第二PMOS管的漏极。

所述电平位移电路包括:

第十五NMOS管,所述第十五NMOS管的源极接地,栅极连接外部偏置VB5输出端;

第十七NMOS管,所述第十七NMOS管的源极连接所述第十五NMOS管的漏极,栅极连接所述第一PMOS管的漏极,漏极作为所述电平位移电路的第二输出端;

第十三PMOS管,所述第十三PMOS管的源极连接电源电压输入端,漏极连接所述第十七NMOS管的漏极,栅极连接外部第二读使能信号RE2的反相信号RE2N;

第十六NMOS管,所述第十六NMOS管的源极接地,栅极连接外部偏置VB5输出端;

第十八NMOS管,所述第十八NMOS管的源极连接所述第十六NMOS管的漏极,栅极连接所述第二PMOS管的漏极,漏极作为所述电平位移电路的第一输出端;

第十四PMOS管,所述第十四PMOS管的源极连接电源电压输入端,漏极连接所述第十八NMOS管的漏极,栅极连接外部第二读使能信号RE2的反相信号RE2N。

所述自偏置电压比较器包括:

第十九NMOS管,所述第十九NMOS管的源极接地;

第二十NMOS管,所述第二十NMOS管的源极连接所述第十九NMOS管的漏极,栅极连接外部第二读使能信号RE2;

第二十一NMOS管,所述第二十一NMOS管的源极连接所述第二十NMOS管的漏极,栅极连接所述电平位移电路的第一输出端;

第二十二NMOS管,所述第二十二NMOS管的源极连接所述第二十NMOS管的漏极,栅极连接所述电平位移电路的第二输出端;

第十五PMOS管,所述第十五PMOS管的源极连接电源电压输入端,栅极连接所述第十九NMOS管的栅极及所述第二十一NMOS管的漏极;

第十六PMOS管,所述第十六PMOS管的源极连接所述第十五PMOS管的漏极,所述栅极连接外部第二读使能信号RE2的反相信号RE2N;

第十七PMOS管,所述第十七PMOS管的源极连接所述第十六PMOS管的漏极,栅极连接所述第二十一NMOS管的栅极,漏极连接所述第二十一NMOS管的漏极;

第十八PMOS管,所述第十八PMOS管的源极连接所述第十六PMOS管的漏极,栅极连接所述第二十二NMOS管的栅极,漏极连接所述第二十二NMOS管的漏极,并作为所述自偏置电压比较器的输出端。

所述输出反相器包括:

第二十三NMOS管,所述第二十三NMOS管的源极接地,栅极连接外部第二读使能信号RE2;

第二十四NMOS管,所述第二十四NMOS管的源极连接所述第二十三NMOS管的漏极,栅极连接所述自偏置电压比较器的输出端;

第十九PMOS管,所述第十九PMOS管的源极连接电源电压输入端,栅极连接外部第二读使能信号RE2的反相信号RE2N;

第二十PMOS管,所述第二十PMOS管的源极连接所述第十九PMOS管的漏极,栅极连接所述第二十四NMOS管的栅极,漏极连接所述第二十四NMOS管的漏极。

所述相变存储阵列包括1S1R相变存储单元,位线传输门和字线传输门;

所述1S1R相变存储单元由相变电阻PCM和双向阈值选通管OTS串联组成;

所述位线传输门包括位线选通传输门和位线半偏传输门;所述位线选通传输门的第一传输端连接所述灵敏放大器电路,所述位线选通传输门的第二传输端连接所述1S1R相变存储单元的一端;所述位线半偏传输门的第一传输端连接外部偏置电压V/2,所述位线半偏传输门的第二传输端连接所述1S1R相变存储单元的一端;

所述字线传输门包括字线选通传输门和字线半偏传输门,所述字线选通传输门的第一传输端接地,所述字线选通传输门的第二传输端连接所述1S1R相变存储单元的另一端;所述字线半偏传输门的第一传输端连接所述字线半偏置电压生成电路,所述字线半偏传输门的第二传输端连接所述1S1R相变存储单元的一端。

所述钳位电压生成电路包括:

第一反相器,所述第一反相器的输入端连接外部第一读使能信号RE1;

第二反相器,所述第一反相器的输入端连接外部第二读使能信号RE2;

第三PMOS管,所述第三PMOS管的源极连接电源电压输入端,栅极连接外部偏置VB4输出端;

第四PMOS管,所述第四PMOS管的源极连接所述第三PMOS管的漏极,所述第四PMOS管的栅极连接外部偏置VRC输出端;

第五PMOS管,所述第五PMOS管的源极连接所述第三PMOS管的漏极,栅极连接所述第一NMOS管的栅极,漏极连接所述第一NMOS管的源极;

第五NMOS管,所述第五NMOS管的漏极和栅极连接所述第四PMOS管的漏极,源极接地;

第六NMOS管,所述第六NMOS管的漏极连接所述第五PMOS管的漏极,栅极连接所述第五NMOS管的栅极,源极接地;

第七NMOS管,所述第七NMOS管的漏极连接所述第五PMOS管的栅极,源极接地,栅极连接所述第一反相器的输出端。

所述字线半偏置电压生成电路包括:

第六PMOS管,所述第六PMOS管的源极连接电源电压输入端,栅极连接外部偏置VB4输出端;

第七PMOS管,所述第七PMOS管的源极连接第六PMOS管的漏极,栅极连接外部偏置电压V/2输出端;

第八PMOS管,所述第八PMOS管的源极连接第六PMOS管的漏极;

第八NMOS管,所述第八NMOS管的漏极和栅极连接所述第七PMOS管的漏极,所源极接地;

第九NMOS管,所述第九NMOS管的漏极连接所述第八PMOS管的漏极,栅极连接所述第八NMOS管的栅极,源极接地;

第九PMOS管,所述第九PMOS管的源极连接电源电压输入端,栅极连接外部偏置VB2输出端;

第十PMOS管,所述第十PMOS管的源极连接所述第九PMOS管的漏极,栅极连接外部偏置VB3输出端;

第一电阻,所述第一电阻的第一端口连接所述第十PMOS管的漏极,第二端口连接所述第八PMOS管的栅极;

第十NMOS管,所述第十NMOS管的源极接地,所述第十NMOS管的栅极连接所述所述第八PMOS管的漏极;

第十四NMOS管,所述第十四NMOS管的源极连接所述第十NMOS管的漏极,漏极连接所述第八PMOS管的栅极以及所述相变存储阵列,栅极连接外部偏置VB1输出端;

第二电阻Rm,所述第二电阻Rm的第一端口连接所述第八PMOS管的漏极;

第三电容Cc,所述第三电容Cc的第一端口连接所述第二电阻Rm的第二端口,第二端口连接述第十四NMOS管的漏极。

所述电流复制电路包括V

所述V

第十一NMOS管,所述第十一NMOS管的源极接地,栅极连接所述连接所述第十NMOS管的栅极;

第十二NMOS管,所述第十二NMOS管的源极连接所述第十一NMOS管的漏极,栅极连接外部偏置VB1输出端,漏极连接所述灵敏放大器电路;

所述支路电流复制模块包括,

第十一PMOS管,所述第十一PMOS管的源极连接电源电压输入端,栅极连接外部偏置VB2输出端;

第十二PMOS管,所述第十二PMOS管的源极连接所述第十一PMOS管的漏极,栅极连接外部偏置VB3输出端,漏极连接所述灵敏放大器电路;

所述V

所述单元参考电流生成电路包括第十三NMOS管,所述第十三NMOS管的源极接地,栅极连接外部偏置V

本发明解决其技术问题所采用的技术方案是:提供一种三维相变存储器亚阈值数据读出方法,应用于上述的三维相变存储器亚阈值数据读出电路,包括以下步骤:

(1)在第一读使能信号RE1有效之后,所述相变存储阵列选中的1S1R相变单元;所述灵敏放大器电路和所述钳位电压生成电路对所述相变存储阵列进行充电操作;

(2)所述字线半偏置电压生成电路将所述相变存储阵列的半偏置的字线稳定在V

(3)当所述V

(4)在所述第一读使能信号RE1无效及第二读使能信号RE2有效之后,所述灵敏放大器电路断开第一NMOS管、第二NMOS管、第三NMOS管和第四NMOS管,基于所述第一电容C1和第二电容C2上存储的电荷对电压SA1和电压SA2进行放大;

(5)所述比较电路对电压SA1和电压SA2的差分信号进行电压移位,并进行比较,输出读出电压。

所述第一读使能信号RE1升至电源电压时开始读步骤(1),所述第一读使能信号RE1由电源电压降至地及所述第二读使能信号RE2升至电源电压时开始读步骤(4)。

所述单元参考电流生成电路基于电压V

有益效果

由于采用了上述的技术方案,本发明与现有技术相比,具有以下的优点和积极效果:本发明通过灵敏放大器、字线半偏置电压生成电路、钳位电压生成电路以及电流复制电路的配合工作下,解决了三维相变存储器亚阈值读操作读裕度窗口小限制存储阵列大小的问题,引入了字线半偏置电压生成电路和钳位电压生成电路,加快了电压稳定的速度,使得泄漏电流可以精确复制,缩短了相变存储器亚阈值数据读取的速度;简化了读操作步骤与控制信号,操作简便。

附图说明

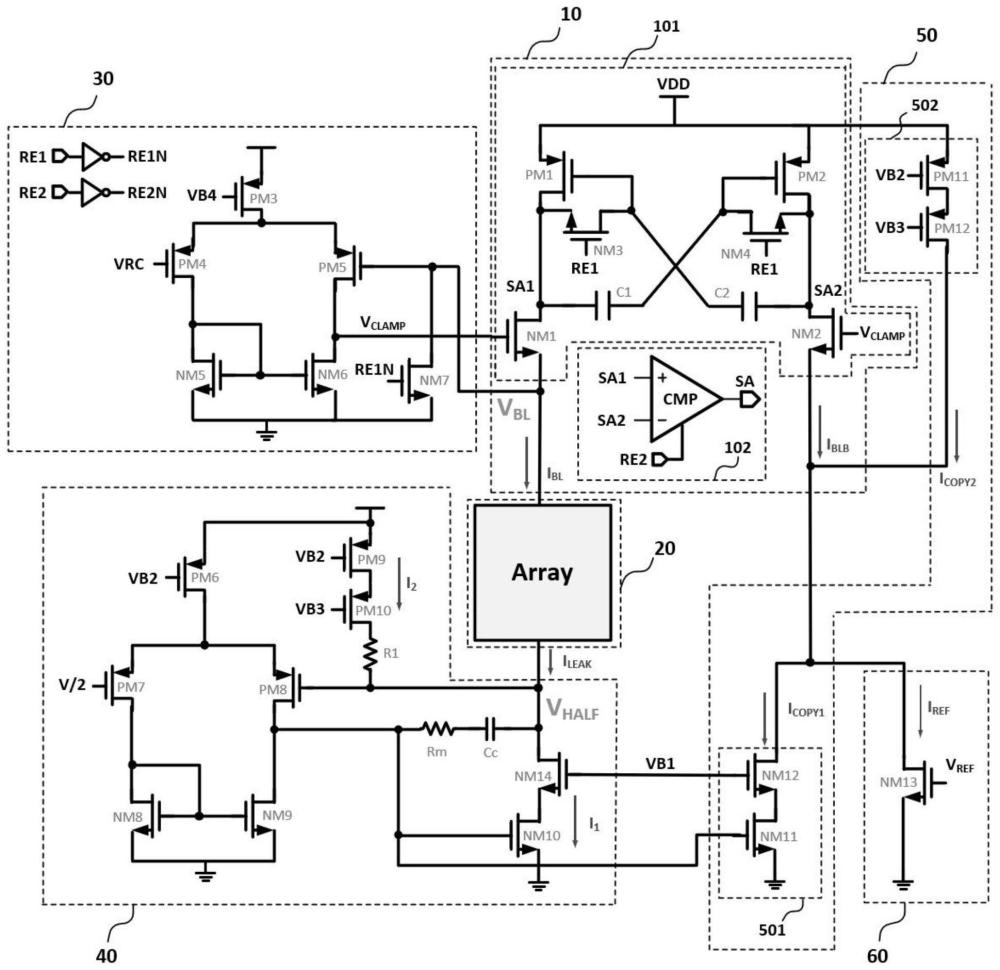

图1为本发明实施例中一种三维相变存储器亚阈值数据读出电路的结构示意图;

图2为本发明实施例中比较电路的结构示意图;

图3为本发明实施例中相变存储器阵列结构示意图;

图4本发明实施例中三维相变存储器亚阈值数据读出方法的步骤示意图;

图5为本发明实施例中亚阈值区域读取低阻相变存储单元的仿真图;

图6为本发明实施例中亚阈值区域读取高阻相变存储单元的仿真图;

其中,10-灵敏放大器电路、101-读电流感应电路、102-比较电路、1021-电平位移电路、1022-自偏置电压比较器、1023-输出反相器、20-相变存储阵列、30-钳位电压生成电路、40-字线半偏置电压生成电路、50-电流复制电路、501-V

具体实施方式

下面结合具体实施例,进一步阐述本发明。应理解,这些实施例仅用于说明本发明而不用于限制本发明的范围。此外应理解,在阅读了本发明讲授的内容之后,本领域技术人员可以对本发明作各种改动或修改,这些等价形式同样落于本申请所附权利要求书所限定的范围。

本发明的实施方式涉及一种三维相变存储器亚阈值数据读出电路,如图1所示,包括:

灵敏放大器电路10,用于比较位线电流和参考位线电流,并输出数据读出电压信号。

相变存储阵列20,通过位线连接所述灵敏放大器电路10,用于存储数据。

钳位电压生成电路30,连接所述灵敏放大器电路10,用于向所述灵敏放大器电路10提供所需的钳位电压,对所述相变存储阵列20的所述位线电压进行钳位,并使所述位线电压快速稳定。

字线半偏置电压生成电路40,连接所述相变存储阵列20,用于向所述相变存储阵列20提供所需的字线半偏置电压,并使所述字线半偏置电压快速稳定。

电流复制电路50,连接所述字线半偏置电压生成电路40以及所述灵敏放大器电路10,用于抵消所述相变存储阵列20产生的泄漏电流。

单元参考电流生成电路60,连接所述电流复制电路50以及所述灵敏放大器电路10,用于生成单个单元参考电流。

本实施方式中的灵敏放大器电路10包括读电流感应电路101和比较电路102;其中,

所述读电流感应电路101连接位线和参考位线,用于收集所述位线电流和所述参考位线电流并将其转换成差分电压信号;

如图2所示,本实施方式中的比较电路102包括:电平位移电路1021、自偏置电压比较器1022和输出反相器1023;其中,

所述电平位移电路1021连接所述读电流感应电路101,用于将所述差分电压转换到合适的数值,以使所述自偏置电压比较器能够处理;

所述自偏置电压比较器1022连接所述所述电平位移电路1021,用于对处理后的差分电压信号进行比较;

所述输出反相器1023连接所述自偏置电压比较器1022,用于将所述自偏置电压比较器1022的比较结果转换成读出电压信号。

本实施方式中,读电流感应电路101包括:

第一PMOS管,所述第一PMOS管的源极连接电源电压输入端。

第二PMOS管,所述第二PMOS管的源极连接电源电压输入端。

第一NMOS管,所述第一NMOS管的漏极连接所述第一PMOS管的漏极。

第二NMOS管,所述第二NMOS管的漏极连接所述第二PMOS管的漏极,所述第二NMOS管的栅极连接所述第一NMOS管的栅极。

第三NMOS管,所述第三NMOS管的源极连接所述第一PMOS管的漏极,所述第三NMOS管的漏极连接所述第一PMOS管的栅极,所述第三NMOS管的栅极连接外部第一读使能信号RE1。

第四NMOS管,所述第四NMOS管的源极连接所述第二PMOS管的漏极,所述第四NMOS管的漏极连接所述第二PMOS管的栅极,所述第四NMOS管的栅极连接所述外部第一读使能信号RE1。

电容C1,所述电容C1的第一端口连接所述第二PMOS管的栅极,所述电容C1的第二端口连接所述第一PMOS管的漏极。

电容C2,所述电容C2的第一端口连接所述第一PMOS管的栅极,所述电容C2的第二端口连接所述第二PMOS管的漏极。

所述电平位移电路1021包括:

第十五NMOS管,所述第十五NMOS管的源极接地,所述第十五NMOS管的栅极连接外部偏置VB5输出端。

第十七NMOS管,所述第十七NMOS管的源极连接所述第十五NMOS管的漏极,所述第十七NMOS管的栅极连接所述所述第一PMOS管的漏极。

第十三PMOS管,所述第十三PMOS管的源极连接电源电压输入端,所述第十三PMOS管的漏极连接所述第十七NMOS管的漏极,所述第十三PMOS管的栅极连接外部第二读使能信号RE2的反相信号RE2N。

第十六NMOS管,所述第十六NMOS管的源极接地,所述第十六NMOS管的栅极连接外部偏置VB5输出端。

第十八NMOS管,所述第十八NMOS管的源极连接所述第十六NMOS管的漏极,所述第十八NMOS管的栅极连接所述所述第二PMOS管的漏极。

第十四PMOS管,所述第十四PMOS管的源极连接电源电压输入端,所述第十四PMOS管的漏极连接所述第十八NMOS管的漏极,所述第十四PMOS管的栅极连接外部第二读使能信号RE2的反相信号RE2N。

本实施方式中,自偏置电压比较器1022包括:

第十九NMOS管,所述第十九NMOS管的源极接地。

第二十NMOS管,所述第二十NMOS管的源极连接所述第十九NMOS管的漏极,所述第二十NMOS管的栅极连接外部第二读使能信号RE2。

第二十一NMOS管,所述第二十一NMOS管的源极连接所述第二十NMOS管的漏极,所述第二十一NMOS管的栅极连接所述第十八NMOS管的源极。

第二十二NMOS管,所述第二十二NMOS管的源极连接所述第二十NMOS管的漏极,所述第二十二NMOS管的栅极连接所述第十七NMOS管的源极。

第十五PMOS管,所述第十五PMOS管的源极连接电源电压输入端,所述第十五PMOS管的栅极连接所述第十九NMOS管的栅极及所述第二十一NMOS管的漏极。

第十六PMOS管,所述第十六PMOS管的源极连接所述第十五PMOS管的漏极,所述第十六PMOS管的栅极连接外部第二读使能信号RE2的反相信号RE2N。

第十七PMOS管,所述第十七PMOS管的源极连接所述第十六PMOS管的漏极,所述第十七PMOS管的栅极连接所述第二十一NMOS管的栅极,所述第十七PMOS管的漏极连接所述第二十一NMOS管的漏极。

第十八PMOS管,所述第十八PMOS管的源极连接所述第十六PMOS管的漏极,所述第十八PMOS管的栅极连接所述第二十二NMOS管的栅极,所述第十八PMOS管的漏极连接所述第二十二NMOS管的漏极。

本实施方式中,所述输出反相器1023包括:

第二十三NMOS管,所述第二十三NMOS管的源极接地,所述第二十三NMOS管的栅极连接外部第二读使能信号RE2。

第二十四NMOS管,所述第二十四NMOS管的源极连接所述第二十三NMOS管的漏极,所述第二十四NMOS管的栅极连接所述第二十二NMOS管的漏极。

第十九PMOS管,所述第十九PMOS管的源极连接电源电压输入端,所述第十九PMOS管的栅极连接外部第二读使能信号RE2的反相信号RE2N。

第二十PMOS管,所述第二十PMOS管的源极连接所述第十九PMOS管的漏极,所述第二十PMOS管的栅极连接所述第二十四NMOS管的栅极,所述第二十PMOS管的漏极连接所述第二十四NMOS管的漏极。

如图3所示,本实施方式中的相变存储阵列20包括:1S1R相变存储单元、位线传输门RTG

所述1S1R相变存储单元由相变电阻PCM和双向阈值选通管OTS串联组成;

所述位线传输门RTG

所述字线传输门RTG

具体的,相变存储阵列20的大小可以为512×512,相变存储阵列大小可根据实际需求设置,不以此实施例为限。

本实施方式中,所述钳位电压生成电路30包括:

第一反相器,所述第一反相器的输入端连接所述外部第一读使能信号RE1。

第二反相器,所述第一反相器的输入端连接所述外部第二读使能信号RE2。

第三PMOS管,所述第三PMOS管的源极连接电源电压输入端,所述第三PMOS管的栅极连接外部偏置VB4输出端。

第四PMOS管,所述第四PMOS管的源极连接所述第三PMOS管的漏极,所述第四PMOS管的栅极连接外部偏置VRC输出端。

第五PMOS管,所述第五PMOS管的源极连接所述第三PMOS管的漏极,所述第五PMOS管的栅极连接所述第一NMOS管的栅极,所述第五PMOS管的漏极连接所述第一NMOS管的源极。

第五NMOS管,所述第五NMOS管的漏极以及所述第五NMOS管的栅极连接所述第四PMOS管的漏极,所述第五NMOS管的源极接地。

第六NMOS管,所述第六NMOS管的漏极连接所述第五PMOS管的漏极,所述第六NMOS管的栅极连接所述第五NMOS管的栅极,所述第六NMOS管的源极接地。

第七NMOS管,所述第七NMOS管的漏极连接所述第五PMOS管的栅极,所述第七NMOS管的源极接地,所述第十NMOS管的栅极连接所述第一反相器的输出端。

本实施方式中,所述字线半偏置电压生成电路40包括:

第六PMOS管,所述第六PMOS管的源极连接电源电压输入端,所述第六PMOS管的栅极连接外部偏置VB4输出端。

第七PMOS管,所述第七PMOS管的源极连接第六PMOS管的漏极,所述第七PMOS管的栅极连接外部偏置电压V/2输出端。

第八PMOS管,所述第八PMOS管的源极连接第六PMOS管的漏极。

第八NMOS管,所述第八NMOS管的漏极以及所述第八NMOS管的栅极连接所述第七PMOS管的漏极,所述第八NMOS管的源极接地。

第九NMOS管,所述第九NMOS管的漏极连接所述第八PMOS管的漏极,所述第九NMOS管的栅极连接所述第八NMOS管的栅极,所述第九NMOS管的源极接地。

第九PMOS管,所述第九PMOS管的源极连接电源电压输入端,所述第九PMOS管的栅极连接外部偏置VB2输出端。

第十PMOS管,所述第十PMOS管的源极连接所述第九PMOS管的漏极,所述第十PMOS管的栅极连接外部偏置VB3输出端。

电阻R1,所述电阻R1的第一端口连接所述第十PMOS管的漏极,所述电阻R1的第二端口连接所述第八PMOS管的栅极。

第十NMOS管,所述第十NMOS管的源极接地,所述第十NMOS管的栅极连接所述所述第八PMOS管的漏极。

第十四NMOS管,所述第十四NMOS管的源极连接所述第十NMOS管的漏极,所述第十四NMOS管的漏极连接所述第八PMOS管的栅极以及所述相变存储阵列20的所述字线半偏传输门的第一传输端,所述第十四NMOS管的栅极连接外部偏置VB1输出端。

电阻R

电容C

本实施方式中,所述电流复制电路50包括V

所述V

第十一NMOS管,所述第十一NMOS管的源极接地,所述第十一NMOS管的栅极连接所述第十NMOS管的栅极。

第十二NMOS管,所述第十二NMOS管的源极连接所述第十一NMOS管的漏极,所述第十二NMOS管的栅极连接所述第十四NMOS管的栅极,所述第十二NMOS管的漏极连接所述第二NMOS管的源极。

所述支路电流复制模块502包括:

第十一PMOS管,所述第十一PMOS管的源极连接电源电压输入端,所述第十一PMOS管的栅极连接所述第九PMOS管的栅极。

第十二PMOS管,所述第十二PMOS管的源极连接所述第十一PMOS管的漏极,所述第十二PMOS管的栅极连接所述第十PMOS管的栅极,所述第十二PMOS管的漏极连接所述第二NMOS管的源极。

作为示例,所述V

本实施方式中,所述单元参考电流生成电路60包括第十三NMOS管,所述第十三NMOS管的源极接地,所述第十三NMOS管的栅极连接外部偏置V

如图4所示,本发明还提供一种三维相变存储器亚阈值数据读出方法,包括以下步骤:

步骤S1,在所述第一读使能信号RE1有效之后,所述相变存储阵列20选中所述的1S1R相变单元;所述灵敏放大器电路10和所述钳位电压生成电路30对所述相变存储阵列20进行充电操作。

步骤S2,所述字线半偏置电压生成电路40将所述相变存储阵列20的半偏置的字线稳定在V

步骤S3,当所述V

步骤S4,在所述第一读使能信号RE1无效及所述第二读使能信号RE2有效之后,所述灵敏放大器电路10断开所述的第一、第二、第三、第四NMOS管,基于所述电容C1、C2上存储的电荷对电压SA1、SA2进行放大。

步骤S5,所述比较电路102对所述差分信号SA1、SA2电压移位,并进行比较,输出读出电压。

作为示例,所述第一读使能信号RE1升至电源电压时开始读步骤S1,所述第一读使能信号RE1由电源电压降至地及所述第二读使能信号RE2升至电源电压时开始读步骤S4。

上述读出方法中,所述位线电压V

通过本实施方式的三维相变存储器亚阈值数据读出电路在对相变存储单元进行读取时,电压仿真结果如图5和图6所示。从图中可以看出,低阻态相变存储单元的亚阈值读取时间为41.5ns,高阻态相变存储单元的亚阈值读取时间为43ns。由此可见,本实施方式的三维相变存储器亚阈值数据读出电路解决了三维相变存储器亚阈值读操作读裕度窗口小限制存储阵列大小的问题,引入了字线半偏置电压生成电路和钳位电压生成电路,加快了电压稳定的速度,使得泄漏电流可以精确复制,缩短了相变存储器亚阈值数据读取的速度;简化了读操作步骤与控制信号,操作简便。