拼接装置

文献发布时间:2023-07-05 06:30:04

技术领域

本发明涉及一种电子装置,尤其涉及一种具备显示功能的拼接装置。

背景技术

具备显示功能的电子装置包括数据驱动电路以及多个像素。数据驱动电路会通过数据引脚将数据信号提供至所述多个像素。为因应高显示分辨率的需求,单位面积的像素数量会增加。因此,数据驱动电路需要增加数据引脚的数量。在数据驱动电路的有限布局面积的情况下,随着数据引脚的数量的增加,数据引脚的宽度会被降低。

应注意的是,在制造工艺上,数据引脚的最小宽度是有限制的。一旦数据引脚的宽度低于被限制的最小宽度,拼接装置的良率势必会降低。为因应高显示分辨率的需求,现行的做法会增加数据驱动电路的数量或增加电路的布局面积。如此一来,上述做法会增加拼接装置的制作成本。因此,如何提供一种具备较少数据引脚数量的驱动方式的电子装置,是本领域技术人员的研究重点之一。

发明内容

本揭露是针对一种具备较少数据引脚数量的驱动方式的拼接装置。

根据本揭露的实施例,拼接装置包括第一基板、第二基板以及数据驱动电路。第一基板包括多个第一半导体单元。第二基板包括多个第二半导体单元。数据驱动电路耦接至第一基板以及第二基板。数据驱动电路将第一数据信号同时提供至所述多个第一半导体单元以及所述多个第二半导体单元,并将第二数据信号同时提供至所述多个第一半导体单元以及所述多个第二半导体单元。

基于上述,数据驱动电路将第一数据信号同时提供至所述多个第一半导体单元以及所述多个第二半导体单元,并将第二数据信号同时提供至所述多个第一半导体单元以及所述多个第二半导体单元。因此,数据驱动电路的数据引脚的数量可以等于第一基板以及第二基板的其中之一的数据通道的数量,而不是等于第一基板的数据通道的通道数量以及第二基板的数据通道的通道数量的总和。如此一来,数据驱动电路的数据引脚的数量被降低。

附图说明

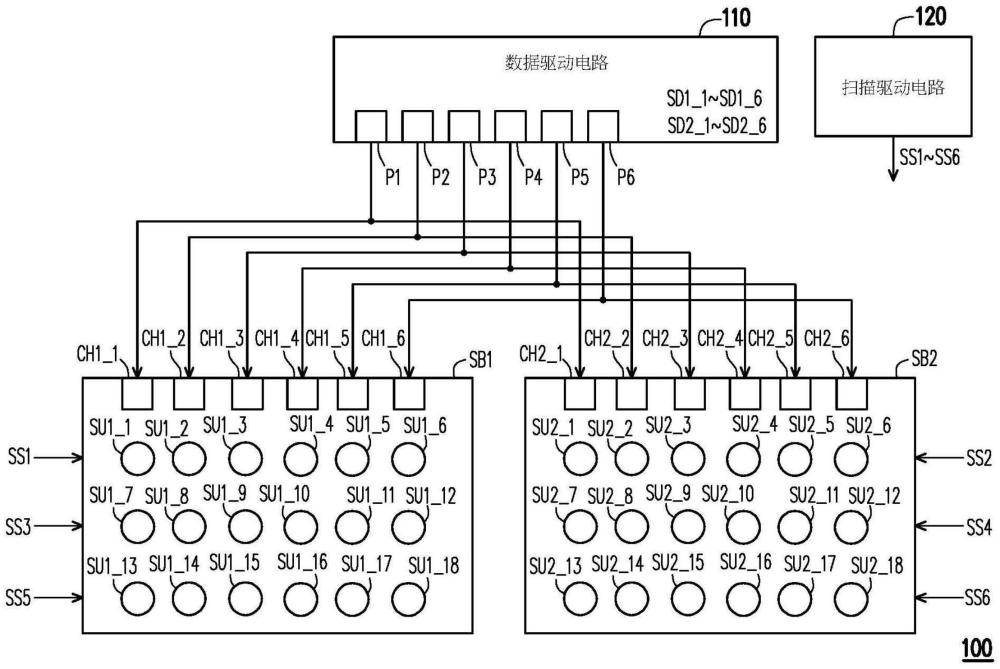

图1是依据本揭露第一实施例所示出的拼接装置的示意图;

图2是依据本揭露第二实施例所示出的拼接装置的示意图;

图3是依据第二实施例所示出的操作示意图;

图4是依据本揭露第三实施例所示出的拼接装置的操作示意图;

图5是依据本揭露第四实施例所示出的拼接装置的操作示意图;

图6是依据本揭露第五实施例所示出的拼接装置的操作示意图;

图7是依据本揭露第六实施例所示出的拼接装置的操作示意图。

附图标记说明

100、200、300、400、500、600:拼接装置

110、310、410、510、610:数据驱动电路

120:扫描驱动电路

230:时序控制器

240:伽玛电路

250:电源电路

CH1_1~CH1_6:第一数据通道

CH2_1~CH2_6:第二数据通道

DP:驱动电能

P1~P6:数据引脚

SB1:第一基板

SB2:第二基板

SB3:第三基板

SB4:第四基板

SB5:第五基板

SB6:第六基板

SB7:第七基板

SB8:第八基板

SB9:第九基板

SB10:第十基板

SB11:第十一基板

SB12:第十二基板

SD1、SD1_1~SD1_6:第一数据信号

SD2、SD2_1~SD2_6:第二数据信号

SD3、SD3_1~SD3_6:第三数据信号

SD4、SD4_1~SD4_6:第四数据信号

SD5、SD5_1~SD5_6:第五数据信号

SD6:第六数据信号

SD7:第七数据信号

SD8:第八数据信号

SD9:第九数据信号

SD10:第十数据信号

SD11:第十一数据信号

SD12:第十二数据信号

SIMG:影像信号

SS1:第一扫描信号

SS2:第二扫描信号

SS3:第三扫描信号

SS4:第四扫描信号

SS5:第五扫描信号

SS6:第六扫描信号

SSn:第n扫描信号

SU1_1~SU1_18:第一半导体单元

SU2_1~SU2_18:第二半导体单元

SU3、SU3_1~SU3_6:第三半导体单元

SU4、SU4_1~SU4_6:第四半导体单元

SU5、SU5_1~SU5_6:第五半导体单元

SU6:第六半导体单元

SU7:第七半导体单元

SU8:第八半导体单元

SU9:第九半导体单元

SU10:第十半导体单元

SU11:第十一半导体单元

SU12:第十二半导体单元

T1:第一时间段

T2:第二时间段

T3:第三时间段

T4:第四时间段

T5:第五时间段

T6:第六时间段

T7:第七时间段

T8:第八时间段

T9:第九时间段

T10:第十时间段

T11:第十一时间段

T12:第十二时间段

具体实施方式

可通过参考如下文所描述的结合附图进行的以下详细描述来理解本揭露。应注意,出于清楚说明且易于读者理解的目的,本揭露的各个附图示出电子装置的一部分,且各个附图中的某些组件可以不按比例绘制。此外,附图中所示出的每个装置的数量和尺寸仅为说明性的且并不旨在限制本揭露的范围。

某些术语在整个描述和以下权利要求中用于指代具体组件。如本领域的技术人员将理解,电子设备制造商可以用不同名称来指代组件。本文件并不打算对名称不同而非功能不同的组件进行区分。在以下描述中和在权利要求中,术语“包含”、“包括”和“具有”以开放式方式使用,且因此应被解释为意指“包含但不限于……”因此,当在本揭露的描述中使用术语“包含”、“包括”和/或“具有”时,将表明存在对应特征、区域、步骤、操作和/或组件,但不限于存在一个或多个对应特征、区域、步骤、操作和/或组件。

应理解,当组件被称为“耦接到”、“连接到”或“导通到”另一组件时,所述组件可直接连接到另一组件且可直接建立电性连接,或在这些组件之间可存在中间组件以用于中继电性连接(间接电性连接)。相比之下,当组件被称为“直接耦接到”、“直接导通到”或“直接连接到”另一组件时,不存在中间组件。

尽管例如第一、第二、第三等的术语可用于描述不同组成组件,但此类组成组件不受这些术语限制。术语仅用于将说明书中的组成组件与其它组成组件区别开。权利要求可以不使用相同术语,而是可相对于组件所要求的顺序使用术语第一、第二、第三等。因此,在以下描述中,第一组成组件可以是权利要求中的第二组成组件。

本揭露的电子装置可包括显示设备、天线装置、感测装置、发光装置、触控电子装置(touch display)、曲面电子装置(curved display)非矩形电子装置(free shapedisplay)、拼接装置或封装装置,但不以此为限。电子装置可包括可弯折或可挠式电子装置。电子装置可例如包括液晶(liquid crystal)、发光二极管、量子点(Quantum dot,QD)、荧光(fluorescence)、磷光(phosphor),其他适合的显示介质,或上述材料的组合,但不限于此。发光二极管可例如包括有机发光二极管(organic light emitting diode,OLED)、次毫米发光二极管(mini LED)、微发光二极管(micro LED)或量子点发光二极管(quantumdot LED,可包括QLED、QDLED)、或其他适合的材料、或上述组合,但不以此为限。显示设备可例如包括拼接显示设备、拼接背光装置,但不以此为限。天线装置可例如是液晶天线,但不以此为限。天线装置可例如包括天线拼接装置,但不以此为限。需注意的是,电子装置可为前述的任意排列组合,但不以此为限。此外,电子装置的外型可为矩形、圆形、多边形、具有弯曲边缘的形状或其他适合的形状。电子装置可以具有驱动系统、控制系统、光源系统…等外围系统以支持显示设备、天线装置或拼接装置,但本揭露不以此为限。感测装置可包括相机或红外线传感器(infrared sensor)或指纹传感器等,本揭露并不以此为限。在一些实施例中,感测装置还可包括闪光灯、红外光(infrared,IR)光源、其他传感器、电子组件、或上述组合,但不限于此。

在本揭露中,实施例使用“像素”或“像素单元”作为用于针对至少一个特定功能描述包含至少一个功能电路的特定区的单元。“像素”的区域取决于用于提供特定功能的单元,相邻像素可共享相同部分或导线,但还可将其自身的特定部分包含于其中。举例来说,相邻像素可共享相同扫描线或相同数据线,但像素还可具有其自身的晶体管或电容。

应注意,在以下所描述的不同实施例中的技术特征可以在在不脱离本揭露的精神的情况下进行替换、重组或与彼此混合以构成另一实施例。

请参考图1,图1是依据本揭露第一实施例所示出的拼接装置的示意图。在本实施例中,拼接装置100包括第一基板SB1、第二基板SB2以及数据驱动电路110。第一基板SB1包括第一半导体单元SU1_1~SU1_18。第二基板SB2包括第二半导体单元SU2_1~SU2_18。第一半导体单元SU1_1~SU1_18以及第二半导体单元SU2_1~SU2_18分别为像素单元或子像素单元。举例来说,第一半导体单元SU1_1~SU1_18以多行(row)以及多列(column)的方式来排列。第二半导体单元SU2_1~SU2_18以多行以及多列的方式来排列。在一些实施例中,第一半导体单元SU1_1~SU1_18与第二半导体单元SU2_1~SU2_18包括发光二极管、光电二极管或天线二极管,但不以此为限。

在一些实施例中,第一半导体单元SU1_1~SU1_18以单行或单列的方式来排列。第二半导体单元SU2_1~SU2_18以单行或单列的方式来排列。

以本实施例为例,第一半导体单元SU1_1~SU1_6分别是第一基板SB1的第一单元行。第一半导体单元SU1_7~SU1_12分别是第一基板SB1的第二单元行。第一半导体单元SU1_13~SU1_18分别是第一基板SB1的第三单元行。第一半导体单元SU1_1、SU1_7、SU1_13分别是第一基板SB1的第一单元列。第一半导体单元SU1_2、SU1_8、SU1_14分别是第一基板SB1的第二单元列,依此类推。因此,基于第一半导体单元SU1_1~SU1_18的上述配置,第一基板SB1具有用以接收第一数据信号SD1_1~SD1_6的第一数据通道CH1_1~CH1_6。第一数据通道CH1_1对应于第一单元列。第一数据通道CH1_2对应于第二单元列,依此类推。

相似地,第二半导体单元SU2_1~SU2_6分别是第二基板SB2的第一单元行。第二半导体单元SU2_7~SU2_12分别是第二基板SB2的第二单元行。第二半导体单元SU2_13~SU2_18分别是第二基板SB2的第三单元行。第二半导体单元SU2_1、SU2_7、SU2_13分别是第二基板SB2的第一单元列。第二半导体单元SU2_2、SU2_8、SU2_14分别是第二基板SB2的第二单元列,依此类推。因此,基于第二半导体单元SU2_1~SU2_18的上述配置,第二基板SB2具有用以接收第二数据信号SD2_1~SD2_6的第二数据通道CH2_1~CH2_6。第二数据通道CH2_1对应于第一单元列。第二数据通道CH2_2对应于第二单元列,依此类推。

为了便于说明,本实施例以第一基板SB1的第一半导体单元SU1_1~SU1_18以及第二基板SB2的第二半导体单元SU2_1~SU2_18来示例。然本揭露并不以此为限。本揭露的基板的数量可以是多个。本揭露的第一基板SB1以及第二基板SB2中的半导体单元的数量可是一个或多个。本揭露的基板的半导体单元的数量以及排列方式可以依据实际的使用需求来调整。本实施例的第一数据通道CH1_1~CH1_6的通道数量相同于第二数据通道CH2_1~CH2_6。在一些实施例中,第一基板SB1的第一数据通道的通道数量不同于第二基板SB2的第二数据通道的通道数量。

在本实施例中,数据驱动电路110耦接至第一基板SB1以及第二基板SB2。数据驱动电路110产生第一数据信号SD1_1~SD1_6以及第二数据信号SD2_1~SD2_6。数据驱动电路110将第一数据信号SD1_1~SD1_6同时提供至第一基板SB1以及第二基板SB2,并将第二数据信号SD2_1~SD2_6同时提供至第一基板SB1以及第二基板SB2。在本实施例中,数据驱动电路110将第一数据信号SD1_1~SD1_6同时提供至第一半导体单元SU1_1~SU1_18以及第二半导体单元SU2_1~SU2_18,并将第二数据信号SD2_1~SD2_6同时提供至第一半导体单元SU1_1~SU1_18以及第二半导体单元SU2_1~SU2_18。因此,数据驱动电路110的数据引脚P1~P6的数量是6个。

在此值得一提的是,数据驱动电路110将第一数据信号SD1_1~SD1_6同时提供至第一半导体单元SU1_1~SU1_18以及第二半导体单元SU2_1~SU2_18,并将第二数据信号SD2_1~SD2_6同时提供至第一半导体单元SU1_1~SU1_18以及第二半导体单元SU2_1~SU2_18。因此,数据驱动电路110的数据引脚P1~P6的数量可以等于第一基板SB1以及第二基板SB2的其中之一的数据通道的通道数量(即,6个),而不是等于第一基板SB1的第一数据通道CH1_1~CH1_6的通道数量以及第二基板SB2的第二数据通道CH2_1~CH2_6的通道数量的总和。如此一来,数据驱动电路110的数据引脚的数量被降低。即便是增加基板的数量,数据驱动电路110的数据引脚的数量并不需要被增加。

进一步来说,在第一时间段中,数据驱动电路110产生第一数据信号SD1_1~SD1_6。数据驱动电路110通过数据引脚P1将第一数据信号SD1_1提供至第一数据通道CH1_1以及第二数据通道CH2_1。数据驱动电路110通过数据引脚P2将第一数据信号SD1_2提供至第一数据通道CH1_2以及第二数据通道CH2_2,依此类推。在第二时间段中,数据驱动电路110产生第二数据信号SD2_1~SD2_6。数据驱动电路110通过数据引脚P1将第一数据信号SD2_1提供至第一数据通道CH1_1以及第二数据通道CH2_1。数据驱动电路110通过数据引脚P2将第一数据信号SD2_2提供至第一数据通道CH1_2以及第二数据通道CH2_2,依此类推。

在本实施例中,第一基板SB1以及第二基板SB2分别是拼接(tiling)基板。举例来说,第一基板SB1以及第二基板SB2可分别是拼接式显示面板、拼接式背光灯板,但不限于此。如此一来,拼接装置100的显示或发光区域可以被扩充。在一些实施例中,第一基板SB1以及第二基板SB2包括发光二极管与薄膜晶体管数组,但不限于此。

在本实施例中,拼接装置100还包括扫描驱动电路120。扫描驱动电路120在不同时间段中提供第一扫描驱动信号SS1、第二扫描驱动信号SS2、第三扫描驱动信号SS3、第四扫描驱动信号SS4、第五扫描驱动信号SS5以及第六扫描驱动信号SS6。扫描驱动电路120耦接至第一基板SB1以及第二基板SB2。扫描驱动电路120在第一时间段中将第一扫描驱动信号SS1提供至第一基板SB1,并且在第二时间段中将第二扫描驱动信号SS2提供至第二基板SB2。举例来说,在第一时间段中,第一半导体单元SU1_1~SU1_6反应于第一扫描驱动信号SS1而被选择。因此,第一半导体单元SU1_1~SU1_6会反应于第一数据信号SD1_1~SD1_6而更新显示内容。在第二时间段中,第二半导体单元SU2_1~SU2_6反应于第二扫描驱动信号SS2而被选择。因此,第二半导体单元SU2_1~SU2_6会反应于第二数据信号SD2_1~SD2_6而更新显示内容,依此类推。在本实施例中,扫描驱动电路120可以是由位移寄存器(shiftregister)或栅极驱动电路来实施。在一些实施例中,扫描驱动电路120也可设置于第一基板SB1以及第二基板SB2上,但不限于此。

请参考图2,图2是依据本揭露第二实施例所示出的拼接装置的示意图。在本实施例中,拼接装置200包括第一基板SB1、第二基板SB2、第三基板SB3、第四基板SB4、第五基板SB5、数据驱动电路110以及扫描驱动电路120。数据驱动电路110耦接至第一基板SB1、第二基板SB2、第三基板SB3、第四基板SB4以及第五基板SB5。在本实施例中,第三基板SB3、第四基板SB4以及第五基板SB5的配置方式大致上相似于第一基板SB1、第二基板SB2的配置方式,故不在此重述。

在本实施例中,数据驱动电路110会在不同时间段中产生第一数据信号SD1_1~SD1_6、第二数据信号SD2_1~SD2_6、第三数据信号SD3_1~SD3_6、第四数据信号SD4_1~SD4_6、第五数据信号SD5_1~SD5_6。举例来说,数据驱动电路110在第一时间段中产生第一数据信号SD1_1~SD1_6,并在第二时间段中产生第二数据信号SD2_1~SD2_6,依此类推。

在本实施例中,数据驱动电路110将第一数据信号SD1_1~SD1_6同时提供至第一基板SB1的第一半导体单元、第二基板SB2的第二半导体单元、第三基板SB3的第三半导体单元、第四基板SB4的第四半导体单元以及第五基板SB5的第五半导体单元。数据驱动电路110将第二数据信号SD2_1~SD2_6同时提供至第一基板SB1的第一半导体单元、第二基板SB2的第二半导体单元、第三基板SB3的第三半导体单元、第四基板SB4的第四半导体单元以及第五基板SB5的第五半导体单元。数据驱动电路110将第三数据信号SD3_1~SD3_6同时提供至第一基板SB1的第一半导体单元、第二基板SB2的第二半导体单元、第三基板SB3的第三半导体单元、第四基板SB4的第四半导体单元以及第五基板SB5的第五半导体单元。数据驱动电路110将第四数据信号SD4_1~SD4_6同时提供至第一基板SB1的第一半导体单元、第二基板SB2的第二半导体单元、第三基板SB3的第三半导体单元、第四基板SB4的第四半导体单元以及第五基板SB5的第五半导体单元。数据驱动电路110将第五数据信号SD5_1~SD5_6同时提供至第一基板SB1的第一半导体单元、第二基板SB2的第二半导体单元、第三基板SB3的第三半导体单元、第四基板SB4的第四半导体单元以及第五基板SB5的第五半导体单元。

在本实施例中,扫描驱动电路120耦接至第一基板SB1、第二基板SB2、第三基板SB3、第四基板SB4以及第五基板SB5。扫描驱动电路120在不同时间段中提供第一扫描驱动信号SS1至第n扫描信号SSn。扫描驱动电路120在第一时间段中将第一扫描驱动信号SS1提供至第一基板SB1,在第二时间段中将第二扫描驱动信号SS2提供至第二基板SB2,并在第三时间段中将第二扫描信号SS3提供至第二基板SB3,依此类推。在一些实施例中,扫描驱动电路120也可设置于第一基板SB1、第二基板SB2、第三基板SB3、第四基板SB4、第五基板SB5上,但不限于此。在一些实施例中,第一基板SB1、第二基板SB2、第三基板SB3、第四基板SB4、第五基板SB5包括发光二极管与薄膜晶体管数组,但不限于此。

在本实施例中,拼接装置200还包括时序控制器230、伽玛电路240以及电源电路250。时序控制器230耦接至数据驱动电路110以及扫描驱动电路120。时序控制器230会提供数据驱动电路110在运行时所需的时钟信号并提供扫描驱动电路120在运行时所需的时钟信号以及初始信号。伽玛电路240耦接至数据驱动电路110。基于伽玛曲线,伽玛电路240会对影像信号SIMG进行数字至模拟转换用以产生第一数据信号SD1_1~SD1_6、第二数据信号SD2_1~SD2_6、第三数据信号SD3_1~SD3_6、第四数据信号SD4_1~SD4_6以及第五数据信号SD5_1~SD5_6的电压信号。在本实施例中,伽玛电路240可以是数字至模拟转换器(Digital to Analog Converter)。电源电路250提供拼接装置200在运行时所需要的驱动电能DP。

请同时参考图2以及图3,图3是依据第二实施例所示出的操作示意图。在本实施例中,第一基板SB1的第一半导体单元、第二基板SB2的第二半导体单元、第三基板SB3的第三半导体单元、第四基板SB4的第四半导体单元以及第五基板SB5的第五半导体单元例如具有相同的排列方式。因此,第一基板SB1的第一数据通道的通道数量、第二基板SB2的第二数据通道的通道数量、第三基板SB3的第三数据通道的通道数量、第四基板SB4的第四数据通道的通道数量第五基板SB5的第五数据通道的通道数量彼此相同。

以更新第一单元行的显示内容为例,在第一时间段T1中,数据驱动电路110将第一数据信号SD1_1~SD1_6提供到第一基板SB1至第五基板SB5。扫描驱动电路120将第一扫描驱动信号SS1提供至第一基板SB1。第一基板SB1的第一单元行反应于第一扫描驱动信号SS1而被选择。因此,第一基板SB1的第一单元行会反应于第一数据信号SD1_1~SD1_6而更新显示内容。在第二时间段T2中,数据驱动电路110将第二数据信号SD2_1~SD2_6提供到第一基板SB1至第五基板SB5。扫描驱动电路120将第二扫描驱动信号SS2提供至第二基板SB2。第二基板SB2的第一单元行反应于第二扫描驱动信号SS2而被选择。因此,第二基板SB2的第一单元行会反应于第二数据信号SD2_1~SD2_6而更新显示内容。在第三时间段T3中,数据驱动电路110将第三数据信号SD3_1~SD3_6提供到第一基板SB1至第五基板SB5。扫描驱动电路120将第三扫描驱动信号SS3提供至第三基板SB3。第三基板SB3的第一单元行反应于第三扫描驱动信号SS3而被选择。因此,第三基板SB3的第一单元行会反应于第三数据信号SD3_1~SD3_6而更新显示内容。在第四时间段T4中,数据驱动电路110将第四数据信号SD4_1~SD4_6提供到第一基板SB1至第五基板SB5。第四基板SB4的第一单元行反应于第四扫描驱动信号SS4而被选择。因此,第四基板SB4的第一单元行会反应于第四数据信号SD4_1~SD4_6而更新显示内容。在第五时间段T5中,数据驱动电路110将第五数据信号SD5_1~SD5_6提供到第一基板SB1至第五基板SB5。第五基板SB5的第一单元行反应于第五扫描驱动信号SS5而被选择。因此,第五基板SB5的第一单元行会反应于第五数据信号SD5_1~SD5_6而更新显示内容。

基于上述,拼接装置200会利用6个通道以及5组扫描信号来更新第一基板SB1至第五基板SB5的第一单元行的显示内容。

在本实施例中,第一时间段T1至第五时间段T5之间的顺序可以被变更。在一些实施例中,扫描驱动电路120可耦接至第一基板SB1、第二基板SB2、第三基板SB3、第四基板SB4以及第五基板SB5。扫描驱动电路120也可设置于第一基板SB1、第二基板SB2、第三基板SB3、第四基板SB4、第五基板SB5上,但不限于此。在一些实施例中,第一基板SB1、第二基板SB2、第三基板SB3、第四基板SB4、第五基板SB5包括发光二极管与薄膜晶体管数组,但不限于此。

请参考图4,图4是依据本揭露第三实施例所示出的拼接装置的操作示意图。在本实施例中,拼接装置300包括第一基板SB1至第十二基板SB12以及数据驱动电路310。第一基板SB1至第十二基板SB12分别具有单一个单元列。因此,数据驱动电路310具有单一个数据引脚。第一基板SB1至第十二基板SB12分别具有单一个数据通道。

以更新第一单元行的显示内容为例,在第一时间段T1中,数据驱动电路310将第一数据信号SD1提供到第一基板SB1至第十二基板SB12。第一基板SB1的第一半导体单元SU1反应于第一扫描信号而被选择。因此,第一半导体单元SU1会反应于第一数据信号SD1而更新显示内容。在第二时间段T2中,数据驱动电路310将第二数据信号SD2提供到第一基板SB1至第十二基板SB12。第二基板SB2的第二半导体单元SU2反应于第二扫描信号而被选择。因此,第二半导体单元SU2会反应于第二数据信号SD2而更新显示内容。同理可推,数据驱动电路310在第三时间段T3至第十二时间段T12中分别产生第三数据信号SD3至第十二数据信号SD12。第三基板SB3至第十二基板SB12的第一单元行的第三半导体单元SU3至第十二半导体单元SU12分别在对应的时间段中反应于对应的扫描信号而被选择而更新显示内容。

基于上述,拼接装置300会利用1个通道以及12组扫描信号来更新第一基板SB1至第五基板SB5的第一单元行的显示内容。在一些实施例中,扫描驱动电路可耦接至第一基板SB1至第十二基板SB12。扫描驱动电路120也可设置于第一基板SB1至第十二基板SB12上,但不限于此。在一些实施例中,第一基板SB1至第十二基板SB12包括发光二极管与薄膜晶体管数组,但不限于此。

请参考图5,图5是依据本揭露第四实施例所示出的拼接装置的操作示意图。在本实施例中,拼接装置400包括第一基板SB1至第五基板SB5以及数据驱动电路410。第一基板SB1至第五基板SB5分别具有6个单元列。数据驱动电路410具有3个数据引脚。第一基板SB1至第五基板SB5的配置相似于图1所示的第一基板SB1的配置方式,故不在此重述。

以更新第一单元行的显示内容为例,在第一时间段T1中,数据驱动电路410将第一数据信号SD1_1~SD1_3提供到第一基板SB1至第五基板SB5。第一基板SB1的第一单元行中的第一半导体单元SU1_1~SU1_3被选择。因此,第一半导体单元SU1_1~SU1_3会反应于第一数据信号SD1_1~SD1_3而更新显示内容。在第二时间段T2中,数据驱动电路410将第一数据信号SD1_4~SD1_6提供到第一基板SB1至第五基板SB5。第一基板SB1的第一单元行中的第一半导体单元SU1_4~SU1_6被选择。因此,第一半导体单元SU1_4~SU1_6会反应于第一数据信号SD1_4~SD1_6而更新显示内容。

在第三时间段T3中,数据驱动电路410将第二数据信号SD2_1~SD2_3提供到第一基板SB1至第五基板SB5。第二基板SB2的第一单元行中的第二半导体单元SU2_1~SU2_3被选择。因此,第二半导体单元SU2_1~SU2_3会反应于第二数据信号SD2_1~SD2_3而更新显示内容。在第四时间段T4中,数据驱动电路410将第二数据信号SD2_4~SD2_6提供到第一基板SB1至第五基板SB5。第二基板SB2的第一单元行中的第二半导体单元SU2_4~SU2_6被选择。因此,第二半导体单元SU2_4~SU2_6会反应于第二数据信号SD2_4~SD2_6而更新显示内容。

在第五时间段T5中,数据驱动电路410将第三数据信号SD3_1~SD3_3提供到第一基板SB1至第五基板SB5。第三基板SB3的第一单元行中的第三半导体单元SU3_1~SU3_3被选择。因此,第三半导体单元SU3_1~SU3_3会反应于第三数据信号SD3_1~SD3_3而更新显示内容。在第六时间段T6中,数据驱动电路410将第三数据信号SD3_4~SD3_6提供到第一基板SB1至第五基板SB5。第三基板SB3的第一单元行中的第三半导体单元SU3_4~SU3_6被选择。因此,第三半导体单元SU3_4~SU3_6会反应于第三数据信号SD3_4~SD3_6而更新显示内容。

在第七时间段T7中,数据驱动电路410将第四数据信号SD4_1~SD4_3提供到第一基板SB1至第五基板SB5。第四基板SB4的第一单元行中的第四半导体单元SU4_1~SU4_3被选择。因此,第四半导体单元SU4_1~SU4_3会反应于第四数据信号SD4_1~SD4_3而更新显示内容。在第八时间段T8中,数据驱动电路410将第四数据信号SD4_4~SD4_6提供到第一基板SB1至第五基板SB5。第四基板SB4的第一单元行中的第四半导体单元SU4_4~SU4_6被选择。因此,第四半导体单元SU4_4~SU4_6会反应于第四数据信号SD4_4~SD4_6而更新显示内容。

在第九时间段T9中,数据驱动电路410将第五数据信号SD5_1~SD5_3提供到第一基板SB1至第五基板SB5。第五基板SB5的第一单元行中的第五半导体单元SU5_1~SU5_3被选择。因此,第五半导体单元SU5_1~SU5_3会反应于第五数据信号SD5_1~SD5_3而更新显示内容。在第十时间段T10中,数据驱动电路410将第五数据信号SD5_4~SD5_6提供到第一基板SB1至第五基板SB5。第五基板SB5的第一单元行中的第五半导体单元SU5_4~SU5_6被选择。因此,第五半导体单元SU5_4~SU5_6会反应于第五数据信号SD5_4~SD5_6而更新显示内容。

基于上述,拼接装置400会利用3个通道以及10组扫描信号来更新第一基板SB1至第五基板SB5的第一单元行的显示内容。

在一些实施例中,在第一时间段T1中,第一半导体单元SU1_1、SU1_3、SU1_5会被选择。在第二时间段T2中,第一半导体单元SU1_2、SU1_4、SU1_6会被选择。本揭露并不以本实施例的选择顺序为限。在一些实施例中,扫描驱动电路可耦接至第一基板SB1、第二基板SB2、第三基板SB3、第四基板SB4以及第五基板SB5。扫描驱动电路120也可设置于第一基板SB1、第二基板SB2、第三基板SB3、第四基板SB4、第五基板SB5上,但不限于此。在一些实施例中,第一基板SB1、第二基板SB2、第三基板SB3、第四基板SB4、第五基板SB5包括发光二极管与薄膜晶体管数组,但不限于此。

请参考图6,图6是依据本揭露第五实施例所示出的拼接装置的操作示意图。在本实施例中,拼接装置500包括第一基板SB1、第二基板SB2以及数据驱动电路510。在本实施例中,第一基板SB1以及第二基板SB2的配置相似于图1所示的第一基板SB1以及第二基板SB2的配置方式,故不在此重述。数据驱动电路510具有单一个数据引脚。第一基板SB1以及第二基板SB2分别具有6个数据通道。

以更新第一单元行的显示内容为例,在第一时间段T1中,数据驱动电路310将第一数据信号SD1_1提供到第一基板SB1以及第二基板SB2。第一基板SB1的第一半导体单元SU1_1被选择。因此,第一半导体单元SU1_1会反应于第一数据信号SD1_1而更新显示内容。在第二时间段T2中,数据驱动电路310将第一数据信号SD1_2提供到第一基板SB1以及第二基板SB2。第一基板SB1的第一半导体单元SU1_2被选择。因此,第一半导体单元SU1_2会反应于第一数据信号SD1_2而更新显示内容,依此类推。在第七时间段T7中,数据驱动电路310将第二数据信号SD2_1提供到第一基板SB1以及第二基板SB2。第二基板SB2的第二半导体单元SU2_1被选择。因此,第二半导体单元SU2_1会反应于第二数据信号SD2_1而更新显示内容。在第八时间段T8中,数据驱动电路310将第二数据信号SD2_2提供到第一基板SB1以及第二基板SB2。第二基板SB2的第二半导体单元SU2_2被选择。因此,第二半导体单元SU2_2会反应于第二数据信号SD2_2而更新显示内容,依此类推。

基于上述,拼接装置500会利用1个通道以及12组扫描信号来更新第一基板SB1以及第二基板SB2的第一单元行的显示内容。在一些实施例中,扫描驱动电路可耦接至第一基板SB1以及第二基板SB2。扫描驱动电路也可设置于第一基板SB1以及第二基板SB2上,但不限于此。在一些实施例中,第一基板SB1以及第二基板SB2包括发光二极管与薄膜晶体管数组,但不限于此。

请参考图7,图7是依据本揭露第六实施例所示出的拼接装置的操作示意图。在本实施例中,拼接装置600包括第一基板SB1至第八基板SB8以及数据驱动电路610。第一基板SB1至第八基板SB8的数据通道的通道数量不完全相同。以本实施例为例,第一基板SB1至第四基板SB4的数据通道的通道数量分别是3个。第五基板SB5至第八基板SB8的数据通道的通道数量分别是1个。数据驱动电路610具有3个数据引脚。拼接装置600的显示区域可以通过具有相同或不同通道数量的基板来扩充。此外,数据驱动电路610的数据引脚并不需要被增加。本揭露并不以第一基板SB1至第八基板SB8的数据通道的通道数量为限。

以更新第一单元行的显示内容为例,在第一时间段T1中,数据驱动电路310将第一数据信号SD1_1~SD1_3提供到第一基板SB1至第八基板SB8。第一基板SB1的第一单元行中的第一半导体单元SU1_1~SU1_3被选择。因此,第一半导体单元SU1_1~SU1_3会反应于第一数据信号SD1_1~SD1_3而更新显示内容。在第二时间段T2中,数据驱动电路610将第一数据信号SD1_4~SD1_6提供到第一基板SB1至第八基板SB8。第一基板SB1的第一单元行中的第一半导体单元SU1_4~SU1_6被选择。因此,第一半导体单元SU1_4~SU1_6会反应于第一数据信号SD1_4~SD1_6而更新显示内容。

在第三时间段T3中,数据驱动电路610将第二数据信号SD2_1~SD2_3提供到第一基板SB1至第八基板SB8。第二基板SB2的第一单元行中的第二半导体单元SU2_1~SU2_3被选择。因此,第二半导体单元SU2_1~SU2_3会反应于第二数据信号SD2_1~SD2_3而更新显示内容。在第四时间段T4中,数据驱动电路610将第二数据信号SD2_4~SD2_6提供到第一基板SB1至第八基板SB8。第二基板SB2的第一单元行中的第二半导体单元SU2_4~SU2_6被选择。因此,第二半导体单元SU2_4~SU2_6会反应于第二数据信号SD2_4~SD2_6而更新显示内容。

在第五时间段T5中,数据驱动电路610将第三数据信号SD3_1~SD3_3提供到第一基板SB1至第八基板SB8。第三基板SB3的第三半导体单元SU3_1~SU3_3被选择。因此,第三半导体单元SU3_1~SU3_3会反应于第三数据信号SD3_1~SD3_3而更新显示内容。在第六时间段T6中,数据驱动电路610将第四数据信号SD4_1~SD4_3提供到第一基板SB1至第八基板SB8。第四基板SB4的第四半导体单元SU4_1~SU4_3被选择。因此,第四半导体单元SU4_1~SU4_3被选择会反应于第四数据信号SD4_1~SD4_3而更新显示内容。

在第七时间段T7中,数据驱动电路410将第五数据信号SD5_1~SD5_3提供到第一基板SB1至第八基板SB8。第五基板SB5的第五半导体单元SU5、第六基板SB6的第六半导体单元SU5以及第七基板SB7的第七半导体单元被选择。因此,第五半导体单元SU5会反应于第五数据信号SD5_1而更新显示内容。第六半导体单元SU6会反应于第五数据信号SD5_2而更新显示内容。第七半导体单元SU7会反应于第五数据信号SD5_3而更新显示内容。

在第八时间段T8中,数据驱动电路410将第六数据信号SD6提供到第一基板SB1至第八基板SB8。第八基板SB8的第八半导体单元SU8被选择。因此,第八半导体单元SU8会反应于第六数据信号SD6而更新显示内容。在一些实施例中,扫描驱动电路可耦接至第一基板SB1至第八基板SB8。扫描驱动电路也可设置于第一基板SB1至第八基板SB8上,但不限于此。在一些实施例中,第一基板SB1至第一基板SB1至第八基板SB8包括发光二极管与薄膜晶体管数组,但不限于此。

综上所述,拼接装置的数据驱动电路将第一数据信号同时提供至所述多个第一半导体单元以及所述多个第二半导体单元,并将第二数据信号同时提供至所述多个第一半导体单元以及所述多个第二半导体单元。因此,数据驱动电路的数据引脚的数量可以等于第一基板以及第二基板的其中之一的数据通道的数量,而不是等于第一基板的数据通道的通道数量以及第二基板的数据通道的通道数量的总和。如此一来,数据驱动电路的数据引脚的数量可被降低,可得到具备较少数据引脚数量的拼接装置。此外,拼接装置的显示区域还可以通过具有相同或不同通道数量的基板来扩充。数据驱动电路的数据引脚并不需要被增加。

最后应说明的是:以上各实施例仅用以说明本揭露的技术方案,而非对其限制;尽管参照前述各实施例对本揭露进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本揭露各实施例技术方案的范围。