模拟数字转换器装置以及时脉偏斜校正方法

文献发布时间:2023-06-19 12:14:58

技术领域

本案是有关于一种模拟数字转换器装置,且特别是有关于时间交错式模拟数字转换器与其时脉偏斜校正方法。

背景技术

模拟数字转换器(analog-to-digital converter,ADC)常应用于各种电子装置中,用于转换模拟信号至数字信号以进行信号处理。在实际应用中,ADC会因为增益误差、电压误差或时序误差影响其本身的解析度或线性度。其中,针对时序误差,现有的技术需设置复杂的电路(例如额外的参考ADC电路、辅助用的ADC电路)或利用晶片外(off-chip)的校正来进行校正,使得ADC的功耗或是校正所需周期越来越高。

发明内容

本案的第一实施态样是在提供一种模拟数字转换器装置,包含:多个模拟数字转换电路、校正电路以及偏斜调整电路。多个模拟数字转换电路用以根据交错的多个时脉信号转换输入信号以产生多个第一量化输出。校正电路用以根据第一量化输出执行至少一校正运算,以产生多个第二量化输出。偏斜调整电路用以将第二量化输出中的偶数项量化输出与比值相乘以产生多个第三量化输出,根据第三量化输出以及第二量化输出中的奇数项量化输出产生多个差值信号,根据差值信号分析时脉信号于取样周期内的时间差信息以产生多个调整信号,其中调整信号用以降低模拟数字转换电路的时脉偏斜。

在一些实施例中,偏斜调整电路更用以分别针对该些差值信号执行多个绝对值运算以产生多个绝对值信号,并用以分别对该些绝对值信号执行多个最大值运算以产生多个最大值信号,接着平均该些最大值信号以产生一参考信号,且将该参考信号分别与该些最大值信号比较以产生该些调整信号。

在一些实施例中,偏斜调整电路包含一延迟电路、多个乘法电路、多个运算电路、多个绝对值电路、多个最大值电路、一平均电路以及多个比较电路。延迟电路用以延迟该些第二量化输出中的一最后一者,以产生一延迟量化输出。乘法电路用以将该些第二量化输出中的偶数项量化输出与该比值相乘以产生多个第三量化输出。运算电路用以依序接收该延迟量化输出、该些第三量化输出以及该些奇数项量化输出,并且该些运算电路用以根据该延迟量化输出、该些第三量化输出以及该些奇数项量化输出中的两个信号分别产生多个差值信号。每一该些绝对值电路用以根据该些差值信号中的一对应差值信号执行一绝对值运算,以产生对应的绝对值信号。每一该些最大值电路用以接收对应的绝对值信号,并执行一最大值运算,以输出对应的最大值信号,其中对应的最大值信号由对应的绝对值信号于该预定期间内的一最大值产生。平均电路用以执行一平均运算以平均该些最大值信号,以产生该参考信号。比较电路,用以比较每一该些最大值信号与该参考信号,以产生该些侦测信号。

在一些实施例中,偏斜调整电路输出该些侦测信号为该些调整信号。

在一些实施例中,该些乘法电路分别电性耦接至偶数项的运算电路,每一该些乘法电路用以传送对应的第三量化输出至对应的偶数项的运算电路。

本案的第二实施态样是在提供一种模拟数字转换器装置,包含:多个模拟数字转换电路、校正电路以及偏斜调整电路。多个模拟数字转换电路用以根据交错的多个时脉信号转换输入信号以产生多个第一量化输出。校正电路用以根据第一量化输出执行至少一校正运算,以产生多个第二量化输出。偏斜调整电路用以将第二量化输出中的奇数项量化输出与比值相乘以产生多个第三量化输出,根据第三量化输出以及第二量化输出中的偶数项量化输出产生多个差值信号,根据差值信号分析时脉信号于取样周期内的时间差信息以产生多个调整信号,其中调整信号用以降低模拟数字转换电路的时脉偏斜。

在一些实施例中,偏斜调整电路更用以分别针对该些差值信号执行多个绝对值运算以产生多个绝对值信号,并用以分别对该些绝对值信号执行多个最大值运算以产生多个最大值信号,接着平均该些最大值信号以产生一参考信号,且将该参考信号分别与该些最大值信号比较以产生该些调整信号。

在一些实施例中,第一调整电路还包含一延迟电路、多个乘法电路、多个运算电路、多个绝对值电路、多个最大值电路、一平均电路以及多个比较电路。延迟电路,用以延迟该些第二量化输出中的一最后一者,以产生一延迟量化输出。乘法电路用以将该些第二量化输出中的奇数项量化输出与该比值相乘以产生多个第三量化输出。运算电路用以依序接收该延迟量化输出、该些第三量化输出以及该些偶数项量化输出,并且该些运算电路用以根据该延迟量化输出、该些第三量化输出以及该些偶数项量化输出中的两个信号分别产生多个差值信号。每一该些绝对值电路用以根据该些差值信号中的一对应差值信号执行一绝对值运算,以产生对应的绝对值信号。每一该些最大值电路用以接收对应的绝对值信号,并执行一最大值运算,以输出对应的最大值信号,其中对应的最大值信号由对应的绝对值信号于该预定期间内的一最大值产生。平均电路用以执行一平均运算以平均该些计算信号,以产生该参考信号。比较电路用以比较每一该些计算信号与该参考信号,以产生该些侦测信号。

在一些实施例中,偏斜调整电路输出该些侦测信号为该些调整信号。

在一些实施例中,该些乘法电路分别电性耦接至奇数项的运算电路,每一该些乘法电路用以传送对应的第三量化输出至对应的奇数项的运算电路。

本案的第三实施态样是在提供一种时脉偏斜校正方法,包含:根据多个模拟数字转换电路所产生的多个第一量化输出执行至少一校正运算,以产生多个第二量化输出;通过偏斜调整电路将第二量化输出中的偶数项量化输出与比值相乘以产生多个第三量化输出,根据第三量化输出以及第二量化输出中的奇数项量化输出产生多个差值信号;以及根据差值信号分析时脉信号于取样周期内的时间差信息以产生多个调整信号;其中调整信号用以降低模拟数字转换电路的时脉偏斜。

在一些实施例中,产生该些差值信号还包含:延迟该些第二量化输出中的一最后一者,以产生一延迟量化输出;将该些第二量化输出中的偶数项量化输出与该比值相乘以产生多个第三量化输出;以及依序接收该延迟量化输出、该些第三量化输出以及该些奇数项量化输出,并且根据该延迟量化输出、该些第三量化输出以及该些奇数项量化输出中的两个信号分别产生多个差值信号。

在一些实施例中,产生该些调整信号还包含:分别针对该些差值信号执行多个绝对值运算以产生多个绝对值信号;分别对该些绝对值信号执行多个最大值运算以产生多个最大值信号;平均该些最大值信号以产生一参考信号;以及比较该参考信号与该些最大值信号以产生该些调整信号。

在一些实施例中,偏斜调整电路输出该些侦测信号为该些调整信号。

在一些实施例中,该比值设定为-1。

本案的第四实施态样是在提供一种时脉偏斜校正方法,包含:根据多个模拟数字转换电路所产生的多个第一量化输出执行至少一校正运算,以产生多个第二量化输出;通过偏斜调整电路将第二量化输出中的奇数项量化输出与比值相乘以产生多个第三量化输出,根据第三量化输出以及第二量化输出中的偶数项量化输出产生多个差值信号;以及根据差值信号分析时脉信号于取样周期内的时间差信息以产生多个调整信号;其中调整信号用以降低模拟数字转换电路的时脉偏斜。

在一些实施例中,产生该些差值信号还包含:延迟该些第二量化输出中的一最后一者,以产生一延迟量化输出;将该些第二量化输出中的奇数项量化输出与该比值相乘以产生多个第三量化输出;以及依序接收该延迟量化输出、该些第三量化输出以及该些偶数项量化输出,并且根据该延迟量化输出、该些第三量化输出以及该些偶数项量化输出中的两个信号分别产生多个差值信号。

在一些实施例中,产生该些调整信号还包含:分别针对该些差值信号执行多个绝对值运算以产生多个绝对值信号;分别对该些绝对值信号执行多个最大值运算以产生多个最大值信号;平均该些最大值信号以产生一参考信号;以及比较该参考信号与该些最大值信号以产生该些调整信号。

在一些实施例中,偏斜调整电路输出该些侦测信号为该些调整信号。

在一些实施例中,该比值设定为-1。

本发明的模拟数字转换器装置及时脉偏斜校正方法主要系利用混频电路将部分的量化输出进行混频产生混频后的量化输出,根据混频后的量化输出与另一部分的量化输出计算出差值信号,使得输入的信号频率在接近奈奎斯特频率(Nyquist frequency)时,可以将时间差值得信息反映得更为明显。因此,数字转换器装置仍然可以通过简单运算取得时脉偏斜的信息以进行校正。如此,可降低整体功耗与校正周期。

附图说明

为让揭示文件的上述和其他目的、特征、优点与实施例能更明显易懂,所附附图的说明如下:

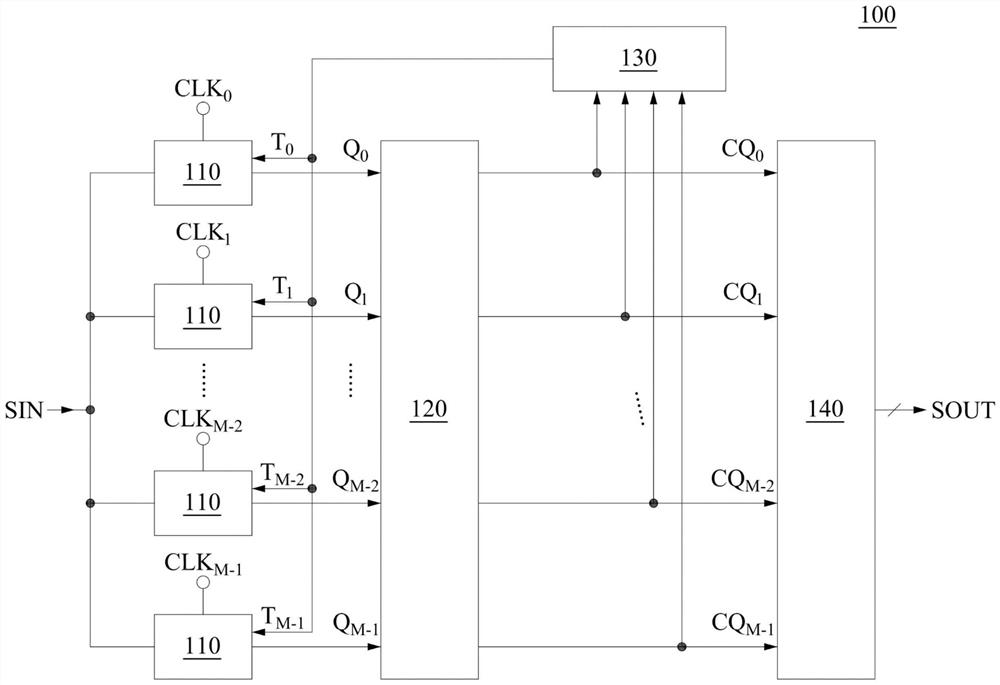

图1A为根据本案一些实施例所绘示的一种模拟数字转换器装置的示意图;

图1B为根据本案一些实施例所绘示的图1A中多个时脉信号的波形示意图;

图2为根据本案的一些实施例所绘示图1A中的偏斜调整电路系统的电路示意图;

图3A为根据本案的一些实施例所绘示差值信号的波形示意图;

图3B为根据本案的一些实施例所绘示差值信号的波形示意图;

图4为根据本案的一些实施例所绘示的一种时脉偏斜校正方法的流程图;

图5为根据本案的一些实施例所绘示图1A中的偏斜调整电路系统的电路示意图;以及

图6为根据本案的一些实施例所绘示的一种时脉偏斜校正方法的流程图。

【符号说明】

100…模拟数字转换器装置

110…模拟数字转换电路

120…校正电路

130…偏斜调整电路

140…输出电路

CLK

Q

SIN…输入信号

fs…取样频率

TS…取样周期

ST…预定期间

SOUT…数字信号

T

205…延迟电路

210A、210B…乘法电路

220…运算电路

230…绝对值电路

240…最大值电路

250…平均电路

260…比较电路

270:滤波电路

280:积分电路

D

A

M

REF…参考信号

SD

TH1…临界值

TR

400、600…时脉偏斜校正方法

S410~S420、S610~S630…步骤

具体实施方式

以下将配合相关附图来说明本发明的实施例。在附图中,相同的标号表示相同或类似的元件或方法流程。

请参阅图1A与图1B,图1A为根据本案一些实施例所绘示的一种模拟数字转换器(analog-to-digital converter,ADC)装置100的示意图。图1B为根据本案一些实施例所绘示的图1A中多个时脉信号CLK

于一些实施例中,ADC装置100包含多个模拟数字转换电路110、校正电路120、偏斜(skew)调整电路130以及输出电路140。值得注意的是,每一个ADC电路110操作为单一通道。换言之,于此例中,ADC装置100包含M个通道。于一些实施例中,M为一偶数。如图1A所示,多个模拟数字转换电路110用以根据多个时脉信号CLK

如图1B所示,多个时脉信号CLK

承上述,校正电路120耦接至每一个模拟数字转换电路110,以接收多个量化输出Q

于一些实施例中,校正电路120可以是前景式校正电路或背景式校正电路。例如,校正电路120可包含一伪随机数值产生器电路(未绘示)与一数字处理电路(未绘示),其中伪随机数值产生器电路产生一校正信号至模拟数字转换电路110,且数字处理电路可根据多个量化输出Q

承上述,偏斜调整电路130电性耦接至校正电路120,以接收多个校正后的量化输出CQ

于一些实施例中,多个模拟数字转换电路110可根据多个调整信号T

承上述,输出电路140电性耦接至校正电路120,以接收校正后的多个量化输出CQ

参照图2,图2为根据本案的一些实施例所绘示图1A中的偏斜调整电路系统130的电路示意图。为了易于理解,图2的类似元件将参照图1A指定为相同标号。于一些实施例中,偏斜调整电路130包含延迟电路205、多个乘法电路210A、多个运算电路220、多个绝对值电路230、多个最大值电路240、平均电路250、多个比较电路260。

延迟电路205用以延迟图1A中的量化输出CQ

如图2所示,多个乘法电路210A电性耦接至图1A中的校正电路120。多个乘法电路210A用以将量化输出CQ

承上述,于一些实施例中,乘法电路210A可由混频器或其他具有相同功能的处理电路实现。各种实现乘法电路210A的电路皆为本揭示所涵盖的范围。

承上述,多个运算电路220电性耦接至乘法电路210A与图1A中的校正电路120。多个运算电路220依序接收延迟量化输出CQ

承上述,以第1个运算电路220为例,第1个运算电路220接收延迟量化输出CQ

同样地,第2个运算电路220系接收乘法电路210A计算后的量化输出-CQ

接着,多个绝对值电路230分别电性耦接至多个运算电路220,以分别接收多个差值信号D

多个最大值电路240分别电性耦接至多个绝对值电路230,以分别接收多个绝对值信号A

于一些实施例中,最大值电路240可由数字处理电路、比较电路与/或暂存器电路实现,但本揭示并不以此为限。各种实现最大值电路240的电路皆为本揭示所涵盖的范围。

平均电路250电性耦接至多个最大值电路250,以接收多个最大值信号M

多个比较电路260分别耦接多个最大值电路240与平均电路250,分别接收最大值信号M

于一些实施例中,比较电路260可由比较器实现。或者,于一些实施例中,比较电路260可由减法器电路实现,并将参考信号REF减去对应的最大值信号M

于一实施例中,多个侦测信号SD

承上述,以第1个运算电路220的操作为例,如图5所示,由于调整信号T

CQ

≈2sin(2πfnT+2πf(T+△T))·cos(πfT+πf△t)…(1)

其中,(n+1)(T+ΔT)相当于量化输出CQ

当输入信号SIN的频率接近于奈奎斯特频率(1/2T)时,式(1)可进一步被推导为下式(2):

sin(2πf(n+1)(T+△t))+sin(2πfnT)≈2sin(2πfnT+2πf(T+△t))·cos(π/2+πf△t)…(2)

由式(2)可以得知,在满足频率f接近于1/2T的条件下时,时间差值Δt与差值信号D

请进一步参考图3A,图3A为根据本案的一些实施例所绘示差值信号的波形示意图。如图3A所示,图3A的纵轴表示为差值信号的振福,横轴表示为时间(已正规化至0~1之间)。接续上方实施例,差值信号D

然而,在先前技术中没有乘法电路210A的情况下,量化输出CQ

CQ

≈2cos(2πfnT+πf(T+△T))·sin(πfT+πf△t)…(3)

当输入信号SIN的频率接近于奈奎斯特频率(1/2T)时,式(3)可进一步被推导为下式(4):

sin(2πf(n+1)(T+△t))-sin(2πfnT)≈2cos(2πfnT+πf(T+△t))·sin(π/2+πf△t)…(4)

因此,由式(4)可以得知,在满足频率f接近于1/2T的条件下时,时间差值Δt与差值信号D

请进一步参考图3B,图3B为根据本案的一些实施例所绘示差值信号的波形示意图。如图3B所示,图3B的纵轴表示为差值信号的振福,横轴表示为时间(已正规化至0~1之间)。接续上方实施例,当频率f接近于奈奎斯特频率(约略是横轴0.25~0.3之间)时,时间差值Δt的变化为范围X2。如图3A及的3B图所示,范围X1比范围X2大。换言之,在接近于奈奎斯特频率时时间差值Δt以cos函数的形式表现比起时间差值Δt以sin函数的形式表现来的明显,因此将差值信号D

接着,通过比较最大值信号M

于一些相关技术中,皆是针对信号频率小于奈奎斯特频率时,获得时脉偏斜的信息的技术。然而,当输入频率接近于奈奎斯特频率时,以往的偏斜调整电路较难反应出时脉偏斜的信息。因此,相较于以往技术,本揭示实施例可达到在输入的信号频率接近奈奎斯特频率时,数字转换器装置仍然可以通过简单运算取得更为明显的时脉偏斜的信息以进行校正,可达到较低的功率消耗与较少的校正周期。值得注意的是,信号频率接近于奈奎斯特频率意谓的是信号频率在1/3T~2/3T之间。

于一些进一步的实施例中,偏斜调整电路130可还包含多个滤波电路270与多个积分电路280。多个滤波电路270分别耦接至多个比较电路260,以分别接收多个侦测信号SD

多个滤波电路270根据多个侦测信号SD

承上述,以第1个滤波电路270与第1个积分电路280为例,滤波电路270电性耦接至第1个比较电路260,以接收侦测信号SD

通过设置滤波电路270,可降低校正时脉偏斜的执行次数,以降低ADC装置100的动态功耗。同时,通过设置滤波电路270亦可降低校正时脉偏斜所引起的抖动(jitter)。通过设置积分电路280,可配合时序调整方法为一个对应值调整的方式。于实际应用中,滤波电路270与积分电路280可以根据实际需求选择性地设置。此外,前述的临界值TH1亦可根据实际需求调整。

于不同实施例中,前述的滤波电路270与积分电路280可由至少一比较器(例如可用于比较触发信号与临界值TH1或比较累积的触发信号)、至少一暂存器(例如可用于储存前述的累加信号或累积的触发信号等等)、至少一清除电路(例如可用于清除前述暂存器的数据)与/或至少一运算电路(例如可用于产生累加信号或用于累积触发信号)实现。上述关于滤波电路270与积分电路280的设置方式用于示例,且本揭示并不以此为限。

请参考图4,图4为根据本案的一些实施例所绘示的一种时脉偏斜校正方法400的流程图。为易于理解,时脉偏斜校正方法400将参照前述各附图进行描述。于一实施例中,时脉偏斜校正方法400首先执行步骤S410,根据多个模拟数字转换电路110所产生的多个量化输出Q

时脉偏斜校正方法400接着执行步骤S420,通过偏斜调整电路130决定量化输出CQ

承上述,于步骤S430中,根据差值信号D

于另一实施例中,图5为根据本案的一些实施例所绘示图1A中的偏斜调整电路系统130的电路示意图。于一些实施例中,偏斜调整电路130包含延迟电路205、多个乘法电路210B、多个运算电路220、多个绝对值电路230、多个最大值电路240、平均电路250、多个比较电路260。于此实施例中,图5所示的偏斜调整电路130与图2所示的偏斜调整电路130类似,两者的差异在于乘法电路210A及210B的实施方式。

承上述,如图5所示,多个乘法电路210B电性耦接至图1A中的校正电路120。多个乘法电路210B用以将延迟量化输出CQ

承上述,于一些实施例中,乘法电路210B可由混频器或其他具有相同功能的处理电路实现。各种实现乘法电路210B的电路皆为本揭示所涵盖的范围。

承上述,多个运算电路220电性耦接至乘法电路210B与图1A中的校正电路120。多个运算电路220依序接收量化输出-CQ

承上述,以第1个运算电路220为例,第1个运算电路220接收乘法电路210B计算后的量化输出-CQ

同样地,第2个运算电路220系接收量化输出CQ

接着,图5所示的延迟电路205、多个绝对值电路230、多个最大值电路240、平均电路250、多个比较电路260、滤波电路270与积分电路280的实施方式与前述图2所示的元件相同,在此不再赘述。

请参考图6,图6为根据本案的一些实施例所绘示的一种时脉偏斜校正方法600的流程图。为易于理解,时脉偏斜校正方法600将参照前述各附图进行描述。于一实施例中,时脉偏斜校正方法600首先执行步骤S610,根据多个模拟数字转换电路110所产生的多个量化输出Q

时脉偏斜校正方法600接着执行步骤S620,通过偏斜调整电路130决定量化输出CQ

承上述,于步骤S630中,根据差值信号D

综上所述,本揭露的模拟数字转换器装置及时脉偏斜校正方法主要是利用混频电路将部分的量化输出进行混频产生混频后的量化输出,根据混频后的量化输出与另一部分的量化输出计算出差值信号,使得输入的信号频率在接近奈奎斯特频率(Nyquistfrequency)时,可以将时间差值得信息反映得更为明显。因此,数字转换器装置仍然可以通过简单运算取得时脉偏斜的信息以进行校正。如此,可降低整体功耗与校正周期。

在说明书及申请专利范围中使用了某些词汇来指称特定的元件。然而,所属技术领域中具有通常知识者应可理解,同样的元件可能会用不同的名词来称呼。说明书及申请专利范围并不以名称的差异做为区分元件的方式,而是以元件在功能上的差异来做为区分的基准。在说明书及申请专利范围所提及的“包含”为开放式的用语,故应解释成“包含但不限定于”。另外,“耦接”在此包含任何直接及间接的连接手段。因此,若文中描述第一元件耦接于第二元件,则代表第一元件可通过电性连接或无线传输、光学传输等信号连接方式而直接地连接于第二元件,或者通过其他元件或连接手段间接地电性或信号连接至该第二元件。

另外,除非说明书中特别指明,否则任何单数格的用语都同时包含复数格的涵义。

以上仅为本发明的较佳实施例,凡依本发明权利要求所做的均等变化与修饰,皆应属本发明的涵盖范围。

- 模拟数字转换器装置以及时脉偏斜校正方法

- 模拟数字转换器装置以及时脉偏斜校正方法