具有复位芯片功能的低电平复位电路及低电平复位方法

文献发布时间:2023-06-19 11:06:50

技术领域

本发明属于集成电路应用技术领域,涉及一种给应用芯片提供低电平复位信号,具有复位芯片功能的低电平复位电路及低电平复位方法。

背景技术

芯片是大规模集成电路,其中包含大量的数字模拟模块单元,其中部分芯片设计具有复位单元,其目的是使芯片整个系统恢复到初始已知的状态开始执行任务。但是很多芯片设计时没有自复位单元,需要借助外部独立的复位电路或复位芯片给其复位。复位芯片具有较好的复位效果,但是使用成本比较高。而且复位芯片的复位阈值电压值和复位时间一旦选定则不能改变,不能根据需要进行调整。如MAX809复位芯片只有固定的几档复位阈值电压值(2.32/2.63/2.93/3.08/4.00/4.38/4.63V),并且只提供固定的低电平复位时间。而现有的复位电路只是简单地采用一个电阻和一个电解电容或瓷片电容的结构,在实际调试过程中这些简单的复位电路有许多的不足,如复位不完全导致死机等故障。

发明内容

本发明的一个目的是针对需要低电平复位的芯片,提供具有复位芯片功能的低电平复位电路。

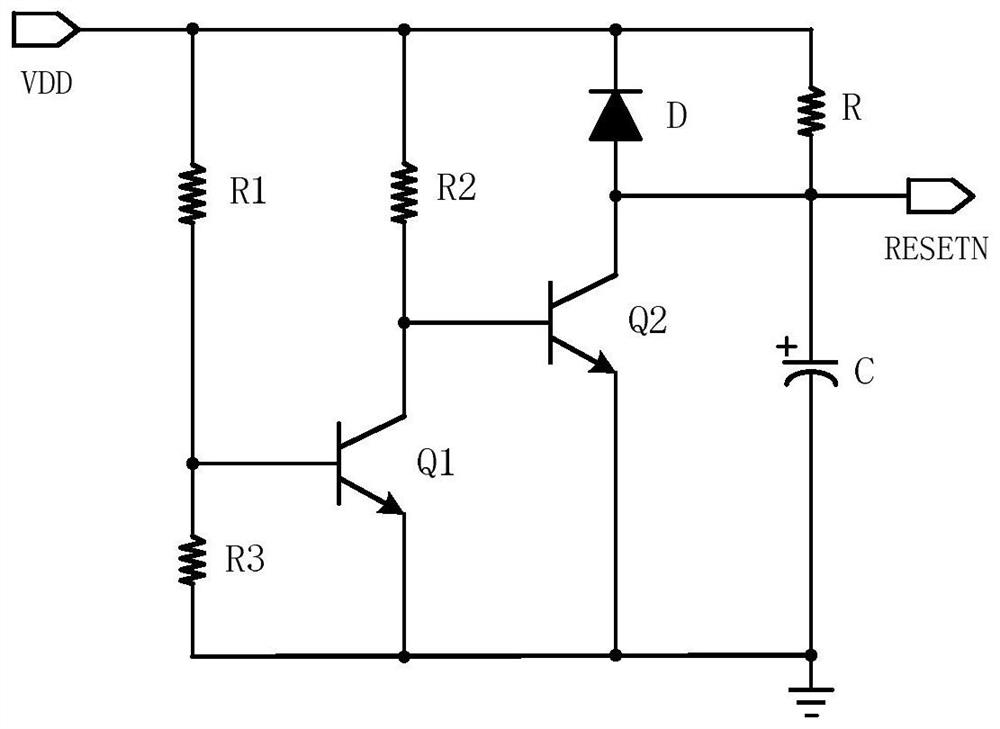

本发明电路包括一个充放电电阻R、电解电容C、肖特基二极管D、两个NPN三极管和三个控制电阻;三个控制电阻分别控制两个NPN三极管的导通和关断,两个NPN三极管作为电子开关,电解电容C用于充放电。

肖特基二极管D的阴极与充放电电阻R的一端、第一控制电阻R1的一端、第二控制电阻R2的一端连接后作为电源输入端VDD;第一NPN三极管Q1的基极接第一控制电阻R1的另一端和第三控制电阻R3的一端,第一NPN三极管Q1的集电极接第二控制电阻R2的另一端和第二NPN三极管Q2的基极;第二NPN三极管Q2的集电极、肖特基二极管D的阳极、充放电电阻R的另一端、电解电容C的正极连接后作为复位输出端RESETN;第一NPN三极管Q1和第二NPN三极管Q2的发射极、电解电容C的负极、第三控制电阻R3的另一端连接后接地。

本发明的另一个目的是提供一种利用上述电路给需要外置低电平复位的芯片提供低电平复位信号的方法。

将复位电路的电源输入端VDD接芯片的IO电源,复位输出端RESETN接芯片的低电平复位脚。

芯片IO电源上电后,在IO电源上升到复位阈值电压值前,第一NPN三极管Q1的基极未到达三极管基射结阈值电压,第一NPN三极管Q1截止,而IO电源电压同时通过控制第二控制电阻R2直接加到第二NPN三极管Q2的基极,第二NPN三极管Q2饱和导通,导致复位输出端RESETN被第二NPN三极管Q2的集射结钳位在低电平;当IO电源上升到复位阈值电压值后,第一NPN三极管Q1的基极到达三极管基射结阈值电压,第一NPN三极管Q1饱和导通,第一NPN三极管Q1的集射结钳位住第二NPN三极管Q2的基射结,导致第二NPN三极管Q2截止,IO电源电压通过充放电电阻R对电解电容C进行充电,复位输出端RESETN保持一定时间的低电平信号,从而让芯片起到冷机复位的作用。

芯片IO电源掉电后,电解电容C通过肖特基二极管D迅速跟着IO电源掉电,当掉电达到复位阈值电压值时,第一NPN三极管Q1迅速截止,而第二NPN三极管Q2迅速饱和导通,导致电解电容C通过第二NPN三极管Q2的集射结迅速泄放到地,从而保证复位输出端RESETN不会出现在电平不确定状态下,避免复位异常现象发生。

当发现复位阈值电压值V

当发现低电平复位时间不够时候,根据芯片具体需要的最大复位时间,通过改变充放电电阻R的阻值R′和电解电容C的容值C′,从而改变低电平复位的时间T

本发明在芯片复位脚与电源地之间设置NPN三极管开关、RC充放电电路和肖特基二极管,当芯片IO电源上升到复位阈值电压前,NPN三极管开关导通,复位得到持续一定时间的低电平复位信号,当超过复位阈值电压后NPN三极管开关断开,由RC充放电电路利用电容电压不突变的特点,继续提供低电平复位信号,直到芯片复位脚认为高电平复位结束。当芯片IO电源突然下降,复位脚电压通过肖特基二极管单向导电性也迅速下降,当下降到复位阈值电压时,NPN三极管开关导通,芯片复位脚被快速拉低,保证复位脚不进入电平不确定状态导致下次快速复位异常问题。本发明方法安全可靠,通过简单稳定的电路保证了芯片复位的安全可靠。本发明能够自由调节复位阈值和低电平复位时间,该复位电路及复位方法安全可靠。

附图说明

图1为本发明的电路图。

具体实施方式

如图1所示,一种具有复位芯片功能的低电平复位电路,包括一个充放电电阻R、电解电容C、肖特基二极管D、两个NPN三极管和三个控制电阻。三个控制电阻分别控制两个NPN三极管的导通和关断,两个NPN三极管作为电子开关,电解电容C用于充放电。

肖特基二极管D的阴极与充放电电阻R的一端、第一控制电阻R1的一端、第二控制电阻R2的一端连接后作为电源输入端VDD。第一NPN三极管Q1的基极接第一控制电阻R1的另一端和第三控制电阻R3的一端,集电极接第二控制电阻R2的另一端和第二NPN三极管Q2的基极;第二NPN三极管Q2的集电极、肖特基二极管D的阳极、充放电电阻R的另一端、电解电容C的正极连接后作为复位输出端RESETN。第一NPN三极管Q1和第二NPN三极管Q2的发射极、电解电容C的负极、第三控制电阻R3的另一端连接后接地。

使用中,将电路的电源输入端VDD接芯片的IO电源,复位输出端RESETN接芯片的低电平复位脚。

当第一PNP三极管Q1的基射结大于等于三极管Q1本身的基射结阈值时,第一NPN三极管Q1的集射结饱和导通输出低电平;当第一PNP三极管Q1的基射结小于三极管Q1本身的基射结阈值时,第一NPN三极管Q1的集射结截止输出高电平。

当第二PNP三极管Q2的基射结大于等于三极管Q2本身的基射结阈值时,第二NPN三极管Q2的集射结饱和导通输出低电平;当第二PNP三极管Q2的基射结小于三极管Q2本身的基射结阈值时,第二NPN三极管Q2的集射结截止,处于断开状态。

芯片IO电源上电后,在IO电源上升到复位阈值电压值前,第一NPN三极管Q1的基极未到达三极管基射结阈值电压,第一NPN三极管Q1截止,而IO电源电压同时通过控制第二控制电阻R2直接加到第二NPN三极管Q2的基极,第二NPN三极管Q2饱和导通,导致复位输出端RESETN被第二NPN三极管Q2的集射结钳位在低电平。当IO电源上升到复位阈值电压值后,第一NPN三极管Q1的基极到达三极管基射结阈值电压,第一NPN三极管Q1饱和导通,第一NPN三极管Q1的集射结钳位住第二NPN三极管Q2的基射结,导致第二NPN三极管Q2截止,IO电源电压通过充放电电阻R对电解电容C进行充电,复位输出端RESETN保持一定时间(保持时间的长短由充放电电阻R和电解电容C预置调节决定)的低电平信号,从而让芯片起到冷机复位的作用。复位阈值电压值即为第一NPN三极管Q1的复位阈值电压值,由第一控制电阻R1和第三控制电阻R3预置调节决定。

芯片IO电源掉电后,电解电容C通过肖特基二极管D迅速跟着IO电源掉电,当掉电达到复位阈值电压值时,第一NPN三极管Q1迅速截止,而第二NPN三极管Q2迅速饱和导通,导致电解电容C通过第二NPN三极管Q2的集射结迅速泄放到地,从而保证复位输出端RESETN不会出现在电平不确定状态下,避免复位异常现象发生,从而准备好迎接再次冷机复位,避免反复开关机第一次复位不完善导致第二次开机不正常问题。而复位阈值电压值的预设定可以避免电源波动到电平不可识别区域导致的复位不完全问题。

当发现复位阈值电压值V

当发现低电平复位时间不够时候,根据芯片具体需要的最大复位时间,通过改变充放电电阻R的阻值R′和电解电容C的容值C′,从而改变低电平复位的时间T

应该理解的是上述实例只是对本发明的说明,而不是对本发明的限制,任何不超出本发明实质精神范围内的发明创造,均落入本发明的保护范围之内。