用于处理具有缺口的晶片的等离子体排除区域环

文献发布时间:2023-06-19 18:27:32

相关申请的交叉引用

本申请要求于2020年3月27日申请的美国临时申请No.63/000,697的优先权。上述引用的申请其全部公开内容都通过引用合并于此。

技术领域

本公开涉及处理具有缺口的晶片。

背景技术

这里提供的背景描述是为了总体呈现本公开的背景的目的。当前指定的发明人的工作在其在此背景技术部分以及在提交申请时不能确定为现有技术的说明书的各方面中描述的范围内既不明确也不暗示地承认是针对本公开的现有技术。

衬底处理系统可用于处理诸如半导体晶片之类的衬底。可以在衬底上执行的示例性处理包括但不限于化学气相沉积(CVD)、原子层沉积(ALD)、导体蚀刻、快速热处理(RTP)、离子植入、物理气相沉积(PVD)和/或其他蚀刻、沉积或清洁工艺。衬底可以布置在衬底处理系统的处理室中的衬底支撑件上,衬底支撑件例如基座、静电卡盘(ESC)等。在处理期间,可以将包括一种或多种前体的气体混合物引入处理室,并且可以使用等离子体来引发化学反应。

发明内容

提供了一种用于衬底处理系统的等离子体排除区域环,所述衬底处理系统被配置成处理衬底。所述等离子体排除区域环包括:环状主体、所述环状主体的上部、基部和等离子体排除区域环缺口。所述环状主体的上部限定径向内侧表面以及顶表面。所述环状主体的基部限定径向外侧表面;第一底表面,其从所述径向外侧表面径向朝内延伸;以及第二底表面,其从所述第一底表面径向朝内延伸。所述等离子体排除区域环缺口正比于所述衬底的对准缺口。所述第一底表面是倾斜的,且以锐角从所述第二底表面延伸至所述径向外侧表面。所述第一底表面被配置成在所述衬底的周缘上方延伸,并与所述周缘相对。

在其他特征中,所述基部包括所述等离子体排除区域环缺口。

在其他特征中,所述等离子体排除区域环缺口正比于所述衬底的对准缺口。

在其他特征中,所述等离子体排除区域环缺口具有与所述衬底的对准缺口相同的轮廓。

在其他特征中,所述等离子体排除区域环缺口被配置成提高所述衬底的缺口处或附近的蚀刻或沉积量。

在其他特征中,所述等离子体排除区域环缺口从所述径向外侧表面和所述第一底表面径向朝内延伸。

在其他特征中,所述等离子体排除区域环缺口包括单一凹陷表面,所述凹陷表面被配置成与所述衬底相对。在其他特征中,所述等离子体排除区域环缺口具有从径向最内侧边缘至径向最外侧边缘的变化深度。

在其他特征中,所述等离子体排除区域环缺口具有从径向最内侧边缘至径向最外侧边缘的不变深度。

在其他特征中,所述等离子体排除区域环缺口包括凹陷表面。所述凹陷表面中的一者或更多者被配置成与所述衬底相对。

在其他特征中,所述凹陷表面包括:第一凹陷表面,其以相对于所述衬底的锐角延伸;以及第二凹陷表面,其平行于所述衬底延伸。

在其他特征中,所述上部和所述基部形成径向内侧台阶状表面。所述径向内侧台阶状表面(i)位于介电部件的凸缘上,并接收所述介电部件的所述凸缘,以及(ii)面对所述介电部件的径向外侧表面。

在其他特征中,所述上部和所述基部形成设置在所述第一底表面的径向外侧部分的径向内侧台阶状表面。所述径向内侧台阶状表面朝内延伸至介于所述径向外侧表面与所述顶表面之间的所述环状主体中。

在其他特征中,一种衬底处理系统包括:所述等离子体排除区域环;以及所述衬底。所述等离子体排除区域环的所述径向外侧表面将处理气体引导朝向所述衬底的周围边缘。

在其他特征中,所述等离子体排除区域环包括缺口。所述缺口具有与所述衬底的对准缺口相同的轮廓。

在其他特征中,一种用于衬底处理系统的等离子体排除区域环被提供且被配置成处理衬底。所述等离子体排除区域环包括环状主体和等离子体排除区域环缺口。所述环状主体限定:径向内侧表面;径向外侧表面;顶表面,其从所述径向内侧表面径向朝外延伸;第一底表面,其从所述径向外侧表面径向朝内延伸;以及第二底表面,其从所述第一底表面径向朝内延伸。所述第二底表面与所述第一底表面是不同角度。等离子体排除区域环缺口从所述径向外侧表面和所述第一底表面朝内延伸至所述环状主体中。所述等离子体排除区域环缺口被配置成在所述衬底的对准缺口上方延伸,与所述对准缺口相对,并且与所述对准缺口对准。

在其他特征中,所述第一底表面是倾斜的,且以锐角从所述第二底表面延伸至所述径向外侧表面。

在其他特征中,所述等离子体排除区域环缺口包括单一凹陷表面,所述凹陷表面被配置成与所述衬底的所述对准缺口相对。

在其他特征中,所述等离子体排除区域环缺口具有从径向最内侧边缘至径向最外侧边缘的变化深度。

在其他特征中,所述等离子体排除区域环缺口具有从径向最内侧边缘至径向最外侧边缘的不变深度。

在其他特征中,所述等离子体排除区域环缺口包括:第一凹陷表面和第二凹陷表面;所述第一凹陷表面以相对于所述衬底的锐角延伸;所述第二凹陷表面平行于所述衬底延伸;以及所述第一表面和所述第二表面中的至少一者被配置成与所述衬底的所述对准缺口相对。

根据详细描述、权利要求和附图,本公开内容的适用性的进一步的范围将变得显而易见。详细描述和具体示例仅用于说明的目的,并非意在限制本公开的范围。

附图说明

根据详细描述和附图将更充分地理解本公开,其中:

图1是根据本公开的示例性衬底处理系统的功能框图,其中该衬底处理系统包括衬底支撑件;

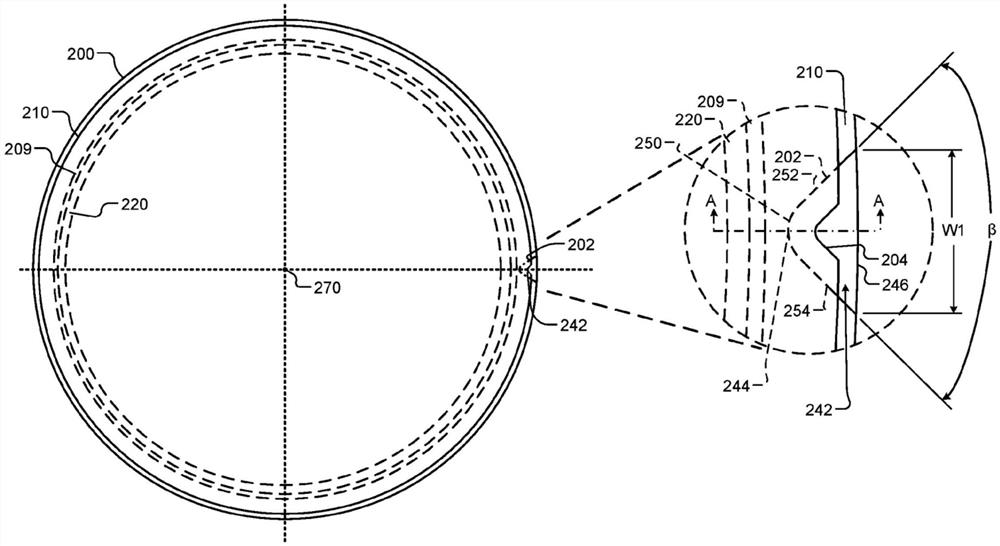

图2是根据本公开的等离子体排除区域(PEZ)环的仰视图,其中该PEZ环包括具有变化深度的单段式PEZ环缺口;

图3是图2的PEZ环的一部分的仰视图,其中描绘了PEZ环缺口轮廓和相应的晶片缺口轮廓;

图4是在图2的截面线A-A处的图2的PEZ环的一部分的横截面图;

图5是根据本公开的另一PEZ环的仰视图,其中该PEZ环包括多段式PEZ环缺口;

图6是在图5的截面线B-B处的图5的PEZ环的一部分的横截面图;

图7是根据本公开的PEZ环的仰视图,其中该PEZ环包括具有不变深度的单段式PEZ环缺口;

图8是在图7的截面线C-C处的图7的PEZ环的一部分的横截面图。

在附图中,可以重复使用附图标记来标识相似和/或相同的元件。

具体实施方式

衬底处理系统可包括一个或更多PEZ环。上PEZ环可被设置在晶片的外缘上,并在晶片的周缘处及其径向内侧限定蚀刻或沉积轮廓。上PEZ环可包括平行于晶片的上表面延伸的平坦底表面。晶片可包括晶片对准缺口(后续称为“晶片缺口”),其中该晶片缺口被用作用于晶片对准的参考点。在晶片缺口处的处理行为可能会与晶片的其他区域处的处理行为不同。举例来说,在蚀刻期间,在晶片缺口处会具有比晶片的其他区域更快的材料移除速率。作为另一示例,在沉积期间,晶片缺口处的粘附性可能会比晶片的其他区域更差,从而导致沉积较少材料。因此,位于晶片缺口处和/或附近的表面形貌可能会与晶片的其他区域(其相对于晶片中心在相同的径向距离处)的表面形貌不同。如果晶片缺口附近的沉积膜覆盖率与晶片的其他区域的覆盖率不同,则会影响晶片缺口处及附近的管芯。举例来说,在晶片与晶片的接合处理中,在晶片缺口附近可能会产生空洞。因此,在缺口区域中的管芯被废弃而导致低良率。

本文所阐述的示例包括PEZ环,其中所述PEZ环具有倾斜底表面及各自的缺口(称为PEZ环缺口),以提高晶片缺口处及附近的等离子体扩散,从而改善蚀刻速率和沉积速率的均匀性。PEZ环缺口与相应晶片缺口具有相同、或相似的轮廓,且PEZ环缺口大于晶片缺口,以在晶片缺口处及附近提供一致的蚀刻以及沉积性能,从而提高良率。PEZ环缺口具有一个或更多凹陷段,且这些凹陷段具有相应的深度。如在下文进一步描述的,所述深度可以是不变的或变化的。PEZ环缺口与晶片缺口对准,且增加晶片缺口处以及附近的蚀刻和沉积,从而改善晶片缺口处以及附近的蚀刻和沉积均匀性。

图1显示了包括PEZ环101的衬底处理系统100,其中PEZ环101具有倾斜的底表面。PEZ环101包括PEZ环缺口,其中PEZ环缺口的示例被显示于图2至图8中。仅举例而言,衬底处理系统100可用于执行使用RF等离子体的蚀刻和/或沉积处理、和/或其他合适的衬底处理。PEZ环101系用于控制衬底周缘处的蚀刻速率和/或沉积速率。PEZ环101以及本文所公开的其他PEZ环可各自包括由铝氧化物、铝氮化物、硅、硅碳化物、硅氮化物、和/或氧化钇所形成的环状主体。

衬底处理系统100包括处理室102,处理室102包围衬底处理系统100的部件并包含RF等离子体。处理室102包括上电极104和衬底支撑件106,该衬底支撑件可以是静电卡盘(ESC)。在操作期间,衬底108布置在衬底支撑件106上。虽然作为示例示出了特定衬底处理系统100和处理室102,但是本公开的原理可以应用于其他类型的衬底处理系统和室,例如原位产生等离子体的衬底处理系统、实现远程等离子体产生和输送(例如,使用等离子体管、微波管)的衬底处理系统等等。

仅举例而言,上电极104可以包括PEZ环101和气体分配设备,例如喷头109,其引入和分配工艺气体。喷头109可包括杆部,杆部包括连接到处理室102的顶部表面的一端。基部部分通常为圆柱形,并且在与处理室102的顶部表面间隔开的位置处从杆部的相对端径向向外延伸。喷头109的基部部分的面向衬底的表面或面板包括让工艺气体或清扫气体流过的孔。替代地,上电极104可包括传导板,并且可以以另一种方式引入工艺气体。

衬底支撑件106包括用作下电极的导电基板110。基板110支撑顶板112,该顶板112可由陶瓷所形成。在一些示例中,顶板112可包括一个或更多加热层,例如陶瓷多区域加热板。该一个或更多加热层可以包括一个或更多加热元件,例如导电轨迹,其将在下文进一步描述。

接合层114被设置在顶板112与基板110之间,并将两者接合。基板110可以包括用于使冷却剂流过基板110的一个或多个冷却剂通道116。衬底支撑件106可包括边缘环118,边缘环118布置成围绕衬底108的外缘。

RF产生系统120产生RF电压并将RF电压输出到上电极104和下电极(例如,衬底支撑件106的基板110)中的一个。上电极104和基板110中的另一个可以是DC接地的、AC接地的或浮动的。仅举例而言,RF产生系统120可包括RF电压产生器122,其产生RF电压,该RF电压由匹配和分配网络124馈送到上电极104或基板110。在其他示例中,可以感应或远程生成等离子体。尽管如为了示例目的所示出的,RF产生系统120对应于电容耦合等离子体(CCP)系统,但是本公开的原理也可以在其他合适的系统中实现,例如,仅举例而言,在变压器耦合等离子体(TCP)系统、CCP阴极系统、远程微波等离子体产生和输送系统等中实现。

气体输送系统130包括一个或多个气体源132-1、132-2、…和132-N(统称为气体源132),其中N是大于零的整数。气体源提供一种或多种气体混合物。气体源还可以供应清扫气体。也可以使用汽化的前体。气体源132通过阀134-1、134-2、…和134-N(统称为阀134)和质量流量控制器136-1、136-2、…和136-N(统称为质量流量控制器136)与歧管140连接。歧管140的输出被供给到处理室102。仅举例而言,歧管140的输出被供给到喷头109。

温度控制器142可以连接到加热元件,例如布置在顶板112中的热控制元件(TCE)144。例如,加热元件可以包括但不限于对应于多区域加热板中的各个区域的大加热元件和/或跨多区域加热板的多个区域设置的微加热元件阵列。温度控制器142可以用于控制加热元件,以控制衬底支撑件106和衬底108的温度。

温度控制器142可以与冷却剂组件146连通以控制流过通道116的冷却剂流。例如,冷却剂组件146可以包括冷却剂泵和贮存器。温度控制器142操作冷却剂组件146以选择性地使冷却剂流过通道116以冷却衬底支撑件106。

阀150和泵152可用于从处理室102排空反应物。系统控制器160可用于控制衬底处理系统100的部件。一个或多个机械手170可用于将衬底输送到衬底支撑件106上,以及从衬底支撑件106去除衬底。例如,机械手170可在设备前端模块(EFEM)171与装载锁172之间、在装载锁与真空转移模块(VTM)173之间、在VTM 173与衬底支撑件106之间等传送衬底。虽然温度控制器142示出为单独的控制器,但是温度控制器142可以在系统控制器160内实现。在一些示例中,可以在顶板112和基板110之间,在接合层114的外缘周围提供保护性密封176。

衬底处理系统100可以包括对准器180,其用于将PEZ环101对准衬底108。这包括将PEZ环101的PEZ环缺口对准衬底108的对准缺口。可通过系统控制器160控制该对准,并且可控制各PEZ环以及对应衬底的对准。这对于包括多个衬底支撑件以及各自PEZ环的衬底处理系统和/或处理室是特别适合用于控制相应衬底的周缘处的蚀刻和沉积性能的。作为示例,系统控制器160可以确定PEZ环缺口与衬底108的该对准缺口之间的偏移,并转动PEZ环101或衬底108,使得PEZ环缺口与该对准缺口对准,如在下文进一步描述的。

图2至图4显示了包括PEZ环缺口202的PEZ环200,所述PEZ环缺口202对应于晶片206(显示于图3中)的晶片缺口204。PEZ环200包括上部205、基部207、最上部表面208、底(或最底部)表面209、倾斜底表面210、最内侧径向表面212、内侧径向表面214、径向最外侧表面216、以及外侧径向表面218。底表面209从内侧径向表面214径向延伸至倾斜底表面210。在一实施方案中,底表面209水平地和/或平行于晶片206的顶表面219延伸。PEZ环200的内侧底表面220从最内侧径向表面212径向朝外延伸至内侧径向表面214。PEZ环200的径向外侧顶表面222从径向最外侧表面216径向朝内延伸至外侧径向表面218。如一些转角所显示的,介于所述表面之间的转角可以是圆弧形的(rounded)。

内侧底表面220和内侧径向表面214形成缺口,该缺口接收介电部件224的一部分(或凸缘)223,其中该介电部件224可以是图1的喷头109的部件。介电部件224可以是环状板体,并包括用于将气体输送至处理室的孔洞。介电部件224将PEZ环200支撑和保持在原位。PEZ环200位于凸缘223上。外侧径向表面218和顶表面222与相对环230形成通道,其中工艺气体流动通过该通道,如箭头232所呈现的。工艺气体沿着外侧径向表面218、顶表面222以及径向最外侧表面216流动,并且被往下引导而朝向晶片206的外周缘。

虽然将PEZ环200及介电部件224显示为分离的部件,但在一实施方案中,PEZ环200和介电部件224被一体成型为单一部件。在另一实施方案中,PEZ环200被附接和/或熔接至介电部件224。例如,可将径向最内侧表面(例如,表面212、214及220)附接和/或熔接至介电部件224的径向最外侧表面。通过将PEZ环200和介电部件224提供为分离的部件,可替换PEZ环200而不替换介电部件224。这使操作成本降低,原因在于PEZ环200经常被暴露在苛刻的等离子体环境中,而介电部件224并不经历这种离子体环境。这是由于PEZ环200相对于介电部件224的布置,以及工艺气体沿着PEZ环200的外侧径向表面218的流动。当PEZ环200和介电部件224被附接和/或熔接在一起、或形成单一部件时,可将其统称为PEZ组件。所陈述的在PEZ环200与介电部件224之间的可能关系适用于本文所公开的其他PEZ环。

PEZ环缺口202具有凹陷段242,其中该凹陷段242具有从径向最内侧边缘244至径向最外侧表面216和/或径向最外侧边缘246逐步增加的变化深度D1。显示出了示例性变化深度D1,且该变化深度D1是在PEZ环200的径向横截面处从(i)参考线247至(ii)PEZ环缺口202的凹陷表面248测得的。PEZ环200的横截面垂直于最上部表面208和底(或最底部)表面209截取,例如图2的线A-A处的横截面。参考线247平行于、且包括切向交叉线(tangentialintersection line),其中该切向交叉线由平坦参考面的切向交叉点所提供,其中该平坦参考面切向延伸至该横截面处的倾斜底表面210。在一实施方案中,从PEZ环200的底部观察时,PEZ环缺口202的轮廓(或形状)匹配晶片缺口204的轮廓(或形状)。在所显示的示例中,PEZ环缺口202和晶片缺口204是V形的。PEZ环缺口202是较大的,但其尺寸正比于晶片缺口204的尺寸。PEZ环缺口202可具有弯曲内部(或表面)250、以及从弯曲内部250延伸至径向最外侧边缘246的两个侧向延伸表面252、254。弯曲内部250和侧向延伸表面252、254分别对应晶片缺口204的弯曲内部260和侧向延伸边缘262、264。PEZ环200的中心点与晶片206的中心点和垂直地呈一直线。在图2中,所述中心点都是以点270表示。PEZ环缺口202的宽度W是在径向最外侧边缘246处显示且测量,并正比于晶片缺口204的宽度W2。这些表面250、252、254的顶边缘可以是圆弧形的。

在(i)从底表面209且平行于底表面209延伸的侧向线300与(ii)倾斜底表面210之间存在角度α。在侧向线300与凹陷表面248之间存在角度β。作为示例,角度α可以是15-25°,而角度β可以是20-40°,但角度α、β可以是其他锐角。凹陷段242的径向最内侧边缘244(i)距离底表面209预定距离D2、和/或(ii)距离径向最外侧边缘246和/或径向最外侧表面216预定距离D3。距离D3可以包括径向最外侧边缘246的一部分或全部,其中径向最外侧边缘246可以是圆弧的。距离D2及D3中的每一者在沿着PEZ环缺口202的方位角方向中是不同的。在晶片206的径向最外侧边缘302与倾斜底表面210之间竖直地存在距离A。在凹陷表面248与晶片缺口204的径向最内侧边缘244之间竖直地存在距离B。在一实施方案中,距离B等于距离A。在底表面209与晶片206之间存在间隙G(例如,0.5至1.0微米(mm))。角度α、β的顶点位于同一点303处,并且距离晶片206的径向最外侧边缘302预定距离D4。角度α、β的顶点距离PEZ环200的径向最外侧表面216预定距离D5。

倾斜底表面210是倾斜的,使得介于倾斜底表面210与晶片206之间的距离从点303到径向最外侧表面216是增加的。与使用具有非倾斜底表面的PEZ环时相比,由于具有如角度α(称为PEZ环200的倾斜角)所表示的倾斜底表面210,在晶片缺口204处和附近发生增多的蚀刻和沉积。具有非倾斜底表面的PEZ环中的一示例是底表面209水平地延伸,直至到达PEZ环的径向最外侧竖直延伸表面。凹陷段242提高径向最外侧边缘302的径向内侧的蚀刻和沉积速率,使得从晶片206的径向最外侧边缘302至晶片缺口204的距离径向最外侧边缘302至少两倍径向深度RD处的蚀刻量和沉积量被维持在恒定速率。RD’表示从径向深度RD至位于凹陷段242的径向最内侧边缘244下方的点的距离,且RD’可大于或等于径向深度RD。作为示例,对于直径为300mm的晶片,径向深度RD可以是1.0至2.0mm。PEZ环缺口202被配置成提高径向深度RD处的蚀刻速率和/或沉积速率,使其与PEZ环200的外边缘和/或周缘处所提供的蚀刻速率和/或沉积速率是相同的,以在PEZ环缺口202处、以及远离PEZ环缺口202的区域中提供蚀刻和沉积速率均匀性。在径向深度RD’和/或PEZ环缺口202附近的较大径向深度处的蚀刻速率和/或沉积速率与PEZ环200的其他位置的蚀刻速率和/或沉积速率维持相同。

在一实施方案中,倾斜角α基于处理需求来确定,其中该处理需求例如为晶片的边缘或外周缘附近的蚀刻速率和/或沉积速率。由于PEZ环200的底表面如图显示是倾斜的,因此从晶片206的径向最外侧边缘302的径向内侧提供蚀刻速率以及沉积速率的最小和/或逐步变化。如图4中所显示的,角度β可基于下列因素来确定:处理需求、倾斜角α、距离A、晶片缺口204的径向最内侧边缘304的半径、底表面209的径向最外侧边缘的半径、和/或倾斜底表面210的点303处的径向最内侧边缘的半径。在一实施方案中,距离B被设定成与距离A相等,而角度β基于该关系来确定。接着,基于所确定的这些参数来形成凹陷段242。

径向最外侧表面216位于晶片206的径向最外侧边缘302的径向外侧。底表面209的最外侧边缘以及凹陷段242的径向最内侧边缘244位于晶片缺口204的径向内侧。图1的衬底支撑件106被配置成将晶片206相对于PEZ环200保持,使晶片缺口204位于PEZ环缺口202下方且与PEZ环缺口202对准。在该状态下,整个晶片缺口204位于凹陷段242下方。该对准被显示于图3中,其中晶片缺口204的弯曲内部260的最内侧点266与PEZ环缺口202的弯曲内部250的最内侧点268处于同一竖直面中。这可经由权利要求1的衬底处理系统的对准器180来实现,其中该对准器180可以由系统控制器160控制。

图5至6显示了包括多段式PEZ环缺口502的PEZ环500。除了PEZ环缺口502具有多个段,而该多个段具有不同角度的凹陷表面之外,PEZ环缺口502类似于图2至图4的PEZ环缺口202。虽然将PEZ环缺口502显示为具有两个凹陷表面504、506,但PEZ环缺口502可以具有两个或更多不同角度的两个或更多凹陷表面。

PEZ环500包括最上部表面508、底(或最底部)表面509、倾斜底表面510、最内侧径向表面512、内侧径向表面514、径向最外侧表面516、以及外侧径向表面518。底表面509从内侧径向表面514径向延伸至倾斜底表面510。在一实施方案中,底表面509水平地延伸。PEZ环500的内侧底表面520是从最内侧径向表面512径向朝外延伸至内侧径向表面514。PEZ环500的径向外侧顶表面522是从径向最外侧表面516径向朝内延伸至外侧径向表面518。如一些转角所显示的,介于所述表面之间的转角可以是圆弧的。在一实施方案中,介于表面506、516之间的转角并非为圆弧形的。介于表面506、516之间的角度可以是85°至95°。

内侧底表面520和内侧径向表面514形成缺口,该缺口接收一部分(或凸缘),例如图4中显示的凸缘223。PEZ环500位于该凸缘上。外侧径向表面518和顶表面522与相对环(例如图4的环230)形成通道,其中工艺气体流动通过该通道。工艺气体沿着外侧径向表面518、顶表面522、以及径向最外侧表面516流动,并且被往下引导而朝向晶片206的外周缘。

PEZ环缺口502具有凹陷段542。凹陷段542包括凹陷表面504、506。凹陷段542的深度从径向最内侧边缘544逐步增加至凹陷表面506,而在凹陷表面506处凹陷段542的深度逐步减低至径向最外侧表面516。显示出示例性的变化深度D1。深度D1可在PEZ环500的径向横截面处从(i)参考线545至(ii)下列一者测量:(a)PEZ环缺口502的凹陷表面504、或(b)PEZ环缺口502的凹陷表面506,具体取决于沿着平面545测量深度D1的位置。PEZ环500的横截面垂直于最上部表面508以及底(或最底部)表面509截取,例如图5的线B-B处的横截面。参考线545平行于且包括切向交叉线,其中该切向交叉线由平坦参考面的切向交叉点所提供,其中该平坦参考面切向延伸至该横截面处的倾斜底表面510。

在一实施方案中,从PEZ环500的底部观察时,PEZ环缺口502的轮廓(或形状)匹配晶片缺口204的轮廓(或形状)。在所显示的示例中,PEZ环缺口502和晶片缺口204是V形的。PEZ环缺口502是较大的,但其尺寸正比于晶片缺口204的尺寸。PEZ环缺口502可以具有弯曲内部(或表面)550以及从弯曲内部550延伸至径向最外侧边缘546的两个侧向延伸表面552、554。侧向延伸表面552、554的示例性竖直轮廓被显示于图4中。侧向延伸表面552、554可具有不同形状的其他竖直轮廓,其中可将所述轮廓进行调整,以调整蚀刻以及沉积的量。弯曲内部550以及侧向延伸表面552、554分别对应于图3中显示的晶片缺口204的弯曲内部260以及侧向延伸边缘262、264。凹陷表面504的宽度W3在边缘555处显示且测量,其中凹陷表面504与凹陷表面506在边缘555处相交。宽度W4在径向最外侧边缘546处显示且测量,并且正比于晶片缺口204的宽度W2(显示于图3中)。这些表面550、552、554的顶边缘可以是圆弧形的。

在(i)从底表面509且平行于底表面509延伸的侧向线600与(ii)倾斜底表面510之间存在角度α。在侧向线600与凹陷表面504之间存在角度β。表面506可平行于侧向线600且平行于晶片506的顶表面219延伸。在一实施方案中,这些表面506和509水平地延伸。

作为示例,角度α可以是15-25°,而角度β可以是20-40°,但角度α、β可以是其他锐角。凹陷段542的径向最内侧边缘544距离底表面509预定距离D6。距离D5是可调整的,从而调整凹陷表面504的宽度W5。距离D6和宽度W5中的每一者在沿着PEZ环缺口502的方位角方向中是不同的。在晶片206的径向最外侧边缘302与倾斜底表面510之间竖直地存在距离A。在凹陷表面504与晶片缺口204的径向最内侧边缘244之间竖直地存在距离B。在一实施方案中,距离B等于距离A。在底表面209与晶片206之间存在间隙G。角度α、β的顶点位于同一点604处,并且距离晶片206的径向最外侧边缘302预定距离D7。角度α、β的顶点距离PEZ环500的径向最外侧表面516预定距离D8。

凹陷表面506的宽度W6被显示且是可调整的。在所显示的示例中,晶片206的径向最外侧边缘302位于凹陷表面506下方,而晶片缺口204的径向最内侧边缘304位于凹陷表面504下方。在另一实施方案中,径向最外侧边缘302和径向最内侧边缘304两者均位于凹陷表面504下方。在另一实施方案中,径向最外侧边缘302和径向最内侧边缘304两者均位于凹陷表面506下方。

边缘555(凹陷表面504与凹陷表面506相交处)可涉及一边缘,其中在该边缘处增加凹陷段542的深度对于。在凹陷表面506下方的晶片206的区域中的蚀刻和/或沉积速率是影响最小或无影响的。例如,如果凹陷表面504侧向延伸至径向最外侧表面516因而去除凹陷表面506时,则相应的蚀刻和/或沉积速率会受到最小影响或不受影响的。这不同于改变径向最外侧边缘302的径向内侧的凹陷表面504的角度和/或形状,改变该角度和/或形状会显著地改变在凹陷表面504下方的晶片206的区域中的蚀刻和沉积速率。

凹陷段542提高径向最外侧边缘302的径向内侧的蚀刻和沉积速率,使得从晶片206的径向最外侧边缘302至晶片缺口204的距离径向最外侧边缘302至少两倍径向深度RD处的蚀刻量和沉积量被维持在恒定速率。RD’表示从径向深度RD至位于凹陷段542的径向最内侧边缘544下方的点的距离,且RD’可大于或等于径向深度RD。作为示例,径向深度RD可以是1.0至2.0mm。

在一实施方案中,倾斜角α基于处理需求来确定,其中该处理需求例如为晶片的边缘或外周缘附近的蚀刻速率或沉积速率。由于PEZ环500的底表面是如图显示地为倾斜的,因此从晶片206的径向最外侧边缘302的径向内侧提供蚀刻速率及沉积速率的最小和/或逐步变化。如图6中所显示,角度β可基于下列因素来确定:处理需求、倾斜角α、距离A、晶片缺口204的径向最内侧边缘304的半径、底表面509的径向最外侧边缘的半径、和/或倾斜底表面510的点604处的径向最内侧边缘的半径。在一实施方案中,距离B被设定成与距离A相等,而角度β基于该关系来确定。接着,基于所确定的这些参数而形成凹陷段542。

径向最外侧表面516位于晶片206的径向最外侧边缘302的径向外侧。底表面509的最外侧边缘和凹陷段542的径向最内侧边缘544位于晶片缺口204的径向内侧。图1的衬底支撑件106被配置成将晶片206相对于PEZ环500保持,使晶片缺口204位于PEZ环缺口502下方且与PEZ环缺口502对准。整个晶片缺口204位于凹陷段542下方。

图7至8显示了包括PEZ环缺口702的PEZ环700,其中PEZ环缺口702具有单一凹陷段704,而凹陷段704具有不变深度D2。由于PEZ环700具有不变深度的单一凹陷段缺口,故PEZ环700比图5至图6的PEZ环500更易于制造。PEZ环缺口702类似于图2至图6的PEZ环缺口202和502,不同的是PEZ环缺口702具有单一凹陷段,且该单一凹陷段具有凹陷表面及不变深度D2。

PEZ环700包括最上部表面708、底(或最底部)表面709、倾斜底表面710、最内侧径向表面712、内侧径向表面714、径向最外侧表面716、以及外侧径向表面718。底表面709从内侧径向表面714径向延伸至倾斜底表面710。在一实施方案中,底表面709水平地延伸。PEZ环700的内侧底表面720从最内侧径向表面712径向朝外延伸至内侧径向表面714。PEZ环700的径向外侧顶表面722从径向最外侧表面716径向朝内延伸至外侧径向表面718。如图所示,介于所述表面之间的转角可以是圆弧形的。内侧底表面720和内侧径向表面714形成缺口,该缺口接收一部分(或凸缘),例如图4中显示的凸缘223。PEZ环700位于该凸缘上。外侧径向表面718和顶表面722与相对环(例如图4的环230)形成通道,其中工艺气体流动通过该通道。工艺气体沿着外侧径向表面718、顶表面722、以及径向最外侧表面716流动,并且被往下引导而朝向晶片206的外周缘。

凹陷段704包括凹陷表面724。凹陷段704的深度D2从径向最内侧边缘744至径向最外侧边缘746和/或径向最外侧表面716维持相同。因此,深度D2为不变的,并且可以在PEZ环700的径向横截面处从(i)参考线747至(ii)凹陷表面724测量。PEZ环700的横截面垂直于最上部表面708和底(或最底部)表面709截取,例如图7的线C-C处的横截面。参考线747平行于且包括切向交叉线,其中该切向交叉线由平坦参考面的切向交叉点提供,其中该平坦参考面切向延伸至该横截面处的倾斜底表面710。

在一实施方案中,从PEZ环700的底部观察时,PEZ环缺口702的轮廓(或形状)匹配晶片缺口204的轮廓(或形状)。在所显示的示例中,PEZ环缺口702和晶片缺口204是V形的。PEZ环缺口702是较大的,但其尺寸正比于晶片缺口204的尺寸。PEZ环缺口702可具有弯曲内部(或表面)750,以及从弯曲内部750延伸至径向最外侧边缘746的两个侧向延伸表面752、754。弯曲内部750和侧向延伸表面752、754分别对应于图3中显示的晶片缺口204的弯曲内部260和侧向延伸边缘262、264。凹陷段704的宽度W7在径向最外侧边缘746处显示且测量,并且正比于晶片缺口204的宽度W2(如图3中所显示的)。这些表面750、752、754的顶边缘可以是圆弧形的。

在(i)从底表面709且平行于底表面709延伸的侧向线800与(ii)倾斜底表面710之间存在角度α。在侧向线800与凹陷表面724之间存在角度β。作为示例,角度α可以是15-25°,而角度β可等于角度α、或与角度α相差在预定范围内。在该示例中,凹陷表面724平行于倾斜底表面710。角度α、β可以是其他锐角。凹陷段704的径向最内侧边缘744距离底表面709预定距离D6。距离D6是可调整的,从而调整凹陷段704的宽度W8。距离D6和宽度W8中的每一者在沿着PEZ环缺口702的方位角方向中是不同的。

在晶片206的径向最外侧边缘302与倾斜底表面710之间竖直地存在距离A。在凹陷表面724与晶片缺口204的径向最内侧边缘304之间存在距离B。在一实施方案中,距离B等于距离A。在底表面709与晶片206之间存在间隙G。角度α、β的顶点804、806位于不同点处。顶点804距离晶片206的径向最外侧边缘302预定距离D7。顶点804距离PEZ环700的径向最外侧表面716预定距离D8。在所显示的示例中,晶片206的径向最外侧边缘302和径向最内侧边缘304位于凹陷表面724下方。

凹陷段704提高径向最外侧边缘302的径向内侧的蚀刻和沉积速率,使得从晶片206的径向最外侧边缘302至晶片缺口204的距离径向最外侧边缘302至少两倍径向深度RD处的蚀刻量和沉积量被维持在恒定速率。RD’表示从径向深度RD至位于凹陷段704的径向最内侧边缘744下方的点的距离,且RD’可大于或等于径向深度RD。作为示例,径向深度RD可以是1.0至2.0mm。

在一实施方案中,倾斜角α基于处理需求来确定,其中该处理需求例如为晶片的边缘或外周缘附近的蚀刻速率和/或沉积速率。由于PEZ环700的底表面如图显示为倾斜的,因此从晶片206的径向最外侧边缘302的径向内侧提供蚀刻速率和沉积速率的最小和/或逐步变化。如图8中所显示,角度β可基于下列因素来确定:处理需求、倾斜角α、距离A、晶片缺口204的径向最内侧边缘304的半径、底表面709的径向最外侧边缘的半径、和/或倾斜底表面710的点804处的径向最内侧边缘的半径。在一实施方案中,角度β等于角度α。接着,基于所决定的这些参数而形成凹陷段704。

径向最外侧表面716位于晶片206的径向最外侧边缘302的径向外侧。底表面709的最外侧边缘、以及凹陷段704的径向最内侧边缘744位于晶片缺口204的径向内侧。图1的衬底支撑件106被配置成将晶片206相对于PEZ环700保持,使晶片缺口204位于PEZ环缺口702下方且与PEZ环缺口702对准。整个晶片缺口204位于凹陷段704下方。

本文所公开的PEZ环缺口对在晶片缺口处及附近的等离子体扩散提供渐变式的蚀刻和沉积轮廓控制,以实现晶片缺口处及附近的较均匀蚀刻和沉积性能。这包括在晶片缺口处从晶片的最外侧边缘径向朝内提供逐步的等离子体变化,而不是急剧的等离子体扩散变化。这不同于具有非倾斜和无凹口基部的PEZ环,其中从晶片的外边缘径向朝内存在急剧的等离子体扩散降低。

前面的描述本质上仅仅是说明性的,并且绝不旨在限制本公开、其应用或用途。本公开的广泛教导可以以各种形式实现。因此,虽然本公开包括特定示例,但是本公开的真实范围不应当被如此限制,因为在研究附图、说明书和所附权利要求时,其他修改将变得显而易见。应当理解,在不改变本公开的原理的情况下,方法中的一个或多个步骤可以以不同的顺序(或同时地)执行。此外,虽然每个实施方案在上面被描述为具有某些特征,但是相对于本公开的任何实施方案描述的那些特征中的任何一个或多个,可以在任何其它实施方案的特征中实现和/或与任何其它实施方案的特征组合,即使该组合没有明确描述。换句话说,所描述的实施方案不是相互排斥的,并且一个或多个实施方案彼此的置换保持在本公开的范围内。

使用各种术语来描述元件之间(例如,模块之间、电路元件之间、半导体层之间等)的空间和功能关系,各种术语包括“连接”、“接合”、“耦合”、“相邻”、“紧挨”、“在...顶部”、“在...上面”、“在...下面”和“设置”。除非将第一和第二元件之间的关系明确地描述为“直接”,否则在上述公开中描述这种关系时,该关系可以是直接关系,其中在第一和第二元件之间不存在其它中间元件,但是也可以是间接关系,其中在第一和第二元件之间(在空间上或功能上)存在一个或多个中间元件。如本文所使用的,短语“A、B和C中的至少一个”应当被解释为意味着使用非排他性逻辑或(OR)的逻辑(A或B或C),并且不应被解释为表示“A中的至少一个、B中的至少一个和C中的至少一个”。

在一些实现方案中,控制器是系统的一部分,该系统可以是上述示例的一部分。这样的系统可以包括半导体处理设备,半导体处理设备包括一个或多个处理工具、一个或多个室、用于处理的一个或多个平台、和/或特定处理部件(晶片基座、气体流系统等)。这些系统可以与用于在半导体晶片或衬底的处理之前、期间和之后控制它们的操作的电子器件集成。电子器件可以被称为“控制器”,其可以控制一个或多个系统的各种部件或子部件。根据处理要求和/或系统类型,控制器可以被编程以控制本文公开的任何工艺,包括处理气体的输送、温度设置(例如加热和/或冷却)、压力设置、真空设置、功率设置、射频(RF)产生器设置、RF匹配电路设置、频率设置、流率设置、流体输送设置、位置和操作设置、晶片转移进出工具和其他转移工具和/或与具体系统连接或通过接口连接的装载锁。

从广义上讲,控制器可以定义为电子器件,电子器件具有接收指令、发出指令、控制操作、启用清洁操作、启用端点测量等的各种集成电路、逻辑、存储器和/或软件。集成电路可以包括存储程序指令的固件形式的芯片、数字信号处理器(DSP)、定义为专用集成电路(ASIC)的芯片、和/或执行程序指令(例如,软件)的一个或多个微处理器或微控制器。程序指令可以是以各种单独设置(或程序文件)的形式发送到控制器的指令,单独设置(或程序文件)定义用于在半导体晶片或系统上或针对半导体晶片或系统执行特定工艺的操作参数。在一些实施方案中,操作参数可以是由工艺工程师定义的配方的一部分,以在一或多个(种)层、材料、金属、氧化物、硅、二氧化硅、表面、电路和/或晶片的管芯的制造期间完成一个或多个处理步骤。

在一些实现方案中,控制器可以是与系统集成、耦合到系统、以其它方式联网到系统或其组合的计算机的一部分或耦合到该计算机。例如,控制器可以在“云”中或是晶片厂(fab)主机系统的全部或一部分,其可以允许对晶片处理的远程访问。计算机可以实现对系统的远程访问以监视制造操作的当前进展、检查过去制造操作的历史、检查多个制造操作的趋势或性能标准,改变当前处理的参数、设置处理步骤以跟随当前的处理、或者开始新的工艺。在一些示例中,远程计算机(例如服务器)可以通过网络(其可以包括本地网络或因特网)向系统提供工艺配方。远程计算机可以包括使得能够输入或编程参数和/或设置的用户界面,然后将该参数和/或设置从远程计算机发送到系统。在一些示例中,控制器接收数据形式的指令,其指定在一个或多个操作期间要执行的每个处理步骤的参数。应当理解,参数可以特定于要执行的工艺的类型和工具的类型,控制器被配置为与该工具接口或控制该工具。因此,如上所述,控制器可以是例如通过包括联网在一起并朝着共同目的(例如本文所述的工艺和控制)工作的一个或多个分立的控制器而呈分布式。用于这种目的的分布式控制器的示例是在与远程(例如在平台级或作为远程计算机的一部分)的一个或多个集成电路通信的室上的一个或多个集成电路,其组合以控制在室上的工艺。

示例系统可以包括但不限于等离子体蚀刻室或模块、沉积室或模块、旋转漂洗室或模块、金属电镀室或模块、清洁室或模块、倒角边缘蚀刻室或模块、物理气相沉积(PVD)室或模块、化学气相沉积(CVD)室或模块、原子层沉积(ALD)室或模块、原子层蚀刻(ALE)室或模块、离子注入室或模块、轨道室或模块、以及可以与半导体晶片的制造和/或制备相关联或用于半导体晶片的制造和/或制备的任何其它半导体处理系统。

如上所述,根据将由工具执行的一个或多个处理步骤,控制器可以与一个或多个其他工具电路或模块、其它工具部件、群集工具、其他工具接口、相邻工具、邻近工具、位于整个工厂中的工具、主计算机、另一控制器、或在将晶片容器往返半导体制造工厂中的工具位置和/或装载口运输的材料运输中使用的工具通信。

- 用于处理运动的成件货物的设备和方法,具有用于处理运动的成件货物的设备的输送、处理和/或包装机组

- 具有环-柱双阳极结构的双电离模式等离子体点火器的点火方法

- 用于晶片的共晶键合的方法和晶片复合体

- 具有高沉积环及沉积环夹具的处理配件

- 用于斜面蚀刻器的下等离子体排除区域环

- 具有用于排放晶片边缘气体的流动路径的排除环