验证方法及相关装置

文献发布时间:2023-06-29 06:30:04

技术领域

本申请涉及软件技术领域,尤其涉及一种验证方法及相关装置。

背景技术

随着软件技术的不断发展,软件可以实现的功能越来越多,这给人们的生活带来了极大的便利。但是,软件存在被篡改的风险,这容易导致该软件无法正常运行,甚至导致用户的敏感信息泄露。采用软件防篡改技术可以有效降低软件被篡改的风险。

例如,可以利用一个可信的远程验证者对不可信平台上运行的软件进行验证。可信的远程验证者对不可信平台上运行的软件提出完整性验证请求。软件根据收到的完整性验证请求进行校验和计算,并将校验和发送给远程验证者。远程验证者确定校验和与其预先存储的预期值一致,则确定该软件没有被篡改。

上述方法虽然可以有效降低软件被篡改的风险,但是需要一个可信的远程验证者对软件的完整性进行验证,便捷度不高。而且,在远程验证者提出完整性验证请求之前,远程验证者不会对软件进行验证,因此,上述方法很难及时发现软件是否被篡改,敏感度不高。

发明内容

本申请提供了一种验证方法及相关装置,实现了在执行函数的过程中通过内部校验单元(inner checker,IC)校验该函数的完整性,从而能够及时发现针对该函数的攻击,提高了校验的敏感性,而且不需要其他可信的验证者。

第一方面,本申请提供了一种验证方法,包括:电子设备执行第一可执行文件中代码段的第一函数,第一函数包括第一内部校验单元(本申请中也称作IC1)。电子设备通过第一内部校验单元确定第一函数的第一校验值。电子设备通过第一内部校验单元从第一可执行文件的只读数据(rodata)段确定第一函数的第一校验预期值。电子设备基于第一校验预期值和第一校验值确定第一函数的完整性。

这样,在电子设备执行第一函数时,电子设备可以通过IC1对第一函数的完整性进行校验。一旦第一函数被篡改,IC1能够及时检测出第一函数的完整性受损进而做出相应的保护措施(例如,静默记录、修复受损代码片段或者停止运行软件,等等),提高了校验网络对于攻击的敏感性,降低了用户受到的损害。此外,由于第一校验预期值被填充在第一可执行文件的rodata段,因此,第一校验预期值的填充不会影响到第一函数的校验预期值,也不会影响第一可执行文件的代码段。

在一种可能的实施方式中,电子设备通过IC1确定第一函数的第一校验值的过程包括以下步骤:

(1)电子设备通过IC1从rodata段读取第一函数的第一元数据,第一元数据用于指示第一函数的位置信息,该第一函数的位置信息包括第一函数的起始存储地址和第一函数的数据长度。

(2)电子设备通过IC1基于第一元数据确定第一函数在第一可执行文件中的位置。

(3)电子设备通过IC1基于第一函数在第一可执行文件中的位置,读取第一函数并计算第一函数的第一校验值。其中,可以通过计算第一函数的哈希值确定第一校验值。

在另一种可能的实现方式中,电子设备通过IC1确定第一函数的第一校验值的过程包括如下步骤:

(1)电子设备通过IC1调用第一保护函数,其中,第一保护函数可以是sc_guard_self函数。

(2)电子设备通过第一保护函数从rodata段读取第一函数的第一元数据。

(3)电子设备通过第一保护函数基于第一元数据确定第一函数在第一可执行文件中的位置。

(4)电子设备通过第一保护函数基于第一函数在第一可执行文件中的位置,读取第一函数并计算第一函数的第一校验值。其中,可以通过计算第一函数的哈希值确定第一校验值。

在一种可能的实现方式中,第一可执行文件被划分为多个区域,一个外部校验单元(outer checker,OC)对应其中一个区域,该外部校验单元用于校验该外部校验单元所对应区域的完整性,该验证方法还包括:电子设备执行第一可执行文件中代码段的第二函数,第二函数包括第一外部校验单元(本申请中也称作OC1)。电子设备通过第一外部校验单元确定该多个区域中第一区域的完整性。

其中,电子设备通过第一外部校验单元确定该多个区域中第一区域的完整性可以包括:电子设备通过第一外部校验单元确定第一区域的第二校验值。电子设备通过第一外部校验单元从第一可执行文件的只读数据段确定第一区域的第二校验预期值。电子设备基于第二校验预期值和第二校验值确定第一区域的完整性。

这样,在电子设备执行第二函数的过程中,OC1可以对第一区域的完整性进行校验。由于每个OC都可以校验第一可执行文件中的其中一个区域的完整性,通过在软件程序中插入多个OC,可以实现对第一可执行文件完整性校验的高覆盖,甚至全覆盖。

在一种可能的实施方式中,电子设备通过第一外部校验单元确定第一区域的第二校验值的过程包括如下步骤:

(1)电子设备通过OC1从rodata段读取第一区域的第二元数据,第二元数据用于指示第一区域的位置信息,该第一区域的位置信息包括第一区域的起始存储地址和第一区域的数据长度。

(2)电子设备通过OC1基于第二元数据确定第一区域在第一可执行文件中的位置。

(3)电子设备通过OC1基于第一区域在第一可执行文件中的位置,读取第一区域中的数据并计算第一区域的第二校验值。其中,可以通过计算第一区域中数据的哈希值确定第二校验值。

在另一种可能的实现方式中,电子设备通过第一外部校验单元确定第一区域的第二校验值的过程包括如下步骤:

(1)电子设备通过OC1调用第二保护函数,其中,第二保护函数可以是sc_guard_me函数。

(2)电子设备通过第二保护函数从rodata段读取第一区域的第二元数据。

(3)电子设备通过第二保护函数基于第二元数据确定第一区域在第一可执行文件中的位置。

(4)电子设备通过第一保护函数基于第一区域在第一可执行文件中的位置,读取第一区域中的数据并计算第一区域的第二校验值。其中,可以通过计算第一区域中数据的哈希值确定第二校验值。

需要说明的是,在本申请中,上述验证方法中的元数据(例如,第一元数据、第二元数据)可以存储在第一可执行文件的代码段,也可以存储在第一可执行文件的rodata段。由于元数据需要在可执行文件生成之后才可以确定,因此,在编译阶段先用占位符替代元数据,在可执行文件生成之后再用元数据替换占位符。当占位符被存储在代码段时,搜索占位符并替换为元数据的过程中很容易对代码段中的代码造成损伤,修改原有代码的逻辑导致功能性异常,因此,本申请的部分实施例将元数据存储在rodata段,这样可以避免在元数据的填充过程中对代码段中的代码造成损害。

在一种可能的实现方式中,第一区域包括第一函数,当电子设备利用上述验证方法通过OC1确定第一区域完整时,电子设备可以确定第一函数完整,同时,电子设备还可以确定位于第一函数中的IC1完整。

这样,第一函数的完整性可以由IC1或OC1来完成校验,而IC1的完整性也可以通过OC1来校验,从而降低了第一函数被篡改的风险。此外,各个IC与各个OC之间可以通过这样的关系组成校验网络,降低软件程序被篡改的风险。

在一种可能的实现方式中,第一区域包括第二函数,当电子设备利用上述验证方法通过OC1确定第一区域完整时,电子设备可以确定第二函数完整,同时确定位于第二函数中的OC1完整。

这样,电子设备可以通过OC1对OC1的完整性进行自校验,即在上述验证方法中,OC1的完整性可以由OC1来完成校验,因此IC和OC组成的校验网络可以是成环的。

在一种可能的实现方式中,第一函数被划分为两个部分,第一区域包括第一函数的第一部分,第二区域包括第一函数的第二部分,其中,第二区域是第一可执行文件被划分成多个区域中的其中一个区域。在这种情况下,上述验证方法还包括:当电子设备通过OC1确定第一区域完整时,电子设备确定第一函数的第一部分完整。

在一些实施例中,电子设备执行第一可执行文件中代码段的第三函数,第三函数包括第二外部校验单元,即OC2。当电子设备通过OC2确定第二区域完整时,电子设备确定第一函数的第二部分完整。

在电子设备分别确定第一函数的第一部分和第二部分完整后,电子设备可以确定第一函数完整。

这样,电子设备也可以通过多个OC对函数的完整性进行校验。

在一种可能的实现方式中,当电子设备执行到校验单元时,电子设备还可以调用一个随机单元,该随机单元用于从所校验的函数或内存片段中确定一个取样片段,该取样片段用于计算该函数或内存片段的校验值。

这样,当校验单元所校验的函数或内存片段过长时,可以随机地对该函数或内存片段的取样片段计算校验值,不需要对整个函数或内存片段进行校验值计算,极大地降低了校验过程带来的能耗。此外,随机性的引入也增加了校验网络的复杂性,让攻击者更难确定校验网络的模型,从而降低了校验网络被篡改的风险。

在一种可能的实现方式中,当电子设备执行到校验单元时,电子设备还可以通过可信根模块对该校验单元进行二级校验,二级校验是电子设备通过可信根模块对该校验单元对应的以下任意一项或多项数据进行的完整性校验:元数据(例如,第一元数据、第二元数据,等等)、校验预期值(例如,第一校验预期值、第二校验预期值,等等)和保护函数(例如,第一保护函数、第二保护函数,等等)。

这样,可以通过可信根模块来确保保护函数以及元数据和校验预期值的完整性,确保保护函数、元数据以及校验预期值不会被篡改。

在一种可能的实现方式中,电子设备还可以在确定待执行的校验单元满足预设条件之后,确定执行该校验单元,即在满足预设条件时确定通过该校验单元确定该校验单元所校验的函数或内存片段的校验值。

这样,通过引入预设条件判决,可以以一定的随机概率来触发校验单元进行校验,降低了校验单元执行校验的频率,从而减少能量的损耗。同时,由于在校验单元的触发中引入了随机性,攻击者也更难确定校验网络,从而也降低了软件被篡改的风险。

在一些实施例中,还可以根据校验单元所校验的对象的重要程度设置不同的随机触发校验的频率,为重要的、高敏感的函数设置较高的随机校验触发频率,为不重要的、低敏感的函数设置较低的随机校验触发频率,从而对能耗进行更经济更高效的划分。

在一种可能的实现方式中,电子设备在确定第一函数完整性之后,还包括:当电子设备确定第一函数完整时,电子设备继续执行第一可执行文件。当电子设备确定第一函数非完整时,即第一函数受损时,电子设备停止执行第一可执行文件,并清空栈帧数据。

在一种可能的实现方式中,电子设备在确定第一区域完整性之后,还包括:当电子设备确定第一区域完整时,电子设备继续执行第一可执行文件。当电子设备确定第一区域非完整时,即第一区域受损时,电子设备停止执行第一可执行文件,并清空栈帧数据。

这样,在确保软件完整性的同时可以保证软件的正常运行。而在确定软件受到攻击后,可以通过及时的补救措施降低用户的受到损害的风险。

第二方面,本申请提供一种电子设备,包括:一个或多个处理器、一个或多个存储器。该一个或多个存储器与该一个或多个处理器耦合,该一个或多个存储器用于存储计算机程序代码,该计算机程序代码包括计算机指令,当该一个或多个处理器执行该计算机指令时,使得该电子设备执行上述任一方面任一项可能的实现方式中的验证方法。

第三方面,本申请提供了一种计算机可读存储介质,包括:计算机指令,当计算机指令在电子设备上运行时,使得电子设备执行上述任一方面任一项可能的实现方式中的验证方法。

第四方面,本申请提供了一种计算机程序产品,当计算机程序产品在计算机上运行时,使得计算机执行上述任一方面任一项可能的实现方式中的验证方法。

第五方面,本申请实施例的一种电子设备,该电子设备包括执行上述第一方面或者第一方面的任意一种可能的设计的方法的模块/单元;这些模块/单元可以通过硬件实现,也可以通过硬件执行相应的软件实现。

其中,第二方面至第五方面的有益效果,请参见第一方面的有益效果,不重复赘述。

附图说明

图1A至图1C为本申请实施例中提供的一种完整性自校验方法的校验网络示意图;

图2为本申请实施例中提供的一种待插入函数的选取方法示意图;

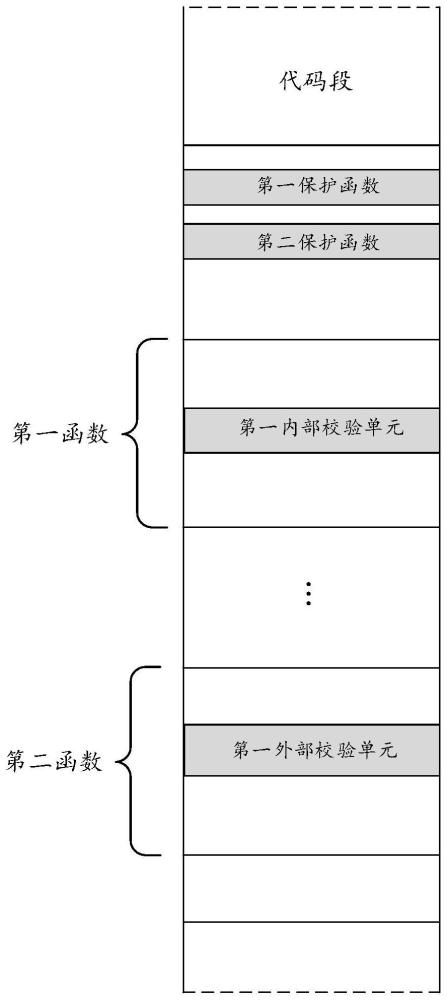

图3A为本申请实施例中提供的一种可执行文件的结构示意图;

图3B为本申请实施例中提供的一种可执行文件中校验单元的位置示意图;

图4A为本申请实施例中提供的低级虚拟机(low level virtual machine,LLVM)编译框架示意图;

图4B为本申请实施例中提供的一种编译系统的示意图;

图4C为本申请实施例中提供的一种混合校验单元指令与函数指令的方法示意图;

图5为本申请实施例中提供的一种验证方法的流程示意图;

图6为本申请实施例中提供的一种第一外部校验单元对第一区域进行完整性校验的方法流程示意图;

图7为本申请实施例中提供的一种电子设备基于随机单元确定第一区域的完整性的流程示意图;

图8为本申请实施例中提供的一种电子设备通过可信根模块对第一内部校验单元进行二级校验的流程示意图;

图9为本申请实施例中提供的一种电子设备根据待执行的校验单元与预设条件的关系决定是否执行该校验单元的流程示意图;

图10为本申请实施例中提供的一种电子设备的功能模块示意图;

图11为本申请实施例中提供的一种电子设备的硬件结构示意图。

具体实施方式

下面将结合附图对本申请实施例中的技术方案进行清楚、详尽地描述。其中,在本申请实施例的描述中,除非另有说明,“/”表示或的意思,例如,A/B可以表示A或B;文本中的“和/或”仅仅是一种描述关联对象的关联关系,表示可以存在三种关系,例如,A和/或B,可以表示:单独存在A,同时存在A和B,单独存在B这三种情况,另外,在本申请实施例的描述中,“多个”是指两个或多于两个。

以下,术语“第一”、“第二”仅用于描述目的,而不能理解为暗示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征,在本申请实施例的描述中,除非另有说明,“多个”的含义是两个或两个以上。

自校验(self-checksumming,SC)技术是一种在没有可信验证者的情况下,由软件完成对自身完整性校验的方法。通过在程序中嵌入多个校验单元(checkers),并利用该多个校验单元构建校验网络,SC可以实现对软件的完整性自校验。

下面结合图1A至图1C介绍本申请实施例中提供的一种完整性自校验方法。

如图1A所示,程序内存中的代码段片段中包括多个校验单元(例如,G1,G2,G3,G4,G5,等等)和多个安全敏感区域(例如C1,C2)。其中,G1和C2位于代码段的片段一,G2位于代码段的片段二,C1、G3和G4位于代码段的片段三,C1位于代码段的片段四,且片段四是片段三的一部分,G5位于代码段的片段五。每个校验单元可以针对一个代码片段进行校验(checksum)或修复(repair)。例如,G1可以对片段三进行校验,G2可以对片段五进行修复,G3可以对片段四进行修复,G4可以对片段一进行校验,G5可以对片段三进行校验。

其中,针对一个代码片段进行校验是验证该代码片段的完整性,即校验该代码片段是否被篡改。在校验该代码片段时,可以将该代码片段的哈希(hash)值作为该代码片段的校验和与该代码片段的完整性预期值相比较来判定该代码片段是否完整。当校验和与完整性预期值一致时,校验单元的校验结果是该代码片段完整,即该代码片段未被篡改,此时软件继续正常运行。当校验和与完整性预期值不一致时,校验单元的校验结果是该代码片段受损,即该代码片段已被篡改,此时校验单元会触发相应操作(例如,静默记录、修复受损代码片段、或停止运行软件,等等)。针对一个代码片段进行修复是指在受损代码片段被执行之前,校验单元可以利用预先存储在其他位置处的原始代码对受损代码片段进行修复,即将该受损代码片段替换为对应的原始代码片段。

基于上述多个校验单元之间的关系,可以构建出如图1B所示的校验网络。

如图1B所示,校验单元G1可以校验G3、C1和G4,校验单元G2可以修复G5,校验单元G3可以修复C1,校验单元G4可以校验G1和C2,校验单元G5可以校验G3、C1和G4。

在上述校验网络中,安全敏感区域C1如果遭到攻击,可以在C1被执行之前由校验单元G3对C1进行修复。此外,在校验单元G3对C1进行修复之前,校验单元G1和G5也可以对G3进行完整性校验。而且,在修复后的C1被执行之前,还可以由校验单元G1和G5对修复后的C1进行完整性校验。更进一步的,校验单元G1在被执行之前可以由校验单元G4进行校验,校验单元G5在被执行之前可以由校验单元G2对其进行修复。类似的,安全敏感区域C2的完整性可以由校验单元G4进行校验,而校验单元G4的完整性则可以由校验单元G1进行校验。这样,所有安全敏感区域都可以由校验单元保证其完整性,而且所有校验单元之间也可以构成一个校验网络,攻击者仅仅攻击校验网络中的一个或几个校验单元很难突破整个校验网络,实现对安全敏感区域中代码的篡改。

在上述校验网络中,校验单元G1和G4之间存在相互校验关系,即上述校验网络是有环的。理论上,采用上述完整性自校验方法,可以根据具体需求构建任意校验网络,但是,由于校验单元中校验函数的单向性,校验网络中不能存在两个校验单元互相校验的情况。下面具体解释校验函数的单向性。

示例性的,如图1C所示,程序内存中的代码段片段中包括多多个代码片段(例如,片段一、片段二,等等)。其中,片段一包括校验单元A,片段二包括校验单元B。校验单元A可以校验片段二,校验单元B可以校验片段一。校验单元A中还填充有预期值Y1,该预期值Y1是片段二的完整性预期值,当校验单元A对片段二进行校验时,计算片段二的校验和并与预期值Y1进行比较,当且仅当片段二的校验和与预期值Y1相同时,校验单元A确定片段二完整。类似的,校验单元B中还填充有预期值Y2,该预期值Y2是片段一的完整性预期值,那个校验单元B对片段一进行校验时,计算片段一的校验和并与预期值Y2进行比较,当且仅当片段一的校验和与预期值Y2相同时,校验单元B确定片段一完整。由于片段一的完整性预期值和片段二的完整性预期值需要在可执行文件生成后才可以获得的,而从程序源代码到可执行文件需要预编译、编译、汇编、链接这四个步骤,因此,预期值Y1和预期值Y2都是在生成可执行文件之后填充在代码段的校验单元中的。在完整性预期值的填充过程中,填充前后校验单元所在的代码片段对应的校验和不同。例如,根据前述校验关系,校验单元A需要填充预期值Y1,校验单元B需要填充预期值Y2。在将预期值Y1填充到校验单元A之后,校验单元A所在的片段一的校验和会发生变化,在这种情况下,若将变化后片段一的校验和作为预期值Y2填充到校验单元B,则校验单元B所在的片段二的校验和也会发生变化,变化后的片段二的校验值与校验单元A中填充的预期值Y1不符,因而校验单元A在对校验单元B所在的片段二进行校验时无法得到正确的校验结果。因此,采用上述完整性自校验方法时,校验单元中的校验函数具有单向性,基于校验单元构建的校验网络必须是无环的,不能存在两个校验单元互相校验的情况,也不能存在校验单元对自身校验的情况。

校验网络的无环特性意味着在该校验网络中,一定存在一个没有其他校验单元对其进行校验的校验单元,这个无法被校验的校验单元可以称为该校验网络的源点。倘若攻击者针对该校验网络中的源点进行攻击,该校验网络被突破的风险会显著提高。

由上述软件的完整性自校验方法可知,通过多个校验单元构建校验网络可以降低软件被篡改的风险,而且该方法不需要可信验证者,便捷度更高。但是,由于校验单元中的校验函数具有单向性,校验网络中必须是无环的,校验网络中的源点无法被校验,因此,上述完整性自校验方法无法实现对整个代码段的全覆盖。

由于校验单元的执行需要花费时间和资源,因此在代码段插入过多的校验单元会降低软件的性能。为了降低由于执行校验单元带来的性能损耗,本申请实施例中提供了一种低损耗的软件完整性自校验方法。低损耗的软件完整性自校验方法通过在多个执行频率较低的函数中嵌入的校验单元构建校验网络,以此降低校验单元的执行带来的损耗,同时也可以通过该校验网络降低软件被篡改的风险。

图2示出了待插入函数的选取方法示意图。函数的执行频率可以利用分析工具(profiling tools)计算得到。在确定所有函数的执行频率之后,可以按照执行频率由低到高的顺序在函数中插入校验单元,直至插入的校验单元的数目达到目标值(例如200)。

示例性的,如图2所示,软件源代码生成的可执行文件中包括多个函数(例如,F1、F2、F3、F4、F5、F6、F7,等等),这些函数均位于该可执行文件的代码段。利用分析工具(profiling tools)可以确定上述所有函数的执行频率从低到高分别是F1、F2、F3、F4、F5、F6、F7。其中,在可执行文件启动时以及执行过程中,函数F1从未被执行,函数F2至少被执行了一次。在选定待插入函数时,如果需要插入的校验单元至少有四个,即目标值为四,在这种情况下,剔除从未被执行过的函数(例如,F1),选定剩余函数中执行频率最低的四个函数(例如,F2、F3、F4和F5)作为待插入的函数。

在低损耗的软件完整性自校验方法中,校验网络的具体运行过程可以参考上述图1A至图1C所示实施例中的相关描述,此处不再赘述。

采用低损耗的软件完整性自校验方法可以在降低软件被篡改风险的同时,降低校验单元的执行带来的损耗。但是,由于校验单元被插入了执行频率低的函数中,校验单元的执行概率也较低,当校验单元所校验的函数或代码片段被篡改时,校验单元很难及时被触发,甚至可能无法被触发。此外,低损耗的软件完整性自校验方法也存在上述校验网络的无环特性,因此低损耗的软件完整性自校验方法也无法实现对整个代码段的全覆盖。

因此,本申请实施例中提供了一种验证方法,该验证方法将校验单元划分为内部校验单元(inner checker,IC)和外部校验单元(outer checker,OC)两大类。其中,IC的校验对象是IC所在的函数,这样,针对该函数的攻击能够及时被IC检测到,提高了对攻击的敏感性。OC的校验对象是内存片段,这样,可以通过多个OC实现对整个软件程序的高覆盖,甚至全覆盖。

为了能更清楚地介绍本申请实施例中提供的验证方法,首先要对可执行文件的结构进行介绍。

在本申请实施例中,可执行文件包括代码段(code section)、数据段(datasection)和只读数据段(read-only data section)。其中,代码段可用于保存程序源代码编译后的机器指令,代码段常见的名称后缀可以为“.code”或“.text”。数据段可用于保存已初始化的全局变量和局部静态变量,数据段的名称后缀可以为“.data”。只读数据段的名称后缀可以为“.rodata”或“.rdata”,只读数据段可用于存放只读数据,例如程序里面的只读变量和字符串常量。操作系统在加载过程中,可以将只读数据段的属性映射为只读,这样对于只读数据段的任何修改操作都会作为非法操作来处理,保证了程序的安全性。在本申请实施例中,只读数据段也可以称作rodata段。

应用于电子设备的可执行文件的格式可以包括可移植执行文件格式(portableexecutable,PE)和可执行链接格式(executable linkable format,ELF)。图3A示出了ELF可执行文件的结构。

如图3A所示,当可执行文件的格式为ELF时,可执行文件不仅包括代码段、数据段和只读数据段,还可以包括文件头(ELF header)、注释信息段(comment section)和其他信息段(other data section)。

其中,文件头用于描述整个文件的文件属性,包括文件是否可执行、是静态链接还是动态链接及入口地址、目标硬件、目标操作系统等信息,文件头还包括段表(sectiontable),该段表用于描述文件中各个段在文件中的偏移位置以及段的属性等信息。

注释信息段存放的是编译器版本信息,它的名称后缀可以是“.comment”。其他信息段用于保存与程序相关的其他信息。

图3B示出了本申请实施例中提供的一种可执行文件中校验单元的位置示意图。

如图3B所示,软件源代码生成的可执行文件的代码段包括多个函数(例如,第一函数、第二函数,等等)。其中,第一函数中插入有第一内部校验单元(IC1),IC1可以对第一函数的完整性进行校验。第二函数中插入有第一外部校验单元(OC1),OC1可以对第一可执行文件所占的内存中的某一个内存片段(例如,第一函数所在的第一区域)的完整性进行校验。在一些实施例中,代码段还可以包括一个或多个保护函数(例如,第一保护函数、第二保护函数,等等)。其中,第一保护函数可以被IC调用,用于确定IC所在函数的完整性。第二保护函数可以被OC调用,用于确定OC校验的内存片段的完整性。

下面介绍本申请实施例中提供的一种IC和OC的选取与注入方式。

因为IC和OC的选取与注入是在编译过程中体现的,所以首先需要介绍下本申请实施例中使用的低级虚拟机(low level virtual machine,LLVM)编译。

LLVM是一套编译器基础设施项目,是以C++写成的自由软件。LLVM包含一系列模块化的编译器组件和工具链,用来开发编译器前端和后端。图4A示出了LLVM编译框架示意图。如图4A所示,LLVM的编译框架包括前端(frontend)、中间语言(intermediaterepresentation,IR)层和后端。其中,IR层可以包括一些LLVM自带的插件(pass)和开发者自己编写的pass。由C++或C语言编写成的源代码经过LLVM的前端之后,被编译为IR文件,IR文件在IR层可以由LLVMpass进行分析(analysis)、优化(optimization)或者代码转换(transformation),LLVMpass输出的依旧是IR文件。IR文件经过LLVM后端可以生成适配于不同机器的可执行文件。

图4B示出了本申请实施例中提供的一种编译系统的示意图。

如图4B所示,编译系统10可以包括:LLVM前端、LLVMIR层、LLVM后端,以及自校验填充模块105。其中,LLVMIR层可以包括一个或多个插件(例如,混淆插件101、合并插件102、标记插件103、校验单元注入插件104,等等)。

示例性的,如图4B所示,编译系统10将软件源代码和保护函数的源代码编译为第一可执行文件的具体流程可以包括如下步骤:

1.LLVM前端将软件源代码编译为第一IR文件。

软件源代码经由LLVM前端编译之后,得到第一IR文件。

2.LLVM前端将保护函数的源代码编译为第二IR文件。

保护函数的源代码经由LLVM前端编译之后,得到第二IR文件。

3.LLVM前端将第一IR文件和第二IR文件发送至LLVMIR层。

在得到第一IR文件和第二IR文件之后,LLVM前端将第一IR文件和第二IR文件发送给LLVMIR层,由IR层的多个pass进行后续操作。

4.LLVMIR层的混淆插件101对第二IR文件进行混淆操作,得到第三IR文件。

在接收到第二IR文件之后,IR层的混淆插件(SCUtillpass)101对第二IR文件进行混淆操作,得到第三IR文件。

其中,针对第二IR文件的混淆操作可以提高保护函数的机密性,从而降低保护函数被攻击篡改的风险。

5.混淆插件101将第三IR文件发送至合并插件102。

在得到第三IR文件之后,混淆插件101可以将第三IR文件发送至合并插件102。

6.合并插件102将第一IR文件与第三IR文件合并为第四IR文件。

合并插件102在接收到第三IR文件和第一IR文件之后,将第一IR文件与第三IR文件合并,得到第四IR文件。

7.合并插件102将第四IR文件发送给标记插件103。

在得到第四IR文件之后,合并插件102可以将第四IR文件发送给标记插件(function annotation pass)103。

8.标记插件103针对第四IR文件进行标记操作,得到第五IR文件。

标记插件103可以接收合并插件102发送的第四IR文件,并针对第四IR文件进行标记操作,例如,将第四IR文件中IC的待插入的函数打上第一标记,将第四IR文件中OC的待插入函数打上第二标记。其中,IC的待插入函数可以是开发者指定的,例如,开发者可以在源代码编写过程中为一些函数贴上带有IC的标签,等等。IC的待插入函数也可以是标记插件根据IC覆盖率随机在第四IR文件中挑选的,例如,标记插件可以根据预先设置的IC覆盖率,利用均匀分布等分布在第四IR文件中挑选函数作为IC的待插入函数。

示例性的,标记插件在接收到第四IR文件之后,查找带有IC标签的函数,将其作为IC的待插入函数,为这些函数打上第一标记。此外,标记插件还可以基于给定的IC覆盖率,确定是否需要额外选择其他函数作为IC的待插入函数。当打上第一标记的函数比例高于或等于给定的IC覆盖率时,标记插件完成对IC的待插入函数的标记。当打上第一标记的函数比例低于给定的IC覆盖率时,标记插件可以利用均匀分布等方式在其余的函数中选择一些函数作为IC的待插入函数,并为这些函数打上第一标记。可以理解的是,IC的待插入函数也可以是由其他方式确定的,本申请在此不做限定。

OC的待插入函数可以由开发者指定,也可以由标记插件选择。

示例性的,OC的待插入函数可以基于函数调用图来挑选。标记插件可以基于第四IR文件构建第一函数调用图(call graph)。从指定函数(例如,带有main/start/init的函数)开始,沿着第一函数调用图进行广度优先搜索(Breadth-first search,BFS)遍历,即以指定函数作为第一函数调用图的根节点,沿着第一函数调用图的宽度遍历第一函数调用图的函数(节点),直至第一函数调用图的所有函数(节点)均被访问。在对第一函数调用图进行BFS遍历的过程中,标记插件记录所有函数的深度(depth)和出度(outdegree)。在确定第一函数调用图中所有函数的深度和出度后,标记插件可以对所有函数的深度和出度做归一化处理,并基于归一化的深度和出度对所有函数进行排序,将出度大、深度低的函数排在前面,将出度小、深度高的函数排在后面。例如,可以根据函数对应的D的数值按照从大到小的顺序排列所有函数,其中D的数值可以由公式(1)确定:

D=(1-depth)*w1+outdegree*w2 公式(1)

其中,在上述公式(1)中,depth为函数的深度,outdegree为函数的出度,w1和w2分别为两个加权系数,均为常数。

之后,标记插件可以根据给定的OC覆盖率确定OC的待插入函数的数目K,并在排序完毕的函数中选取前K个函数作为OC的待插入函数,并打上第二标记。

9.标记插件103将第五IR文件发送至校验单元注入插件104。

10.校验单元注入插件104根据标记在第五IR文件中注入校验单元。

校验单元注入插件(SCpass)104在接收到第五IR文件之后,可以根据第五IR文件中的标记在第五IR文件中注入相应的校验单元。

示例性的,校验单元注入插件可以识别带有第一标记的函数,并在该函数中插入一个IC。校验单元注入插件也可以识别带有第二标记的函数,并在该函数中插入一个OC。需要说明的是,在OC的注入过程中,假定OC的数目为K,即打有第二标记的OC的待插入函数的数目为K,校验单元注入插件可以将整个内存片段(例如,代码段、rodata段等等)划分为可重叠的N个部分,N>=K,并将N个部分随机映射到K个OC上。当N与K的值相等时,K个OC可以实现对整个内存片段的全覆盖校验。

由于校验单元对应的元数据和校验预期值需要在生成可执行文件之后才可以确定,因此,在编译阶段先用占位符代替元数据与校验预期值等数据,在生成可执行文件后再对占位符进行替换。在确定每个OC与其校验内存片段的对应关系后,校验单元注入插件可以为每一个IC和每一个OC在rodata段中对应维护一份占位符,该占位符用于在rodata段为每一个IC或OC所校验的函数或内存片段的元数据(例如,起始地址、数据长度,等等)和校验预期值预留一份存储空间。

在一些实施例中,为了能够增强校验单元的隐蔽性,可以将校验单元中的指令与待插入函数中的指令混合。

示例性的,如图4C所示,带有第一标记或第二标记的待插入函数F可以包括一个或多个基本块(例如,第一基本块、第二基本块、第三基本块、第四基本块、第五基本块,等等),每个基本块中可以包括一条或多条指令。函数F的所有基本块可以分为可选基本块集合和必要基本块集合,其中,必要基本块集合包括函数F中一定会执行的基本块(例如,第一基本块、第二基本块、第三基本块,等等),可选基本块集合包括函数F中选择执行的基本块(例如,第四基本块、第五基本块,等等)。

校验单元注入插件可以对待插入函数F的必要基本块集合进行遍历,获取函数指令集合。即将插入函数F中的校验单元中的指令可以组成校验单元指令集合,同样的,校验单元注入插件可以通过遍历该IC或OC获取校验单元指令集合。在确定函数指令集合和校验单元指令集合之后,可以按照函数指令集合和校验单元指令集合中指令执行的先后顺序,随机地在函数指令集合中插入校验单元指令。在指令插入前后,函数指令集合中指令执行的先后顺序不变,校验单元指令集合中指令执行的先后顺序也不变。

校验单元注入插件可以以图4C所示实施例中描述的方法,将各个IC或OC插入到对应的待插入函数中。这样,通过将函数指令与校验单元中的指令随机混合,可以提高校验单元的隐蔽性,使得攻击者更难确定校验单元的位置,从而降低软件被篡改的风险。

11.LLVMIR层将第六IR文件发送至LLVM后端。

12.LLVM后端基于第六IR文件生成可执行文件。

LLVM后端在接收到第六IR文件之后,可以基于第六IR文件生成可执行文件。其中,在基于第六IR文件生成的可执行文件中,占位符被放置在rodata段。

13.LLVM后端可以将可执行文件发送至自校验填充模块105。

14.自校验填充模块105将rodata段的占位符替换为元数据和校验预期值,生成第一可执行文件。

自校验填充(SCpatch)模块105在接收到可执行文件之后,可以获取各个IC或OC所校验的函数或内存片段的起始地址和数据长度,并计算相应的校验预期值。在确定各个校验单元所校验的函数或内存片段对应的元数据和校验预期值之后,自校验填充模块可以在rodata段搜索占位符,并将占位符替换为相应的元数据和校验预期值后,得到最终的第一可执行文件。

图5为本申请实施例中提供的一种验证方法的方法流程示意图。

如图5所示,该方法包括:

S501,电子设备执行第一可执行文件中代码段的第一函数,第一函数包括第一内部校验单元。

其中,第一可执行文件可以包括代码段、数据段和rodata段,具体结构可以参考上述图3A所示实施例中的相关描述,此处不再赘述。

第一可执行文件的代码段包括第一函数,第一函数包括第一内部校验单元,第一内部校验单元在本申请实施例中也可以称作IC1。

在电子设备执行第一可执行文件中代码段的第一函数时,电子设备可以执行第一函数中的第一内部校验单元,即电子设备可以执行IC1。

S502,电子设备通过第一内部校验单元确定第一函数的第一校验值。

电子设备通过IC1确定第一函数的第一校验值的过程可以包括以下步骤:

(1)电子设备可以通过IC1从代码段或者rodata段读取第一函数的第一元数据,第一元数据用于指示第一函数的位置信息,该第一函数的位置信息包括第一函数的起始存储地址和第一函数的数据长度。

(2)电子设备可以通过IC1基于第一元数据确定第一函数在第一可执行文件中的位置。

(3)电子设备可以通过IC1基于第一函数在第一可执行文件中的位置,读取第一函数并计算第一函数的第一校验值。其中,可以通过计算第一函数的哈希值确定第一校验值。

在一些实施例中,电子设备通过IC1确定第一函数的第一校验值的过程也可以包括如下步骤:

(1)电子设备可以通过IC1调用第一保护函数,其中,第一保护函数可以是sc_guard_self函数。

(2)电子设备可以通过第一保护函数从代码段或者rodata段读取第一函数的第一元数据。

(3)电子设备可以通过第一保护函数基于第一元数据确定第一函数在第一可执行文件中的位置。

(4)电子设备可以通过第一保护函数基于第一函数在第一可执行文件中的位置,读取第一函数并计算第一函数的第一校验值。其中,可以通过计算第一函数的哈希值确定第一校验值。

需要说明的是,在本申请实施例中,第一函数的第一元数据可以存储在第一可执行文件的代码段,也可以存储在第一可执行文件的rodata段。由于第一函数的第一元数据需要在可执行文件生成之后才可以确定,因此,在编译阶段可以先用占位符替代第一元数据,在可执行文件生成之后再用第一元数据替换占位符。当占位符被存储在代码段时,搜索占位符并替换为第一元数据的过程中很容易对代码段中的代码造成损伤,修改原有代码的逻辑导致功能性异常,因此,本申请实施例中的优选方案为将第一元数据等元数据存储在rodata段,这样可以避免在元数据的填充过程中对代码段中的代码造成损害。

S503,电子设备通过第一内部校验单元从第一可执行文件的只读数据段确定第一函数的第一校验预期值。

电子设备可以通过IC1从第一执行文件的rodata段读取第一函数的第一校验预期值,电子设备也可以通过IC1调用的第一保护函数从第一可执行文件的rodata段读取第一函数的第一校验预期值。

需要说明的是,如果第一元数据也被放置在第一可执行文件的rodata段,电子设备通过IC1从第一可执行文件的rodata段读取第一元数据和读取第一校验预期值的操作可以合并为一个操作,即电子设备可以通过IC1从第一可执行文件的rodata段同时读取第一元数据和第一校验预期值。

S504,电子设备基于第一校验预期值和第一校验值确定第一函数的完整性。

在确定第一函数的第一校验值和第一校验预期值之后,电子设备可以通过比较第一校验值和第一校验预期值确定第一函数的完整性。

示例性的,当第一校验值与第一校验预期值相同时,电子设备确定第一函数完整,即第一函数没有被篡改。当第一校验值与第一校验预期值不同时,电子设备确定第一函数受损,即第一函数已被篡改。

这样,在电子设备执行第一函数时,电子设备可以通过IC1对第一函数的完整性进行校验,而不需要其他可信的验证者。一旦第一函数被篡改,IC1能够及时检测出第一函数的完整性受损进而做出相应的保护措施(例如,静默记录、修复受损代码片段或者停止运行软件,等等),提高了校验网络对于攻击的敏感性,降低了用户受到的损害。此外,由于第一校验预期值被填充在第一可执行文件的rodata段,因此,第一校验预期值的填充不会影响到第一函数的校验预期值,也不会影响第一可执行文件的代码段。

在一种可能的实现方式中,电子设备在确定第一函数完整性之后,还可以根据第一函数的完整性确定之后的操作。

示例性的,当电子设备确定第一函数完整时,电子设备可以继续执行第一可执行文件。当电子设备确定第一函数非完整时,即第一函数受损时,电子设备可以停止执行第一可执行文件,并清空栈帧数据。

可选的,当电子设备确定第一函数受损时,电子设备也可以根据第一函数的重要程度,进行其他操作,例如,静默记录、修复受损代码片段、停止运行第一可执行文件,等等。

这样,在确保软件完整性的同时可以保证软件的正常运行。而在确定软件受到攻击后,可以通过及时的补救措施降低用户的受到损害的风险。

在一种可能的实现方式中,电子设备还可以通过外部校验单元对第一可执行文件所处内存中的某一个内存片段进行完整性校验。在本申请实施例中,也将上述一个内存片段称作第一可执行文件中的一个区域(例如,第一区域、第二区域,等等)。

示例性的,图6示出了一种外部校验单元针对第一可执行文件中的一个区域进行完整性校验的流程示意图。

如图6所示,第一外部校验单元对第一区域的完整性校验过程可以包括:

S601,电子设备执行第一可执行文件中代码段的第二函数,第二函数包括第一外部校验单元。

其中,第一可执行文件的代码段包括第二函数,第二函数包括第一外部校验单元,第一外部校验单元在本申请实施例中也可以称作OC1。

在电子设备执行第一可执行文件中代码段的第二函数时,电子设备可以执行第二函数中的第一外部校验单元,即电子设备可以执行OC1。

S602,电子设备通过第一外部校验单元确定第一区域的第二校验值。

其中,第一可执行文件可以被划分为多个可重叠的区域,第一区域是其中的一个区域。

电子设备可以直接通过OC1确定第一区域的第二校验值,具体过程可以包括如下步骤:

(1)电子设备可以通过OC1从代码段或者rodata段读取第一区域的第二元数据,第二元数据用于指示第一区域的位置信息,该第一区域的位置信息包括第一区域的起始存储地址和第一区域的数据长度。

(2)电子设备可以通过OC1基于第二元数据确定第一区域在第一可执行文件中的位置。

(3)电子设备可以通过OC1基于第一区域在第一可执行文件中的位置,读取第一区域中的数据并计算第一区域的第二校验值。其中,可以通过计算第一区域中数据的哈希值确定第二校验值。

在一些实施例中,电子设备也可以通过OC1调用第二保护函数,并通过第二保护函数确定第一区域的第二校验值。这种情况下,电子设备通过OC1确定第一区域的第二校验值的具体过程可以包括如下步骤:

(1)电子设备可以通过OC1调用第二保护函数,其中,第二保护函数可以是sc_guard_me函数。

(2)电子设备可以通过第二保护函数从代码段或者rodata段读取第一区域的第二元数据。

(3)电子设备可以通过第二保护函数基于第二元数据确定第一区域在第一可执行文件中的位置。

(4)电子设备可以通过第一保护函数基于第一区域在第一可执行文件中的位置,读取第一区域中的数据并计算第一区域的第二校验值。其中,可以通过计算第一区域中数据的哈希值确定第二校验值。

需要说明的是,在本申请实施例中,第一区域所对应的第二元数据可以存储在第一可执行文件的代码段,也可以存储在第一可执行文件的rodata段。具体内容可以参考上述图5所示步骤S502中的相关描述,此处不再赘述。

S603,电子设备通过第一外部校验单元从第一可执行文件的只读数据段确定第一区域的第二校验预期值。

电子设备可以通过OC1从第一执行文件的rodata段读取第一函数的第一校验预期值,电子设备也可以通过OC1调用的第二保护函数从第一可执行文件的rodata段读取第一区域的第二校验预期值。

需要说明的是,如果第二元数据也被放置在第一可执行文件的rodata段,电子设备通过OC1从第一可执行文件的rodata段读取第二元数据和读取第二校验预期值的操作可以合并为一个操作,即电子设备可以通过OC1从第一可执行文件的rodata段同时读取第二元数据和第二校验预期值。

S604,电子设备基于第二校验预期值和第二校验值确定第一区域的完整性。

在确定第一区域的第二校验值和第二校验预期值之后,电子设备可以通过比较第二校验值和第二校验预期值确定第一区域的完整性。

示例性的,当第二校验值与第二校验预期值相同时,电子设备确定第一区域完整,即第一区域没有被篡改。当第二校验值与第二校验预期值不同时,电子设备确定第一区域受损,即第一区域已被篡改。

这样,在电子设备执行第二函数的过程中,OC1可以对第一区域的完整性进行校验。由于每个OC都可以校验第一可执行文件中的其中一个区域的完整性,通过在软件程序中插入多个OC,可以实现对第一可执行文件完整性校验的高覆盖,甚至全覆盖。

在一种可能的实现方式中,电子设备在确定第一区域完整性之后,可以根据第一区域的完整性确定之后的操作。

示例性的,当电子设备确定第一区域完整时,电子设备可以继续执行第一可执行文件。当电子设备确定第一区域非完整时,即第一区域受损时,电子设备可以停止执行第一可执行文件,并清空栈帧数据。

可选的,当电子设备确定第一区域受损时,电子设备也可以根据第一区域的重要程度,进行其他操作,例如,静默记录、修复受损代码片段、停止运行第一可执行文件,等等。

这样,在确保软件完整性的同时可以保证软件的正常运行。而在确定软件受到攻击后,可以通过补救措施降低用户的受到损害的风险。

在一种可能的实现方式中,当电子设备执行到校验单元(例如IC1、OC1,等等)时,电子设备还可以调用一个随机单元,该随机单元用于从所校验的函数或内存片段中确定一个取样片段,该取样片段用于计算该函数或内存片段的校验值。

以上述实施例中的OC1为例,图7示出了电子设备通过OC1调用随机单元,并基于随机单元确定第一区域的完整性的流程示意图。

如图7所示,具体过程可以包括:

S701,电子设备执行第二函数中的第一外部校验单元。

其中,第二函数和第一外部校验单元可以参考上述实施例中的相关描述,此处不再赘述。在本申请实施例中,第一外部校验单元也可以写作OC1。

S702,电子设备通过OC1调用随机单元。

电子设备可以直接通过OC1调用随机单元,也可以通过OC1调用第二保护函数,再通过第二保护函数调用随机单元。

S703,电子设备通过随机单元生成随机数h。

电子设备可以通过随机单元生成随机数h,其中,随机数h的取值范围可以是预先设置的。

S704,电子设备通过OC1基于随机数h从rodata段读取第二校验预期值。

电子设备可以直接通过OC1基于随机数h从rodata段读取第二校验预期值,也可以通过第二保护函数从rodata段读取第二校验预期值。

需要说明的是,在这种情况下,第一区域在rodata段中对应的校验预期值有多个(大于等于两个),电子设备可以基于随机数h和校验预期值之间的关系,从上述多个校验预期值中读取其中一个校验预期值为第二校验预期值。示例性的,随机数h的取值可以是h1、h2或h3中的任一个,第一区域在rodata段中的校验预期值可以包括Y1、Y2和Y3。当随机单元生成的随机数为h1时,电子设备可以基于h1从rodata段读取校验预期值Y1作为第一区域的第二校验预期值;当随机单元生成的随机数为h2时,电子设备可以基于h2从rodata段读取校验预期值Y2作为第一区域的第二校验预期值;当随机单元生成的随机数为h3时,电子设备可以基于h3从rodata段读取校验预期值Y3作为第一区域的第二校验预期值。

S705,电子设备通过OC1确定第一区域的第二元数据。

电子设备通过OC1或第二保护函数确定第二元数据的具体过程可以参考上述图6所示实施例步骤S602中的相关描述,此处不再赘述。

S706,电子设备通过OC1基于随机数h和第二元数据确定取样片段。

电子设备可以通过OC1或第二保护函数基于第二元数据确定第一区域在第一可执行文件中的位置,其具体过程可以参考上述图6所示实施例步骤S602中的相关描述,此处不再赘述。

在确定第一区域在第一可执行文件中的位置之后,电子设备可以基于随机数h从第一区域中确定取样片段。示例性的,电子设备可以通过在第一区域中每H个字节取h个字节,作为第一区域的取样片段,电子设备也可以通过将第一区域划分为H个片段,取第h个片段作为取样片段。本申请实施例对取样片段的确定方式不做限定。

S707,电子设备通过OC1基于取样片段确定第一区域的第二校验值。

在确定取样片段之后,电子设备可以通过OC1或第二保护函数基于取样片段确定第二校验值,其中,第二校验值可以通过计算取样片段的哈希值确定。

S708,电子设备基于第二校验值和第二校验预期值确定第一区域的完整性。

在确定第二校验值和第二校验预期值之后,电子设备可以基于二者的关系确定第一区域的完整性,具体过程可以参考上述图6所示实施例步骤S604中的相关描述,此处不再赘述。

可以理解的是,在一些实施例中,电子设备执行IC的过程中也可以调用一个随机单元,并通过该随机单元从IC所校验的函数中确定一个取样片段,并基于该取样片段计算该函数的校验值。具体过程,可以参考上述图7所示实施例中的相关描述,此处不再赘述。

这样,当OC或IC所校验的函数或内存片段过长时,可以随机地对该函数或内存片段的取样片段计算校验值,不需要对整个函数或内存片段进行校验值计算,极大地降低了校验过程带来的能耗。此外,随机性的引入也增加了校验网络的复杂性,让攻击者更难确定校验网络的模型,从而降低了校验网络被篡改的风险。

在一种可能的实现方式中,第一区域可以包括第一函数,在这种情况下,当电子设备利用上述实施例中所示方法通过OC1确定第一区域完整时,电子设备可以确定第一函数完整,同时,电子设备还可以确定位于第一函数中的IC1完整。这样,第一函数的完整性可以由IC1或OC1来完成校验,而IC1的完整性也可以通过OC1来校验,从而降低了第一函数被篡改的风险。类似的,各个IC与各个OC之间可以通过这样的关系组成校验网络,降低软件程序被篡改的风险。

在一种可能的实现方式中,第一区域也可以包括第二函数,在这种情况下,当电子设备利用上述实施例中所示方法通过OC1确定第一区域完整时,电子设备可以确定第二函数完整,同时确定位于第二函数中的OC1完整,即电子设备可以通过OC1对OC1的完整性进行自校验。

由于校验预期值(例如,第一校验预期值、第二校验预期值,等等)被填充在可执行文件中的rodata段,因此,校验预期值的填充过程不会对代码段造成任何影响,校验预期值的填充也不会影响OC或IC所在的函数或内存片段的校验值,因此,在本申请实施例中提供的验证方法中,IC和OC组成的校验网络没有无环要求,即IC和OC组成的校验网络可以是成环的,例如OC1的完整性可以由OC1来完成校验。因此,在IC和OC组成的校验网络中,可以不存在校验网络的源点,即可以不存在无法被校验的校验单元。这样,可以更进一步提高校验网络的抗攻击能力,降低软件被篡改的风险。

在一种可能的实现方式中,第一函数可以被划分为多个部分,例如两个部分,第一区域包括第一函数的第一部分,第二区域包括第一函数的第二部分,其中,第二区域是第一可执行文件被划分成多个区域中的其中一个区域。

在这种情况下,利用上述实施例中所描述的方法,当电子设备通过OC1确定第一区域完整时,电子设备可以确定第一函数的第一部分完整。

在一些实施例中,电子设备可以执行第一可执行文件中代码段的第三函数,第三函数包括第二外部校验单元,即OC2。利用上述实施例中提供的验证方法,当电子设备通过OC2确定第二区域完整时,电子设备可以确定第一函数的第二部分完整。在电子设备分别确定第一函数的第一部分和第二部分完整后,电子设备可以确定第一函数完整。

这样,电子设备也可以通过多个OC对函数的完整性进行校验。

在一种可能的实现方式中,当电子设备执行到校验单元时,电子设备还可以通过可信根模块对该校验单元进行二级校验,二级校验是电子设备通过可信根模块对该校验单元对应的以下任意一项或多项数据进行的完整性校验:元数据(例如,第一元数据、第二元数据,等等)、校验预期值(例如,第一校验预期值、第二校验预期值,等等)和保护函数(例如,第一保护函数、第二保护函数,等等)。

示例性的,图8示出了一种电子设备通过可信根模块对IC1进行二级校验的流程示意图。

如图8所示,电子设备通过可信根模块对IC1进行二级校验的流程可以包括:

S801,电子设备通过可信根模块从rodata段读取IC1对应的二级校验数据。

当检测到电子设备执行到IC1时,电子设备通过可信根模块从rodata段读取IC1对应的二级数据。其中,IC1对应的二级数据用于IC1的完整性,IC1对应的二级数据可以包括:第一保护函数的起始存储地址和数据长度、第一元数据起始存储地址和数据长度以及第一校验预期值的起始存储地址和数据长度。

需要说明的是,在这种情况下,rodata段存储有上述IC1对应的二级校验数据。

S802,电子设备基于二级校验数据,通过可信根模块计算第一元数据的第一哈希值,并将第一哈希值作为可信根模块的第一派生因子。

电子设备可以基于第一元数据起始存储地址和数据长度,通过可信根模块确定第一元数据的位置并读取第一元数据,计算第一元数据的第一哈希值,并将第一哈希值作为可信根模块的第一派生因子。

S803,电子设备基于二级校验数据,通过可信根模块计算第一校验预期值的第二哈希值,并将第二哈希值作为可信根模块的第二派生因子。

电子设备可以基于第一校验预期值起始存储地址和数据长度,通过可信根模块确定第一校验预期值的位置并读取第一校验预期值,计算第一校验预期值的第二哈希值,并将第二哈希值作为可信根模块的第二派生因子。

可以理解的是,在一些实施例中,电子设备也可以基于二级校验数据,通过可信根模块计算第一元数据和第一校验预期值的哈希值,并将该第一元数据和第一校验预期值的哈希值作为可信根模块的一个派生因子。本申请在此不做限定。

S804,电子设备基于二级校验数据,通过可信根模块计算第一保护函数的第三哈希值,并将第三哈希值作为可信根模块的第三派生因子。

电子设备可以基于第一保护函数起始存储地址和数据长度,通过可信根模块确定第一保护函数的位置并读取第一保护函数,计算第一保护函数的第三哈希值,并将第三哈希值作为可信根模块的第三派生因子。

S805,基于派生因子确定可信根模块的根密钥,通过根密钥与可信根模块的匹配结果确定二级校验的结果。

电子设备可以通过可信根模块基于派生因子确定可信根模块的根密钥。其中,派生因子是可信根模块所有的派生因子,可以包括:第一派生因子、第二派生因子、第三派生因子,等等。

在确定可信根模块的根密钥之后,电子设备可以通过该根密钥与可信根模块之间的匹配关系确定二级校验结果。示例性的,当根密钥与可信根模块匹配时,电子设备确定IC1完整。当根密钥与可信根模块不匹配时,电子设备确定IC1受损。

这样,可以通过可信根模块来确保保护函数以及元数据和校验预期值的完整性,确保保护函数、元数据以及校验预期值不会被篡改。

在一种可能的实现方式中,电子设备还可以在确定待执行的校验单元满足预设条件之后,确定执行该校验单元,即在满足预设条件时确定通过该校验单元确定该校验单元所校验的函数或内存片段的校验值。

示例性的,图9示出了一种电子设备根据待执行的校验单元与预设条件的关系决定是否执行该校验单元的流程示意图。

如图9所示,上述流程具体可以包括:

S901,电子设备检测到执行中的函数F中存在校验单元C1。

S902,电子设备确定函数F执行的次数M。

在电子设备检测到执行中的函数F中存在校验单元C1之后,电子设备可以确定函数F的执行次数M(包含正在执行中的这一次)。其中M是大于等于1的正整数。

S903,电子设备判断执行的次数M是否大于1。

在确定函数F的执行次数M之后,电子设备可以基于M的数值确定M与1之间的关系。

S904,当电子设备确定M=1时,电子设备确定执行校验单元C1。

由于M是大于等于1的正整数,当电子设备确定M不大于1,即当电子设备确定M=1时,该函数F为首次执行,电子设备确定执行校验单元C1中的指令。

S905,当电子设备确定M>1时,电子设备生成随机数x。

当电子设备确定M大于1时,即函数F非首次执行,电子设备可以生成一个随机数x。

S906,电子设备判断随机数x与预存的固定值z是否相同。

基于随机数x和预存的固定值z,电子设备可以判断随机数x和固定值z是否相同。

S907,当随机数x与固定值z相同时,电子设备确定执行校验单元C1。

当随机数x与固定值z相同时,电子设备确定执行校验单元C1中的指令。

S908,当随机数x与固定值z不同时,电子设备确定不执行校验单元C1。

当随机数x与固定值z不同时,电子设备不执行校验单元C1中的指令。

在另一些实施例中,预设条件也可以是其他条件,例如距离上一次执行该校验单元时间间隔、校验单元所在函数F的执行频次、校验单元所在函数F的重要性,等等,本申请实施例中不对预设条件做具体限定。

这样,通过引入预设条件判决,可以以一定的随机概率(例如,百分之一、千分之一,等等)来触发校验单元进行校验,降低了校验单元执行校验的频率,从而减少能量的损耗。同时,由于在校验单元的触发中引入了随机性,攻击者也更难确定校验网络,从而也降低了软件被篡改的风险。

此外,还可以根据校验单元所校验的对象的重要程度设置不同的随机触发校验的频率,为重要的、高敏感的函数设置较高的随机校验触发频率,为不重要的、低敏感的函数设置较低的随机校验触发频率,从而对能耗进行更经济更高效的划分。

下面介绍本申请实施例中提供的一种电子设备的功能模块。

如图10所示,电子设备可以包括自校验(self-checksumming,SC)模块1010、只读数据(rodata)模块1020,可选的,在一些实施例中,电子设备还可以包括可信根模块1030。

SC模块1010可以包括代码段中的一个或多个校验单元。其中,校验单元可以包括一个或多个IC(例如,IC1)和一个或多个OC(例如,OC1)。任意一个IC可用于触发电子设备校验该IC所在函数的完整性,任意一个OC可用于触发电子设备校验该OC所对应的内存片段的完整性。在一些实施例中,SC模块还可以包括保护函数,保护函数可以包括第一保护函数和第二保护函数。第一保护函数可以被任意一个IC调用,用于校验该IC所在函数的完整性。第二保护函数可以被任意一个OC调用,用于校验该OC所对应的内存片段的完整性。

在执行到任意一个IC或OC时,SC模块1010可以向只读数据模块1020发送数据读取请求,该数据读取请求用于从只读数据模块1020读取相应的元数据和校验预期值。在一些实施例中,该数据读取请求也可以用于从只读数据模块1020读取校验预期值,在这种情况下,SC模块也可以从代码段读取相应的元数据,本申请在此不做限定。

SC模块1010可以基于该元数据和校验预期值确定该IC所校验的函数的完整性,或确定该OC所校验的内存片段的完整性。具体过程可以参考上述图5至图9所示实施例中的相关内容,此处不再赘述。

只读数据模块1020位于可执行文件中的只读数据段,只读数据模块1020可用于储存元数据(例如,第一元数据、第二元数据,等等)和校验预期值(例如,第一校验预期值、第二校验预期值,等等)。在执行第一可执行文件中的任意一个IC或OC的过程中,只读数据模块1020可以响应于SC模块1010发送的数据读取请求,将相应的校验预期值或将相应的元数据和校验预期值发送给SC模块1010。在一些实施例中,只读数据模块1020中还可以储存二级校验数据(例如,保护函数的起始存储地址和数据长度、元数据和校验预期值的起始存储地址和数据长度,等等)。只读数据模块1020可以响应于可信根模块1030发送的二级校验数据请求,将上述二级校验数据发送给可信根模块1030。

在一些实施例中,电子设备还可以包括可信根模块1030。可信根模块1030可用于校验保护函数和只读数据模块1020中存储的元数据和校验预期值的完整性。

可信根模块1030针对保护函数、元数据和校验预期值的完整性校验可以参考上述图8所示实施例中的相关描述,此处不再赘述。

在另一些实施例中,电子设备还可以包括预设条件判决模块1040(图中未示出)。在一种可能的实现方式中,预设条件判决模块1040也可以设置在自校验模块1010中。预设条件判决模块1040可以在校验单元执行之前,基于该校验单元当前的情况与预设条件进行判决,当该校验单元当前的情况满足预设条件时,判决结果为执行该校验单元。当该校验单元当前的情况不满足预设条件时,判决结果为不执行该校验单元。预设条件判决模块1040具体的执行过程,可以参考上述图9所示实施例中的相关内容,本申请在此不再赘述。

最后,下面介绍本申请提供的电子设备。

图11为本申请实施例提供的电子设备100硬件结构的一个示例性示意图。

下面以电子设备100为例对实施例进行具体说明。应该理解的是,电子设备100可以具有比图中所示的更多的或者更少的部件,可以组合两个或多个的部件,或者可以具有不同的部件配置。图中所示出的各种部件可以在包括一个或多个信号处理和/或专用集成电路在内的硬件、软件、或硬件和软件的组合中实现。

电子设备100可以包括:处理器110、总线和接口120、随机存取存储器(randomaccess memory,RAM)130、非易失性存储器(non-volatile memory,NVM)140、传感器模块150、通信模块160、显示模块170等。其中,非易失性存储器中包括ROM/flashmemory。

可以理解的是,本发明实施例示意的结构并不构成对电子设备100的具体限定。在本申请另一些实施例中,电子设备100可以包括比图示更多或更少的部件,或者组合某些部件,或者拆分某些部件,或者不同的部件布置。图示的部件可以以硬件,软件或软件和硬件的组合实现。

处理器110可以包括一个或多个处理单元,例如:内存管理单元(memorymanagement unit,MMU)、内存保护单元(memory protection unit,MPU)、运算器、控制器、寄存器、数字信号处理器(digital signal processor,DSP),基带处理器,和/或神经网络处理器(neural-network processing unit,NPU)等。其中,不同的处理单元可以是独立的器件,也可以集成在一个或多个处理器中。

总线和接口120可以包括集成电路(inter-integrated circuit,I2C)接口,集成电路内置音频(inter-integrated circuit sound,I2S)接口,脉冲编码调制(pulse codemodulation,PCM)接口,通用异步收发传输器(universal asynchronous receiver/transmitter,UART)接口,移动产业处理器接口(mobile industry processor interface,MIPI),通用输入输出(general-purpose input/output,GPIO)接口,用户标识模块(subscriber identity module,SIM)接口,和/或通用串行总线(universal serial bus,USB)接口等。

可以理解的是,本发明实施例示意的各模块间的接口连接关系,只是示意性说明,并不构成对电子设备100的结构限定。在本申请另一些实施例中,电子设备100也可以采用上述实施例中不同的接口连接方式,或多种接口连接方式的组合。

随机存取存储器130可以包括静态随机存储器(static random-access memory,SRAM)、动态随机存储器(dynamic random access memory,DRAM)、同步动态随机存储器(synchronous dynamic random access memory,SDRAM)、双倍资料率同步动态随机存取存储器(double data rate synchronous dynamic random access memory,DDR SDRAM,例如第五代DDR SDRAM一般称为DDR5 SDRAM)等。

非易失性存储器140可以包括磁盘存储器件、快闪存储器(flash memory)。快闪存储器按照运作原理划分可以包括NOR FLASH、NAND FLASH、3D NAND FLASH等,按照存储单元电位阶数划分可以包括单阶存储单元(single-level cell,SLC)、多阶存储单元(multi-level cell,MLC)、三阶储存单元(triple-level cell,TLC)、四阶储存单元(quad-levelcell,QLC)等,按照存储规范划分可以包括通用闪存存储(英文:universal flashstorage,UFS)、嵌入式多媒体存储卡(embedded multi media Card,eMMC)等。

随机存取存储器130可以由处理器110直接进行读写,可以用于存储操作系统或其他正在运行中的程序的可执行程序(例如机器指令),还可以用于存储用户及应用程序的数据等。

非易失性存储器140也可以存储可执行程序和存储用户及应用程序的数据等,可以提前加载到随机存取存储器中,用于处理器110直接进行读写。

传感器模块150可以包括压力传感器、陀螺仪传感器、气压传感器、磁传感器、加速度传感器、距离传感器、接近光传感器、环境光传感器、指纹传感器、触摸传感器、骨传导传感器等。

通信模块160可以包括移动通信模块、无线通信模块。

显示模块170可以包括显示屏。

本申请的各实施方式可以任意进行组合,以实现不同的技术效果。

在上述实施例中,可以全部或部分地通过软件、硬件、固件或者其任意组合来实现。当使用软件实现时,可以全部或部分地以计算机程序产品的形式实现。所述计算机程序产品包括一个或多个计算机指令。在计算机上加载和执行所述计算机程序指令时,全部或部分地产生按照本申请所述的流程或功能。所述计算机可以是通用计算机、专用计算机、计算机网络、或者其他可编程装置。所述计算机指令可以存储在计算机可读存储介质中,或者从一个计算机可读存储介质向另一个计算机可读存储介质传输,例如,所述计算机指令可以从一个网站站点、计算机、服务器或数据中心通过有线(例如同轴电缆、光纤、数字用户线)或无线(例如红外、无线、微波等)方式向另一个网站站点、计算机、服务器或数据中心进行传输。所述计算机可读存储介质可以是计算机能够存取的任何可用介质或者是包含一个或多个可用介质集成的服务器、数据中心等数据存储设备。所述可用介质可以是磁性介质,(例如,软盘、硬盘、磁带)、光介质(例如,DVD)、或者半导体介质(例如固态硬盘(solidstate disk,SSD))等。

本领域普通技术人员可以理解实现上述实施例方法中的全部或部分流程,该流程可以由计算机程序来指令相关的硬件完成,该程序可存储于计算机可读取存储介质中,该程序在执行时,可包括如上述各方法实施例的流程。而前述的存储介质包括:ROM或随机存储记忆体RAM、磁碟或者光盘等各种可存储程序代码的介质。

总之,以上所述仅为本发明技术方案的实施例而已,并非用于限定本发明的保护范围。凡根据本发明的揭露,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。