一种四通道鳍型的垂直碳化硅器件及其制备方法

文献发布时间:2024-01-17 01:15:20

技术领域

本发明涉及碳化硅器件领域,尤其是一种四通道鳍型的垂直碳化硅器件及其制备方法。

背景技术

碳化硅材料具有优良的物理和电学特性,以其宽的禁带宽度、高的热导率、大的饱和漂移速度和高的临界击穿电场等独特优点,成为制作高功率、高频、高压、耐高温、抗辐射器件的理想半导体材料,在军事和民事方面具有广阔的应用前景。

碳化硅MOSFET(Metal Oxide Semiconductor Filed-effect Transistor)器件则具有开关速度快、导通电阻小等优势,且在较小的漂移层厚度可以实现较高的击穿电压水平,减小功率开关模块的体积,降低能耗,在功率开关、转换器等应用领域中优势明显。随着5G通信、智能家电和自动驾驶等新兴电子信息产业的快速发展,碳化硅MOSFET器件重要性日益凸显,要求功率MOSFET朝着额定功率更大、开关速度更快、驱动功耗更小等方向前进。现有的MOSFET(PIC7)利用两侧的Dummy区能够很好的保护栅极(Gate),提高器件性能但是导致器件面积增大,单位面积上功率减小,导致器件功率较小。

发明内容

有鉴于此,本发明提供了一种四通道鳍型的垂直碳化硅器件,达到增加器件的电流通道、提高器件功率目的。具体为一种四通道鳍型的垂直碳化硅器件,N型衬底层;

N型掺杂漂移层,位于所述N型衬底层的上表面;

鳍型硅墙,鳍型硅墙设有两个,两个鳍型硅墙间隔且平行成型在所述漂移层的上表面,两个鳍型硅墙关于所述器件的中线对称,鳍型硅墙包括N型掺杂缓冲层、P阱层、N+区域和P+区域,N型掺杂缓冲层位于N型掺杂漂移层的上表面,P阱层位于所述N型掺杂缓冲层的上表面,P阱层的上表面设有源区,源区包括两个N+区域和一个P+区域,P+区域设置在两个N+区域之间;

P型屏蔽区,P型屏蔽区设有至少两个,P型屏蔽区关于所述器件的中线对称,位于N型掺杂漂移层上部的部分区,其中一个P型屏蔽区位于一个鳍型硅墙远离另个一鳍型硅墙一侧的底部;

栅氧化层,位于P型屏蔽区的上表面、两个鳍型硅墙的侧表面以及两个鳍型硅墙之间N型掺杂缓冲层的上表面;

多晶硅栅层,位于栅氧化层的内表面,两个鳍型硅墙之间的多晶硅栅层的上表面与所述源区的上表面齐平;

第一导电材料,位于N型衬底层的下表面,形成漏极;

第二导电材料,位于两个鳍型硅墙之间多晶硅栅层的上表面,形成栅极;

第三导电材料,位于源区的上表面,形成源极。

进一步地,两个鳍型硅墙之间的多晶硅栅层下表面比所述P阱层的下表面更接近于所述N型衬底层。

进一步地,还包括第四导电材料,位于N型掺杂漂移层上部未设置P型屏蔽区的上表面,所述P型屏蔽区与所述源极相短接。

进一步地,位于一个鳍型硅墙远离另个一鳍型硅墙一侧的多晶硅栅层形成侧墙,所述侧墙设置在P型屏蔽区上方栅氧化层的部分区域上,所述侧墙距离所述N型衬底层的最远端与所述源区的上表面齐平。

进一步地,沿着远离N型衬底层的方向,形成侧墙的所述多晶硅栅层的横截面逐渐减小。

进一步地,沿着远离N型衬底层的方向,形成侧墙的所述多晶硅栅层的横截面的斜率逐渐减小。

进一步地,所述漂移层的厚度为6μm。

进一步地,所述P型屏蔽区的掺杂元素为B元素或Al元素,P型屏蔽区的掺杂浓度高于P阱层的掺杂浓度。

进一步地,所述P型屏蔽区的掺杂浓度为1e17,厚度为0.2um。

还提出了一种上述四通道鳍型的垂直碳化硅器件的制备方法,所述方法包括以下步骤:

S1、在N型衬底层的上表面生长N型掺杂漂移层,随后,在N型掺杂漂移层上表面相应区域进行P+的注入形成P型屏蔽区;

S2、在N型掺杂漂移层上表面继续生长形成N型掺杂缓冲层,在N型掺杂缓冲层上表面生长形成P阱层,在P阱层上表面注入N+和P+,形成源区;

S3、刻蚀形成两个鳍型硅墙,具体刻蚀两个鳍型硅墙之间的沟槽一和鳍型硅墙外侧部的沟槽二,形成两个间隔且平行的鳍型硅墙;

S4、在P型屏蔽区的上表面、N型掺杂漂移层、两个鳍型硅墙的侧表面以及两个鳍型硅墙之间N型掺杂缓冲层的上表面进行栅氧的填充形成栅氧化层;在栅氧化层和源区的上表面填充多晶硅;

S5、刻蚀多晶硅,保留位于栅氧化层内表面的多晶硅,形成多晶硅栅层;

S6、沉积导电材料,在N型衬底层的下表面沉积第一导电材料形成漏极,在两个鳍型硅墙之间多晶硅栅层的上表面沉积第二导电材料形成栅极;在源区的上表面沉积第三导电材料形成源极。

与现有技术相比,本发明的有益效果是:

1、通过设置两个鳍型硅墙,并在每个鳍型硅墙上设源区,源区包括两个N+区域和一个P+区域,P+区域设置在两个N+区域之间,使得器件的电流通道数量增加,电流通道由原来的双通道增加至四通道,提高器件的功率;

2、通过源区下方P阱层105形成的P型埋层之间的JFET效应产生耗尽区,阻挡电力线,能够很好保护栅结构,同时也能够很好的保护集成SBD二极管,提高器件的反向性能。

本发明的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本发明而了解。本发明的目的和其他优点可通过在说明书、权利要求书以及附图中所指出的结构来实现和获得。

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

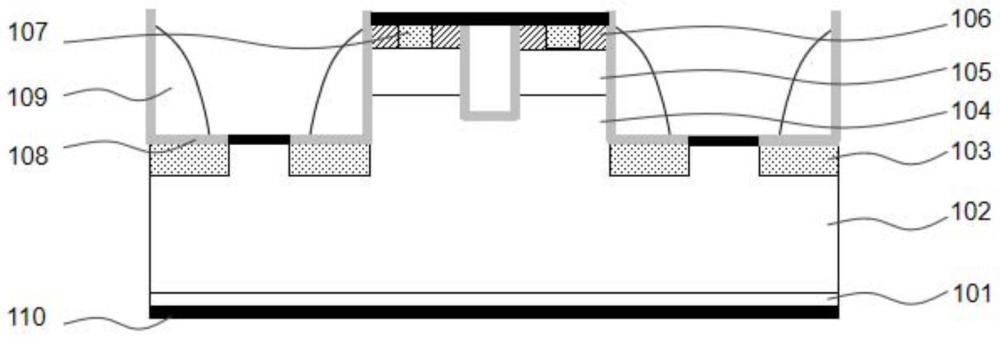

图1示出了本发明实施例提供的四通道鳍型的垂直碳化硅器件的结构示意图。

图2示出了本发明实施例提供的四通道鳍型的垂直碳化硅器件的制备方法过程图。

附图标记说明:

N型衬底层101;N型掺杂漂移层102;P型屏蔽区103;N型掺杂缓冲层104;P阱层105;N+区域106;P+区域107;栅氧化层108;多晶硅栅层109;导电材料110。

具体实施方式

为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地说明,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

本发明实施例提供的四通道鳍型的垂直碳化硅器件,参见图1,包括,

N型衬底层101;

N型掺杂漂移层102,位于所述N型衬底层101的上表面;

鳍型硅墙,鳍型硅墙设有两个,两个鳍型硅墙间隔且平行成型在所述N型掺杂漂移层102的上表面,两个鳍型硅墙关于所述器件的中线对称,鳍型硅墙包括N型掺杂缓冲层104、P阱层105、N+区域106和P+区域107,N型掺杂缓冲层104位于N型掺杂漂移层102的上表面,P阱层105位于所述N型掺杂缓冲层104的上表面,P阱层105的上表面设有源区,源区包括两个N+区域106和一个P+区域107,P+区域107设置在两个N+区域106之间;

P型屏蔽区103,P型屏蔽区103设有至少两个,P型屏蔽区103关于所述器件的中线对称,位于N型掺杂漂移层102上部的部分区,其中一个P型屏蔽区103位于一个鳍型硅墙远离另个一鳍型硅墙一侧的底部;

栅氧化层108,位于P型屏蔽区103的上表面、两个鳍型硅墙的侧表面以及两个鳍型硅墙之间N型掺杂缓冲层104的上表面;

多晶硅栅层109,位于栅氧化层108的内表面,两个鳍型硅墙之间多晶硅栅层108的上表面与源区的上表面齐平;

第一导电材料,位于N型衬底层101的下表面,形成漏极;

第二导电材料,位于两个鳍型硅墙之间多晶硅栅层109的上表面,形成栅极;

第三导电材料,位于源区的上表面,形成源极。

本发明设有两个鳍型硅墙,并在每个鳍型硅墙上设源区,源区包括两个N+区域106和一个P+区域107,P+区域107设置在两个N+区域106之间,使得器件的电流通道数量增加,电流通道由原来的双通道增加至四通道,提高器件的功率;并且通过源区下方P阱层105形成的P型埋层之间的JFET效应产生耗尽区,阻挡电力线,能够很好保护栅结构,同时也能够很好的保护集成SBD二极管,提高器件的反向性能。

两个鳍型硅墙之间的多晶硅栅层109下表面比P阱层105的下表面更接近于N型衬底层101;P阱层105主要用于进行电荷耦合为SBD提供耐压保护。

还包括第四导电材料,位于N型掺杂漂移层102上部未设置P型屏蔽区103的上表面,所述P型屏蔽区103与源极相短接;与源极短接的P型屏蔽区可以抑制器件的动态特性恶化。

位于一个鳍型硅墙远离另个一鳍型硅墙一侧的多晶硅栅层形成侧墙,所述侧墙设置在P型屏蔽区103上方栅氧化层108的部分区域上,所述侧墙距离所述N型衬底层101的最远端与所述源区的上表面齐平;侧墙用于保护栅氧化层108表面,以减少后续形成源漏结构的刻蚀工艺中对栅氧化层108造成的损伤。

沿着远离N型衬底层101的方向,形成侧墙的所述多晶硅栅层的横截面逐渐减小;沿着远离N型衬底层101的方向,形成侧墙的所述多晶硅栅层的横截面的斜率逐渐减小,利用Spacer工艺制作侧墙,防止半导体结构形成工艺过程中,侧墙表面受到损伤,延长侧墙的使用时间。

所述P型屏蔽区103的掺杂元素为B元素或Al元素,P型屏蔽区103的掺杂浓度高于P阱层的掺杂浓度,使得器件在P型屏蔽区103形成耗尽区

在一实施例中,所述N型衬底层101为N型掺杂的4H-SiC衬底,漂移层的厚度为6μm,所述P阱层的掺杂元素为B元素或Al元素

基于该实施例,在常温条件下,对所述四通道鳍型的垂直碳化硅器件进行性能测试,能够有效提高器件的功率。

上述四通道鳍型的垂直碳化硅器件的制备方法如下,参见图2,具体包括以下步骤:

S1、在N型衬底层101的上表面生长N型掺杂漂移层102,随后,使用离子注入技术,在N型掺杂漂移层102上表面相应区域进行P+的注入形成P型屏蔽区103,参见图2中的(a);

S2、在N型掺杂漂移层102上表面继续生长形成N型掺杂缓冲层104,在N型掺杂缓冲层104上表面生长形成P阱层105,在P阱层105上表面的注入N+和P+,形成源区层

S3、刻蚀形成两个鳍型硅墙,具体刻蚀两个鳍型硅墙之间的沟槽一和鳍型硅墙的外侧部沟槽二,形成两个间隔且平行的鳍型硅墙;沟槽一的下表面处于P阱层105的下表面与N型掺杂漂移层102的上表面之间,沟槽二的下表面与N型掺杂漂移层102的上表面齐平,参见图2中的(c);

使用传统的刻蚀技术形成沟槽,例如,使用硬掩膜板(hard mask)或软掩膜板(soft mask)进行刻蚀。

S4、在P型屏蔽区103的上表面、N型掺杂漂移层102、两个鳍型硅墙的侧表面以及两个鳍型硅墙之间N型掺杂缓冲层104的上表面进行栅氧的填充形成栅氧化层108;在栅氧化层108和源区的上表面填充多晶硅,参见图2中的(d);多晶硅在栅氧化层108和源区的上表面均延伸出一定的高度。

S5、刻蚀多晶硅,保留位于栅氧化层108内表面的多晶硅,形成多晶硅栅层109,参见图2中的(e);

其中,刻蚀后两个鳍型硅墙之间多晶硅栅层的上表面与源区的上表面齐平;

位于一个鳍型硅墙远离另个一鳍型硅墙一侧的多晶硅栅层形成侧墙,所述侧墙设置在P型屏蔽区103上方栅氧化层108的部分区域上,侧墙距离N型衬底层101的最远端与源区的上表面齐平;沿着远离N型衬底层101的方向,形成侧墙的所述多晶硅栅层的横截面逐渐减小,并且沿着远离N型衬底层101的方向,形成侧墙的所述多晶硅栅层的横截面的斜率逐渐减小。

S6、沉积导电材料110,在N型衬底层101的下表面沉积第一导电材料形成漏极,在两个鳍型硅墙之间多晶硅栅层的上表面沉积第二导电材料形成栅极;在源区的上表面沉积第三导电材料形成源极,参见图2中的(f);

另外,步骤S6还包括在N型掺杂漂移层102上部未设置P型屏蔽区103的上表面沉积第四导电材料,所述P型屏蔽区103与源极相短接。

尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。