一种特殊显示屏结构及其驱动方法

文献发布时间:2023-06-19 09:46:20

技术领域

本发明涉及显示屏技术领域,特别涉及一种特殊显示屏结构及其驱动方法。

背景技术

窄边框、全面屏的显示屏设计已成为主流,随着显示屏的广泛普及,从屏占比角度来看,2007年的初代iPhone屏占比仅为50%左右,后续几年内,手机屏占比在持续提升,但提升幅度不大。现有的显示屏,驱动单元的Y轴长度是影响全面屏或者窄边框屏的一个重要因素。现有的显示屏是IC(集成芯片,也作驱动单元)的一条源极走线(Source Line)对应面内一条数据走线(Data Line),显示屏一条数据走线控制一种子像素,导致源极走线数量过多,使得IC的Y轴得不到减小,使显示屏功耗增加,同时又增加了驱动单元的制作成本。

发明内容

本发明所要解决的技术问题是:提供一种特殊显示屏结构及其驱动方法。

为了解决上述技术问题,本发明采用的第一种技术方案为:

一种特殊显示屏结构,包括两个以上的像素单元、第一Demux走线、第二Demux走线、第三Demux走线和多条栅极走线,一个所述像素单元配置两条栅极走线且位于两条栅极走线之间;

每个所述像素单元包括从左至右依次排列的九列子像素对,位于第一列的所述子像素对至第三列的子像素对划分为第一子像素组,位于第四列的所述子像素对至第六列的子像素对划分为第二子像素组,位于第七列的所述子像素对至第九列的子像素对划分为第三子像素组,一列所述子像素对配置两条数据走线且位于两条数据走线之间,相邻的两列所述子像素对共用一条数据走线,所述第一子像素组中所有的子像素对配置的数据走线分别对应连接有一个TFT开关,所述第二子像素组中所有的子像素对配置的数据走线分别对应连接有一个TFT开关,所述第三子像素组中所有的子像素对配置的数据走线分别对应连接有一个TFT开关;

所述第一子像素组中所有的TFT开关的栅极均与第一Demux走线电连接,所述第二子像素组中所有的TFT开关的栅极均与第二Demux走线电连接,所述第三子像素组中所有的TFT开关的栅极均与第三Demux走线电连接,每个所述TFT开关的输入端分别对应连接有一条源极走线;

位于第n位置的TFT开关、第(n+3)位置的TFT开关和第(n+6)位置的TFT开关共用一条源极走线,其中n的取值为1或2或3。

本发明采用的第二种技术方案为:

一种特殊显示屏结构的驱动方法,包括以下步骤:

步骤S1、在一个像素单元中,控制两条栅极走线中的一条栅极走线开启;

步骤S2、在一条栅极走线开启期间,依次控制第一Demux走线、第二Demux走线和第三Demux走线开启;在第一Demux走线开启期间,控制源极走线将信号传输至位于第一位置至第三位置的数据走线连接的像素对中;在第二Demux走线开启期间,控制源极走线将信号传输至位于第四位置至第六位置的数据走线连接的像素对中;在第三Demux走线开启期间,控制源极走线将信号传输至位于第七位置至第九位置的数据走线连接的像素对中;

步骤S3、控制两条栅极走线中的另一条栅极走线开启;

步骤S4、在另一条栅极走线开启期间,依次控制第一Demux走线、第二Demux走线和第三Demux走线开启;在第一Demux走线开启期间,控制源极走线将信号传输至位于第一位置至第三位置的数据走线连接的像素对中;在第二Demux走线开启期间,控制源极走线将信号传输至位于第四位置至第六位置的数据走线连接的像素对中;在第三Demux走线开启期间,控制源极走线将信号传输至位于第七位置至第九位置的数据走线连接的像素对中;

步骤S5、循环步骤S1-S4,驱动每个像素单元。

本发明的有益效果在于:

本方案通过设置第一Demux走线、第二Demux走线和第三Demux走线分别与像素单元中的第一子像素组、第二子像素组和第三子像素组中的TFT开关对应连接,采用这样的Layout设计使本方案的源极走线比普通显示屏少了5倍,有利于显示屏的下Border(边界)极度缩小,为全面屏的实现提供了另外的方案设计;由于IC的源极走线数量的减少,使得IC在Y轴上变得更窄,这样可使显示屏达到全面屏效果;本方案设计的像素排列方式可节省白画面的功耗,改善显示屏由于热效应引起的寿命缩短问题。

附图说明

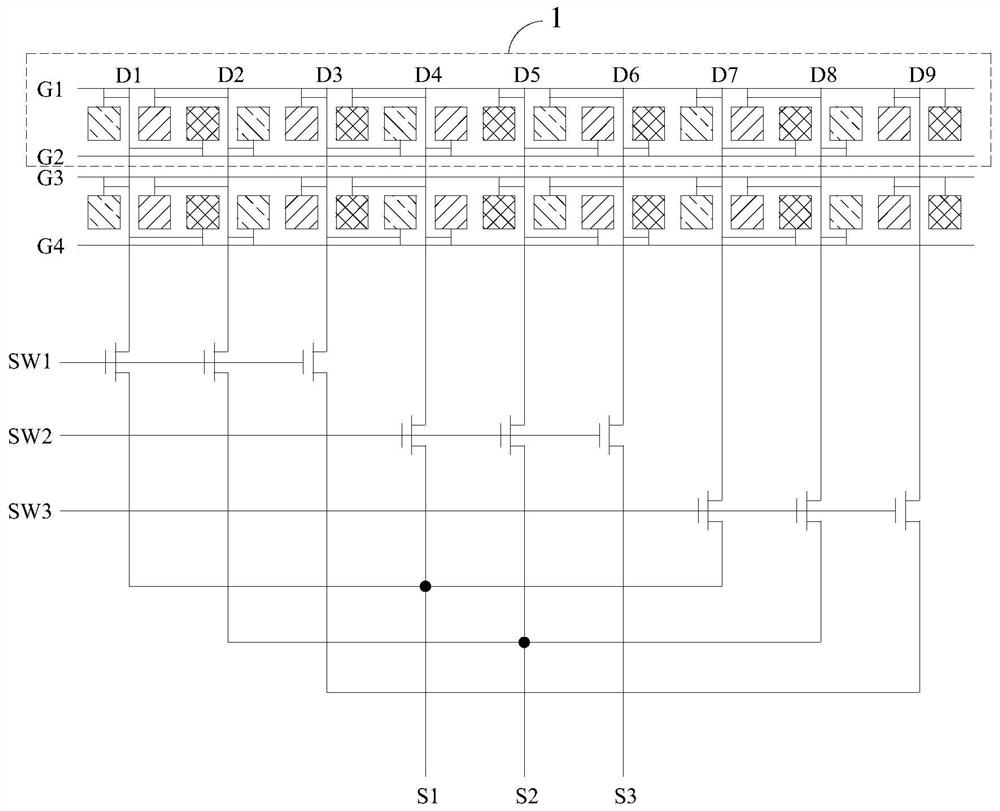

图1为根据本发明的一种特殊显示屏结构的结构示意图;

图2为根据本发明的一种特殊显示屏结构的结构示意图;

图3为根据本发明的一种特殊显示屏结构的源极走线S1的时序图;

图4为根据本发明的一种特殊显示屏结构的源极走线S2的时序图;

图5为根据本发明的一种特殊显示屏结构的源极走线S3的时序图;

图6为根据本发明的一种特殊显示屏结构的驱动方法的步骤流程图;

标号说明:

1、像素单元。

具体实施方式

为详细说明本发明的技术内容、所实现目的及效果,以下结合实施方式并配合附图予以说明。

请参照图1,本发明提供的一种技术方案:

一种特殊显示屏结构,包括两个以上的像素单元、第一Demux走线、第二Demux走线、第三Demux走线和多条栅极走线,一个所述像素单元配置两条栅极走线且位于两条栅极走线之间;

每个所述像素单元包括从左至右依次排列的九列子像素对,位于第一列的所述子像素对至第三列的子像素对划分为第一子像素组,位于第四列的所述子像素对至第六列的子像素对划分为第二子像素组,位于第七列的所述子像素对至第九列的子像素对划分为第三子像素组,一列所述子像素对配置两条数据走线且位于两条数据走线之间,相邻的两列所述子像素对共用一条数据走线,所述第一子像素组中所有的子像素对配置的数据走线分别对应连接有一个TFT开关,所述第二子像素组中所有的子像素对配置的数据走线分别对应连接有一个TFT开关,所述第三子像素组中所有的子像素对配置的数据走线分别对应连接有一个TFT开关;

所述第一子像素组中所有的TFT开关的栅极均与第一Demux走线电连接,所述第二子像素组中所有的TFT开关的栅极均与第二Demux走线电连接,所述第三子像素组中所有的TFT开关的栅极均与第三Demux走线电连接,每个所述TFT开关的输入端分别对应连接有一条源极走线;

位于第n位置的TFT开关、第(n+3)位置的TFT开关和第(n+6)位置的TFT开关共用一条源极走线,其中n的取值为1或2或3。

从上述描述可知,本发明的有益效果在于:

本方案通过设置第一Demux走线、第二Demux走线和第三Demux走线分别与像素单元中的第一子像素组、第二子像素组和第三子像素组中的TFT开关对应连接,采用这样的Layout设计使本方案的源极走线比普通显示屏少了5倍,有利于显示屏的下Border(边界)极度缩小,为全面屏的实现提供了另外的方案设计;由于IC的源极走线数量的减少,使得IC在Y轴上变得更窄,这样可使显示屏达到全面屏效果;本方案设计的像素排列方式可节省白画面的功耗,改善显示屏由于热效应引起的寿命缩短问题。

进一步的,每列所述子像素对包括两个子像素,所述像素单元中的所有子像素以R、G和B的方式依次阵列排布。

进一步的,每条所述数据走线连接两个相邻的子像素,每条所述数据走线连接的两个子像素分别通过对应的栅极走线与数据走线电连接。

进一步的,所述TFT开关的输出端分别与对应的数据走线和两条栅极走线电连接。

进一步的,还包括驱动单元,所述驱动单元分别与多条所述源极走线电连接。

请参照图6,本发明提供的另一种技术方案:

一种特殊显示屏结构的驱动方法,包括以下步骤:

步骤S1、在一个像素单元中,控制两条栅极走线中的一条栅极走线开启;

步骤S2、在一条栅极走线开启期间,依次控制第一Demux走线、第二Demux走线和第三Demux走线开启;在第一Demux走线开启期间,控制源极走线将信号传输至位于第一位置至第三位置的数据走线连接的像素对中;在第二Demux走线开启期间,控制源极走线将信号传输至位于第四位置至第六位置的数据走线连接的像素对中;在第三Demux走线开启期间,控制源极走线将信号传输至位于第七位置至第九位置的数据走线连接的像素对中;

步骤S3、控制两条栅极走线中的另一条栅极走线开启;

步骤S4、在另一条栅极走线开启期间,依次控制第一Demux走线、第二Demux走线和第三Demux走线开启;在第一Demux走线开启期间,控制源极走线将信号传输至位于第一位置至第三位置的数据走线连接的像素对中;在第二Demux走线开启期间,控制源极走线将信号传输至位于第四位置至第六位置的数据走线连接的像素对中;在第三Demux走线开启期间,控制源极走线将信号传输至位于第七位置至第九位置的数据走线连接的像素对中;

步骤S5、循环步骤S1-S4,驱动每个像素单元。

请参照图1至图5,本发明的实施例一为:

请参照图1和图2,一种特殊显示屏结构,包括两个以上的像素单元1、第一Demux走线(Demux走线也叫解复合单元结构走线)、第二Demux走线、第三Demux走线和多条栅极走线,一个所述像素单元1配置两条栅极走线且位于两条栅极走线之间;

请参照图1和图2,每个所述像素单元1包括从左至右依次排列的九列子像素对,位于第一列的所述子像素对至第三列的子像素对划分为第一子像素组,位于第四列的所述子像素对至第六列的子像素对划分为第二子像素组,位于第七列的所述子像素对至第九列的子像素对划分为第三子像素组,一列所述子像素对配置两条数据走线且位于两条数据走线之间,相邻的两列所述子像素对共用一条数据走线,所述第一子像素组中所有的子像素对配置的数据走线分别对应连接有一个TFT开关,所述第二子像素组中所有的子像素对配置的数据走线分别对应连接有一个TFT开关,所述第三子像素组中所有的子像素对配置的数据走线分别对应连接有一个TFT开关;

请参照图1和图2,所述第一子像素组中所有的TFT开关的栅极均与第一Demux走线电连接,所述第二子像素组中所有的TFT开关的栅极均与第二Demux走线电连接,所述第三子像素组中所有的TFT开关的栅极均与第三Demux走线电连接,每个所述TFT开关的输入端分别对应连接有一条源极走线;

请参照图1和图2,位于第n位置的TFT开关、第(n+3)位置的TFT开关和第(n+6)位置的TFT开关共用一条源极走线,其中n的取值为1或2或3。

请参照图1和图2,每列所述子像素对包括两个子像素,所述像素单元1中的所有子像素以R、G和B的方式依次阵列排布。

请参照图1和图2,每条所述数据走线连接两个相邻的子像素,每条所述数据走线连接的两个子像素分别通过对应的栅极走线与数据走线电连接。

请参照图1和图2,所述TFT开关的输出端分别与对应的数据走线和两条栅极走线电连接。

还包括驱动单元,所述驱动单元分别与多条所述源极走线电连接。

源极走线S1通过SW1(第一Demux走线)/SW2(第二Demux走线)/SW3(第三Demux走线)分别与显示屏内部的D1(第一位置的数据走线)/D4(第四位置的数据走线)/D7(第七位置的数据走线)连接,源极走线S2通过SW1/SW2/SW3分别与显示屏内部的D2(第二位置的数据走线)/D5(第五位置的数据走线)/D8(第八位置的数据走线)连接,源极走线S3通过SW1/SW2/SW3分别与显示屏内部的D3(第三位置的数据走线)/D6(第六位置的数据走线)/D9(第九位置的数据走线)连接;采用这样的Layout设计使本方案的源极走线比普通显示屏少了5倍,有利于显示屏的下Border极度缩小,为全面屏的实现提供了另外的方案设计。S1/S2/S3与SW1/SW2/SW3连接直到面内的数据走线D1-D9组成一个循环序列(像素单元1),如图1和图2所示,在显示屏内部会出现多个这样的循环序列,显示屏分辨率不同,此循环序列出现的个数不一样。

请参照图2和图3,图3为源极走线S1的时序图,以S1为例介绍本方案的数据传输过程,当G1打开,SW1打开时,S1传送R子像素资料;当G1打开,SW1关闭,SW2打开时,S1传送R子像素资料;当G1打开,SW1和SW2均关闭,SW3打开时,S1传送R子像素资料;当G2打开,SW1打开时,S1传送G子像素资料;当G2打开,SW1关闭,SW2打开时,S1传送G子像素资料;当G2打开,SW1和SW2均关闭,SW3打开时,S1传送G子像素资料;G3打开时,S1传送数据的情况跟G1打开时是一样的,可参考图3中的G3打开时的情况;G4打开时,S1传送数据的情况跟G2打开时是一样的,可参考图3中的G4打开时的情况。

请参照图2和图4,图4为源极走线S2的时序图,当G1打开,SW1打开时,S2传送B子像素资料;当G1打开,SW1关闭,SW2打开时,S2传送B子像素资料;当G1打开,SW1和SW2均关闭,SW3打开时,S2传送B子像素资料;当G2打开,SW1打开时,S2传送R子像素资料;当G2打开,SW1关闭,SW2打开时,S2传送R子像素资料;当G2打开,SW1和SW2均关闭,SW3打开时,S2传送R子像素资料;G3打开时,S2传送数据的情况跟G1打开时是一样的,可参考图4中的G3打开时的情况;G4打开时,S2传送数据的情况跟G2打开时是一样的,可参考图4中的G4打开时的情况。

请参照图2和图5,图5为源极走线S3的时序图,当G1打开,SW1打开时,S3传送G子像素资料;当G1打开,SW1关闭,SW2打开时,S3传送G子像素资料;当G1打开,SW1和SW2均关闭,SW3打开时,S3传送G子像素;当G2打开,SW1打开时,S3传送B子像素资料;当G2打开,SW1关闭,SW2打开时,S3传送B子像素资料;当G2打开,SW1和SW2均关闭,SW3打开时,S3传送B子像素资料;G3打开时,S3传送数据的情况跟G1打开时是一样的,可参考图5中的G3打开时的情况;G4打开时,S3传送数据的情况跟G2打开时是一样的,可参考图5中的G4打开时的情况。

综上所述,S1的数据循环序列按照R/R/R/G/G/G规律传输数据,并反复按此规律反复传输给显示屏面内;S2的数据循环序列按照B/B/B/R/R/R规律传输数据,并反复按此规律反复传输给显示屏面内;S3的数据循环序列按照G/G/G/B/B/B规律传输数据,并反复按此规律反复传输给显示屏面内。由于S1/S2/S3的数据是以三个R或者三个G或三个B形式重复传递,在纯色画面下,减少了R、G、B子像素电压高低翻转的频率,从而达到降低功耗的目的,同时使得纯色充电率也得到提升。比如在红色画面,对于S1来说,可以直接先传三个R子像素资料,不用像普通显示屏一样,必须传完R子像素资料后,再传G子像素资料(红色画面G子像素资料电压为0),再传B子像素资料(红色画面B子像素资料电压为0),又回来传R子像素资料(电压为±5V),这样的传输方式不仅使得功耗升高,而且还可能使得纯色画面的充电率不好。

请参照图2至图6,本发明的实施例二为:

请参照图6,一种特殊显示屏结构的驱动方法,包括以下步骤:

步骤S1、在一个像素单元1中,控制两条栅极走线中的一条栅极走线开启;

步骤S2、在一条栅极走线开启期间,依次控制第一Demux走线、第二Demux走线和第三Demux走线开启;在第一Demux走线开启期间,控制源极走线将信号传输至位于第一位置至第三位置的数据走线连接的像素对中;在第二Demux走线开启期间,控制源极走线将信号传输至位于第四位置至第六位置的数据走线连接的像素对中;在第三Demux走线开启期间,控制源极走线将信号传输至位于第七位置至第九位置的数据走线连接的像素对中;

步骤S3、控制两条栅极走线中的另一条栅极走线开启;

步骤S4、在另一条栅极走线开启期间,依次控制第一Demux走线、第二Demux走线和第三Demux走线开启;在第一Demux走线开启期间,控制源极走线将信号传输至位于第一位置至第三位置的数据走线连接的像素对中;在第二Demux走线开启期间,控制源极走线将信号传输至位于第四位置至第六位置的数据走线连接的像素对中;在第三Demux走线开启期间,控制源极走线将信号传输至位于第七位置至第九位置的数据走线连接的像素对中;

步骤S5、循环步骤S1-S4,驱动每个像素单元1。

上述的特殊显示屏结构的驱动方法的具体实施例为:

请参照图2和图3,图3为源极走线S1的时序图,以S1为例介绍本方案的数据传输过程,当G1打开,SW1打开时,S1传送R子像素资料;当G1打开,SW1关闭,SW2打开时,S1传送R子像素资料;当G1打开,SW1和SW2均关闭,SW3打开时,S1传送R子像素资料;当G2打开,SW1打开时,S1传送G子像素资料;当G2打开,SW1关闭,SW2打开时,S1传送G子像素资料;当G2打开,SW1和SW2均关闭,SW3打开时,S1传送G子像素资料;G3打开时,S1传送数据的情况跟G1打开时是一样的,可参考图3中的G3打开时的情况;G4打开时,S1传送数据的情况跟G2打开时是一样的,可参考图3中的G4打开时的情况。

请参照图2和图4,图4为源极走线S2的时序图,当G1打开,SW1打开时,S2传送B子像素资料;当G1打开,SW1关闭,SW2打开时,S2传送B子像素资料;当G1打开,SW1和SW2均关闭,SW3打开时,S2传送B子像素资料;当G2打开,SW1打开时,S2传送R子像素资料;当G2打开,SW1关闭,SW2打开时,S2传送R子像素资料;当G2打开,SW1和SW2均关闭,SW3打开时,S2传送R子像素资料;G3打开时,S2传送数据的情况跟G1打开时是一样的,可参考图4中的G3打开时的情况;G4打开时,S2传送数据的情况跟G2打开时是一样的,可参考图4中的G4打开时的情况。

请参照图2和图5,图5为源极走线S3的时序图,当G1打开,SW1打开时,S3传送G子像素资料;当G1打开,SW1关闭,SW2打开时,S3传送G子像素资料;当G1打开,SW1和SW2均关闭,SW3打开时,S3传送G子像素;当G2打开,SW1打开时,S3传送B子像素资料;当G2打开,SW1关闭,SW2打开时,S3传送B子像素资料;当G2打开,SW1和SW2均关闭,SW3打开时,S3传送B子像素资料;G3打开时,S3传送数据的情况跟G1打开时是一样的,可参考图5中的G3打开时的情况;G4打开时,S3传送数据的情况跟G2打开时是一样的,可参考图5中的G4打开时的情况。

综上所述,本发明提供的一种特殊显示屏结构及其驱动方法,本方案通过设置第一Demux走线、第二Demux走线和第三Demux走线分别与像素单元中的第一子像素组、第二子像素组和第三子像素组中的TFT开关对应连接,采用这样的Layout设计使本方案的源极走线比普通显示屏少了5倍,有利于显示屏的下Border(边界)极度缩小,为全面屏的实现提供了另外的方案设计;由于IC的源极走线数量的减少,使得IC在Y轴上变得更窄,这样可使显示屏达到全面屏效果;本方案设计的像素排列方式可节省白画面的功耗,改善显示屏由于热效应引起的寿命缩短问题。

以上所述仅为本发明的实施例,并非因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等同变换,或直接或间接运用在相关的技术领域,均同理包括在本发明的专利保护范围内。

- 一种特殊显示屏结构及其驱动方法

- 一种显示屏驱动芯片、显示屏驱动电路及显示屏驱动方法