制造半导体结构及可控制氧化层厚度的方法

文献发布时间:2023-06-19 10:38:35

技术领域

本发明涉及制造半导体结构的方法,尤指制造半导体结构及可控制氧化层厚度的方法。

背景技术

于存储装置中,编程操作可透过热载子注入(HEI)效应,将电子拉入栅极(例如浮动栅极)而执行。擦除操作可透过福勒-诺德海姆(F-N)穿隧效应,将电子拉出栅极而执行。

为了妥适地执行编程操作及擦除操作,栅极的氧化层厚度应被精确控制。然而,控制栅极的氧化层厚度并非易事。

当栅极的氧化层过厚,则难以拉入或拉出电子,故编程操作及擦除操作易失败。当栅极的氧化层过薄,存放于栅极的电子易逸散而导致漏电流,且结构易产生缺陷,而使可靠度下降。

如上述,控制存储装置的氧化层厚度是个难题。若考量输入输出(IO)装置,还有另一难题如下。

根据输入输出电压的操作电压,输入输出装置应具有适当厚度。然而,输入输出装置及存储装置形成于相同晶圆,且输入输出装置的氧化层是随存储装置的氧化层而形成,这将导致存储装置的氧化层过厚或过薄。

因此,本领域仍欠缺适宜的解决方案,以分别精确控制存储装置及输入输出装置的氧化层厚度。

发明内容

一种制造半导体结构的方法,包括于晶圆上产生第一氧化层;于该第一氧化层上产生氮化硅层;产生复数个沟槽;以氧化材料填补该复数个沟槽以形成复数个浅沟槽隔离区;执行研磨程序以平坦化该氮化硅层的表面;移除该氮化硅层且不移除该第一氧化层;使用光罩以施加光阻,以于第一区域遮盖该第一氧化层的第一部分,且于第二区域露出该第一氧化层的第二部分;及移除该第一氧化层的该第二部分,且保留该第一氧化层的该第一部分。

一种制造半导体结构的方法,包括于晶圆上产生第一氧化层;于该第一氧化层上产生氮化硅层;产生复数个沟槽;以氧化材料填补该复数个沟槽以形成复数个浅沟槽隔离区;执行研磨程序以平坦化该氮化硅层的表面;移除该氮化硅层及该第一氧化层;形成第二氧化层;植入离子以形成复数个井区;使用第一光罩以施加第一光阻,以于第一区域遮盖该第二氧化层的第一部分,且于第二区域露出该第二氧化层的第二部分;及移除该第二氧化层的该第二部分且保留该第二氧化层的该第一部分。

附图说明

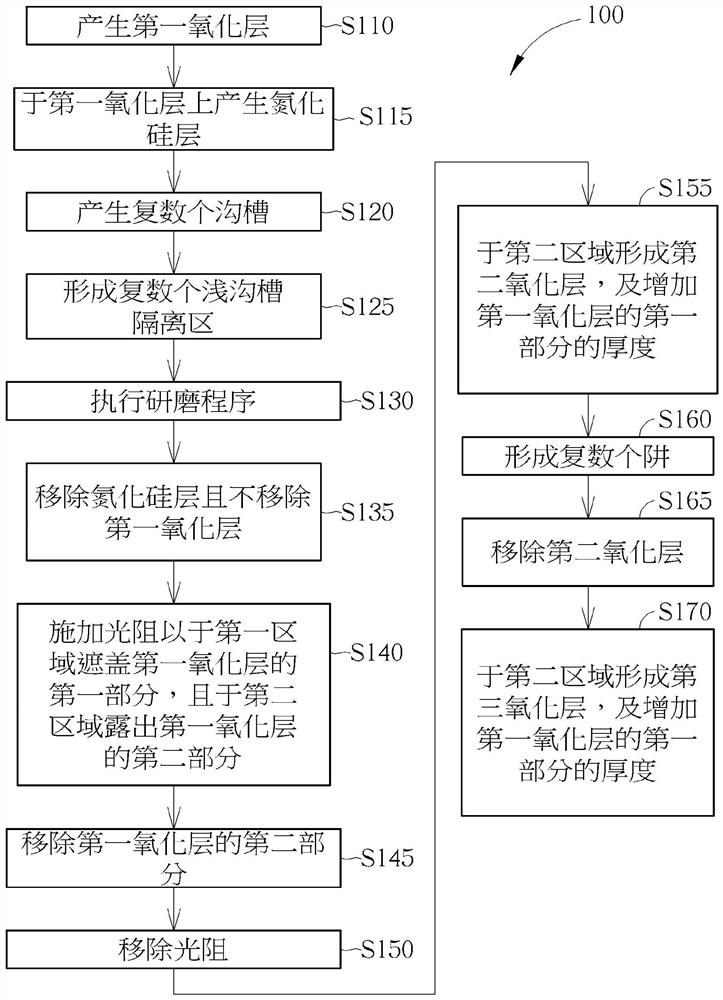

图1为实施例中,制造半导体结构的方法的流程图。

图2至图8为执行图1的方法的制程剖面图。

图9为另一实施例中,制造半导体结构的方法的流程图。

图10至图13为执行图9的方法的制程剖面图。

图14为另一实施例中,制造半导体结构的方法的流程图。

图15至图20为执行图14的方法的制程剖面图。

其中,附图标记说明如下:

1,9,14 半导体结构

100,900,1400 方法

110,120,130,920,930,1440 氧化层

115 氮化硅层

155 晶圆

166,966,1466 光阻

188 浅沟槽隔离区

A1,A2 区域

A21 第一部分

A22 第二部分

S110至S170,S910至S965,S1410至S1485 步骤

TH1,TH3,TH92,TH93 厚度

W1,W2,W3,W4 阱

具体实施方式

图1为实施例中,制造半导体结构1的方法100的流程图。图2至图8为制造半导体结构1的制程剖面图。

步骤S110至S130可对应于图2。步骤S135可对应于图3。步骤S140至S145可对应于图4。步骤S150至S155可对应于图5。步骤S160可对应于图6。步骤S165可对应于图7。步骤S170可对应于图8。

方法100可包含以下步骤。

步骤S110:于晶圆155上产生氧化层110;

步骤S115:于氧化层110上产生氮化硅层115;

步骤S120:产生复数个沟槽;

步骤S125:以氧化材料填补该些沟槽以形成复数个浅沟槽隔离区188;

步骤S130:执行研磨程序以平坦化氮化硅层115的表面;

步骤S135:移除氮化硅层115且不移除氧化层110;

步骤S140:使用光罩以施加光阻166,以于区域A1遮盖氧化层110的第一部分,且于区域A2露出氧化层110的第二部分;

步骤S145:移除氧化层110的第二部分,且保留氧化层110的第一部分

步骤S150:移除光阻166;

步骤S155:执行第一氧化程序以于区域A2形成氧化层120,及增加氧化层110的第一部分的厚度;

步骤S160:植入离子以形成复数个阱W1、W2及W3;

步骤S165:移除氧化层120;及

步骤S170:执行第二氧化程序,以于区域A2形成氧化层130,及增加氧化层110的第一部分的厚度。

根据实施例,图1至图8中,氧化层110可为垫氧化层(pad oxide layer),氧化层120可为牺牲氧化层(sacrificial oxide layer),且氧化层130可为输入输出(input/output,IO)装置的栅极氧化层,又称输入输出栅极氧化层。

垫氧化层可用化学气相沉积(CVD)程序或热氧化程序来制造,且可形成于硅材料及氮化硅材料之间,以防止温度变化或其他原因引发的应力。牺牲氧化层可减少因离子植入导致的损害。可根据输入输出装置的操作电压,将输入输出栅极氧化层的厚度调整到适当值,否则,输入输出装置无法于操作电压下正常运作。

图2至图8中,区域A1可对应于存储装置,且区域A2可对应于输入输出装置。

步骤S125中,填入沟槽的氧化材料可为二氧化硅(SiO

步骤S130的研磨程序可包含化学机械研磨(CMP)程序,也就是化学机械平坦化程序。

步骤S135中,磷酸(例如H

步骤S135至S150中,藉由使用光罩,氧化层110的部分可被选择性地移除,如图4所示。藉由蚀刻程序,可移除未被光阻166遮盖的氧化层110的第二部分。举例而言,氢氟酸(例如HF)或其他适宜的化学物质可用于蚀刻程序。

步骤S155及S170中,第一氧化程序及第二氧化程序的每一者可包含物理气相沉积程序(PVD)、化学气相沉积(CVD)程序、电浆增强化学气相沉积(PECVD)程序及热氧化程序的一者。

步骤S155中,若氧化层120是以沉积程序(例如,电浆增强化学气相沉积)产生,则氧化层110的第一部分的厚度可从顶部增加,因为新增的氧化物可沉积于氧化层110的上。

另一情况中,于步骤S155,若氧化层120是以热氧化程序产生,则氧化层110的第一部分的厚度可从底部增加,因为氧离子可进入氧化层110的第一部分的底部,以产生新增的氧化物。然而,无论使用沉积程序或热氧化程序,皆可形成相似的结构。

步骤S160及图6中,离子可穿透氧化层110及氧化层120而植入,故氧化层110及氧化层120的品质会劣化。为改善输入输出栅极层的品质及厚度,可如图7及步骤S165所述,移除氧化层120,且氧化层130可如图8及步骤S170所述而新增形成。

如图6所示,阱W1、W2及W3的种类可决定于所植入的离子。举例来说,阱W1、W2及W3可分别为(但不限于)n型阱、p型阱及n型阱。

于此例中,阱W1及W2可用以产生非挥发性存储器(NVM)的元件。阱W3可用以产生输入输出装置的元件。

步骤S165及图7中,相似于步骤S145,可用蚀刻程序移除氧化层120,且蚀刻程序可降低氧化层110的厚度。然而,氧化层110的厚度之后又可被增加,如下文所述。

步骤S170及图8中,相似于步骤S155,随着氧化层130的形成,氧化层110的厚度可随之增加。根据第二氧化程序的类型,氧化层110的厚度可从顶部或从底部增加。

于执行步骤S170的第二氧化程序后,如图8所示,氧化层110的厚度TH1可大于氧化层130的厚度TH3。

举例而言,氧化层110的厚度TH1可为70至100埃

氧化层130的厚度TH3可约为50埃,以使区域A2的输入输出装置可操作于2.5伏特的操作电压。

上述的厚度与电压值仅为举例,而非限制实施例的范围。

如图8所示,(位于区域A1的存储装置的)氧化层110及(位于区域A2的输入输出装置的)氧化层130可具有相异厚度。存储装置(也称为存储器单元)的氧化层可较厚。由于氧化层130是重新产生,故可优化输入输出栅极氧化层的品质。藉由使用步骤S140所述的光罩与光阻,可改善对于相异氧化层的厚度的控制。

图9为实施例中,制造半导体结构9的方法900的流程图。图10至图13为制造半导体结构9的制程剖面图。

图9的步骤S910至S930可相似于图1的步骤S110至S130,且对应于图2,故不重述该些步骤及相关的结构剖面图。

步骤S935至S945可对应于图10,步骤S947可对应于图11,步骤S950至S955可对应于图12,步骤S960至S965可对应于图13。

方法900可包含以下步骤。

步骤S910:于晶圆155上产生氧化层110;

步骤S915:于氧化层110上产生氮化硅层115;

步骤S920:产生复数个沟槽;

步骤S925:以氧化材料填补该些沟槽以形成复数个浅沟槽隔离区188;

步骤S930:执行研磨程序以平坦化氮化硅层115的表面;

步骤S935:移除氮化硅层115及氧化层110;

步骤S940:形成氧化层920;

步骤S945:植入离子以形成复数个阱W1、W2及W3;

步骤S947:执行打薄程序以减少氧化层920的厚度;

步骤S950:使用第一光罩以施加光阻966,以于区域A1遮盖氧化层920的第一部分,且于区域A2露出氧化层920的第二部分;

步骤S955:移除氧化层920的第二部分且保留氧化层920的第一部分;

步骤S960:移除光阻966;及

步骤S965:执行氧化程序以于区域A2形成氧化层930,及增加氧化层920的第一部分的厚度。

图10及图13中,氧化层920可为牺牲氧化层,且氧化层930可为输入输出装置的栅极氧化层(也就是输入输出栅极氧化层)。

图10中,氧化层920的厚度可为90埃至120埃。

图11及步骤S947中,打薄程序可为(但不限于)蚀刻程序。于执行打薄程序后,氧化层920的厚度可为40埃至80埃。

图12及步骤S950中,光阻966可相似于图4的光阻166,且用以保留区域A1的氧化层920,其中存储装置可形成于区域A1。图11至图12,氧化层920的厚度可维持相同。步骤S955中,可用蚀刻方式移除区域A2的氧化层920。

图13及步骤S965中,氧化程序可包含化学气相沉积程序、物理气相沉积程序、电浆增强化学气相沉积程序及热氧化程序的至少一者。根据步骤S965的氧化程序的类型,图13的氧化层920的厚度TH92可由顶部或底部增加。

图13中,于执行氧化程序后,氧化层920的厚度TH92可大于氧化层930的厚度TH93。

举例而言,图13中,厚度TH92可增加至约为90埃至120埃,且厚度TH93可约为50埃。

存储装置可形成于区域A1,且输入输出装置可形成于区域A2。根据图13的厚度TH92及TH93,存储装置可操作于3.3伏特的操作电压,且输入输出装置可操作于2.5伏特的操作电压。

图13中,相似于图8,存储装置(也就是存储器单元)的氧化层可更厚。因为氧化层930为新增形成,故可优化输入输出栅极层的品质。藉由使用步骤S950的光罩与光阻,可改善对于相异氧化层的厚度的控制。

图14为实施例中,制造半导体结构14的方法1400的流程图。图15至图20为制造半导体结构14的制程剖面图。图14中,步骤S1410至S1445可相似于图9的步骤S910至S945,且相关结构可相似于图2至图10,故不另重述。

然而,图14的流程中,因形成的浅沟槽隔离区188较多,故浅沟槽隔离区188的数量比图9的流程多。

图14中,步骤S1445至S1450可对应于图15,步骤S1455可对应于图16,步骤S1460至S1465可对应于图17,步骤S1470可对应于图18,步骤S1475可对应于图19,步骤S1480至1485可对应于图20。

如图14所示,方法1400可包含以下步骤。

步骤S1410:于晶圆155上产生氧化层110;

步骤S1415:于氧化层110上产生氮化硅层115;

步骤S1420:产生复数个沟槽;

步骤S1425:以氧化材料填补该些沟槽以形成复数个浅沟槽隔离区188;

步骤S1430:执行研磨程序以平坦化氮化硅层115的表面;

步骤S1435:移除氮化硅层115及氧化层110;

步骤S1440:形成氧化层920;

步骤S1445:植入离子以形成复数个阱W1、W2、W3及W4;

步骤S1450:使用第一光罩以施加光阻966,以于区域A1遮盖氧化层920的第一部分,且于区域A2露出氧化层920的第二部分;

步骤S1455:移除氧化层920的第二部分且保留氧化层920的第一部分;

步骤S1460:移除光阻966;

步骤S1465:执行第一氧化程序以于区域A2形成氧化层930,及增加氧化层920的第一部分的厚度;

步骤S1470:使用第二光罩以施加光阻1466,以遮盖氧化层930的第一部分,及露出氧化层930的第二部分;

步骤S1475:执行蚀刻程序以移除氧化层930的第二部分,及减少氧化层920的第一部分的厚度;

步骤S1480:移除光阻1466;及

步骤S1485:执行第二氧化程序以产生氧化层1440,增加氧化层920的第一部分的厚度,及增加氧化层930的第一部分的厚度。

步骤S1445中,相较于图9的步骤S945,另形成阱W4。

相较于图9,如图14所示,图9的步骤S947可选择性地省略,而不打薄氧化层920。

图14至图20中,阱W1及W3可为n型阱,且阱W2及W4可为p型阱。然而,此仅为举例,而非限制实施例的范围。

图14的流程中,氧化层110(如图2所示)可为垫氧化层,氧化层920(如图20所示)可为牺牲氧化层,氧化层930(如图20所示)可为输入输出装置的栅极氧化层(也就是输入输出栅极氧化层),且氧化层1440是核心装置的氧化层。举例而言,核心装置可包含逻辑门元件组成的电路。

图18及步骤S1470中,氧化层930的第一部分可位于区域A2的第一部分A21,且氧化层930的第二部分可位于区域A2的第二部分A22。

区域A1可对应于存储装置,区域A2的第一部分A21可对应于输入输出装置,且区域A2的第二部分A22可对应于核心装置。

于图1、图9及图14的方法中,可于植入离子后,对氧化层920进行退火,以提升氧化层920的品质。

于步骤S965及S1485中,第一氧化程序及第二氧化程序的每一者包含物理气相沉积程序(PVD)、化学气相沉积(CVD)程序、电浆增强化学气相沉积(PECVD)程序及热氧化程序的一者。

图15及图16中,氧化层920的厚度可为90埃至120埃。

图17及图18中,氧化层920的厚度可增加至约为140埃至170埃。氧化层930的厚度可约为50埃。

图19中,氧化层920的厚度可减少至约为90埃至120埃。氧化层930的厚度可约为50埃。上述的厚度仅为举例,以描述氧化层于相异阶段的厚度变化,而非用以限制实施例的范围。

如图20所示,于执行步骤S1485后,氧化层920可比氧化层930更厚,氧化层930可比氧化层1440更厚。氧化层1440的厚度可小于50埃。

于执行步骤S1485后,可执行标准(STD)逻辑制程,以制造核心装置。

总上,根据图1、图9及图14的方法,藉由使用上述的光阻966及/或光阻1466,存储装置、输入输出装置及核心装置的氧化层可被精确且分别制作,以具有相异厚度。因此,可改善存储装置的编程及擦除,以提高可靠度。输入输出装置可被操作在适宜的操作电压,例如3.3伏特、5伏特、2.5伏特或1.8伏特。先进制程可被更佳地用于制造输入输出装置及存储装置,且可减少氧化层相关的问题。故对于减少本领域的难题,实有助益。

以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 制造半导体结构及可控制氧化层厚度的方法

- 形成于多厚度埋入氧化层上的半导体装置以及制造此半导体装置的方法