光刻工艺的优化方法和光刻方法

文献发布时间:2023-06-19 11:45:49

技术领域

本发明涉及半导体制造技术领域,尤其涉及一种光刻工艺的优化方法和光刻方法。

背景技术

光刻技术是半导体制作技术中至关重要的一项技术,能够实现将图形从掩模版中转移到硅片表面,形成符合设计要求的半导体产品。

在半导体制造中,随着设计尺寸的不断缩小,设计尺寸已经接近或者小于光刻过程中使用的光波波长,光的衍射效应和干涉效应变得越来越明显,导致实际形成的光刻图案相对于掩模版上的图案发生严重畸变,最终在硅片上经过光刻形成的实际图形和设计图形不同,这种现象被称为光学邻近效应(OPE:Optical Proximity Effect)。

光学邻近效应修正(OPC:Optical Proximity Correction)是用于解决光学邻近效应的主要技术。然而,现有通过光学邻近效应修正对图案进行优化的方式仍存在着较多的问题。

发明内容

本发明解决的技术问题是提供一种光刻工艺的优化方法和光刻方法,能够有效降低光斑对曝光后的曝光主图形所造成的影响,进而提升所述曝光主图形与后续目标主图形之间的图像对比度。

为解决上述问题,本发明提供一种光刻工艺的优化方法,包括:提供测试版图和测试光源,所述测试版图中包括若干测试主图形、以及包围所述若干所述测试主图形的若干辅助图形;获取光源掩膜优化模型;根据所述光源掩膜优化模型对所述测试版图与所述测试光源进行预设次数的优化处理,在每次所述优化处理后获取光源掩膜优化数据;根据预设次数的所述优化处理所获取的光源掩膜优化数据,获取优化版图与优化光源。

可选的,每次所述优化处理的方法包括:对所述测试版图进行版图调整,获取中间版图;根据所述光源掩膜优化模型对所述测试光源进行光源调整,获取中间光源;根据所述中间光源对所述中间版图进行模拟曝光,获取曝光版图,所述曝光版图中包括与所述测试主图形相对应的曝光主图形。

可选的,所述版图调整包括:对所述测试主图形的尺寸调整以及对所述辅助图形的密度调整。

可选的,对所述测试主图形的尺寸调整的方法包括:将所述测试主图形的各个边长分割为若干分割段,对若干分割段中的一段或多段进行平移调整。

可选的,对所述辅助图形的密度调整的方法包括:获取所述测试版图的区域面积;对所述测试版图的区域面积内的所述辅助图形的数量进行调整。

可选的,所述光源调整包括:对所述测试光源进行形状的调整、以及对所述测试光源进行照射角度的调整。

可选的,获取每次所述优化处理后的光源掩膜优化数据的方法包括:提供目标版图,所述目标版图中包括与所述曝光主图形相对应的目标主图形;对比所述曝光主图形与所述目标主图形,获取每次所述优化处理后的光源掩膜优化数据。

可选的,每次所述优化处理后的光源掩膜优化数据包括:所述曝光主图形与所述目标主图形之间的边缘位置误差、所述曝光主图形与所述目标主图形之间的工艺变化带宽以及所述曝光主图形的聚焦偏移。

可选的,根据预设次数的所述优化处理所获取的光源掩膜优化数据,获取优化版图与优化光源的方法包括:获取所有光源掩膜优化数据中最小的光源掩膜优化数据;获取最小光源掩膜优化数据的曝光主图形所对应的中间版图与所述中间光源,且以最小光源掩膜优化数据的曝光主图形所对应的中间版图与所述中间光源作为优化版图与优化光源。

相应的,本发明的技术方案中还提供了一种光刻方法,包括:提供测试版图和测试光源,所述测试版图中包括若干测试主图形、以及包围所述若干所述测试主图形的若干辅助图形;获取光源掩膜优化模型;根据所述光源掩膜优化模型对所述测试版图与所述测试光源进行预设次数的优化处理,在每次所述优化处理后获取光源掩膜优化数据;根据预设次数的所述优化处理所获取的光源掩膜优化数据,获取优化版图与优化光源;根据所述优化版图获取芯片掩模版;提供基底;以所述芯片掩模版为掩膜,通过所述优化光源对所述基底进行曝光,在所述基底上形成光刻图形。

可选的,根据所述优化版图获取芯片掩模版的方法包括:通过所述优化版图形成初始芯片掩模版图,所述初始芯片掩模版图与所述优化版图相同或成比例;对所述初始芯片掩模版图进行芯片掩模优化,获取芯片掩模版图;根据所述芯片掩模版图形成芯片掩模版。

可选的,所述芯片掩模优化的方法包括光学邻近效应修正方法或相位转移掩模方法。

可选的,所述基底包括衬底和位于所述衬底上的光刻胶。

与现有技术相比,本发明的技术方案具有以下优点:

本发明的技术方案中,根据所述光源掩膜优化模型对所述测试版图与所述测试光源进行预设次数的优化处理,获取每次所述优化处理后的光源掩膜优化数据;根据每次所述优化处理的光源掩膜优化数据,获取优化版图与优化光源。通过对所述测试版图与测试光源的共同优化处理,能够有效降低光斑对曝光后的曝光主图形所造成的影响,进而提升所述曝光主图形与后续目标主图形之间的图像对比度。

附图说明

图1是一种光刻工艺的优化方法的流程图;

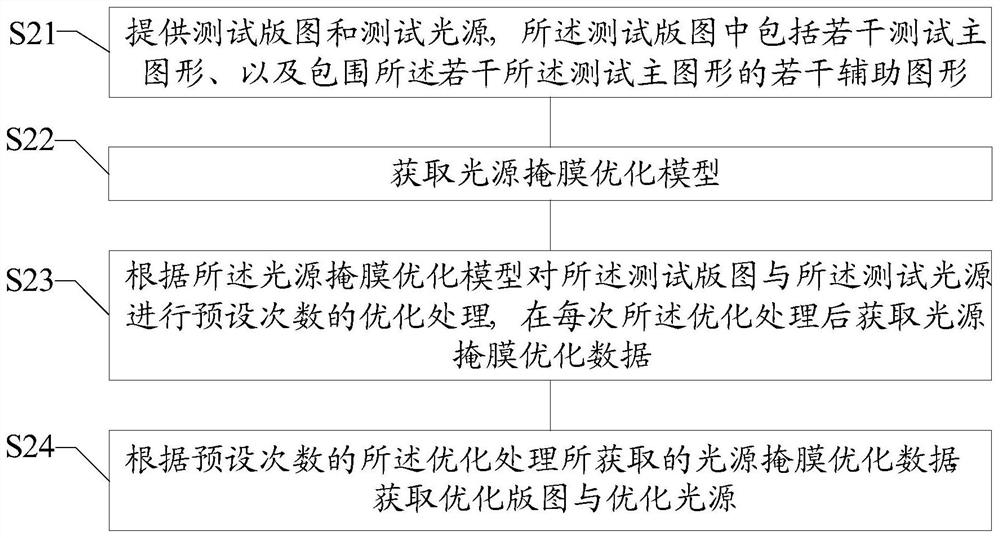

图2是本发明实施例的光刻工艺的优化方法流程图;

图3至图10是本发明光刻工艺的优化方法一实施例各步骤结构示意图。

具体实施方式

正如背景技术所述,现有技术中通过光学邻近效应修正对图案进行优化的方式仍存在着较多的问题。

请参考图1,图1是一种光刻工艺的优化方法的流程图,所述光刻工艺的优化方法包括:

步骤S11,提供测试版图,所述测试版图包括多个测试图形;

步骤S12,对所述测试版图进行光学邻近效应修正;

步骤S13,重复执行步骤S12直至每个所述测试图形满足光刻工艺窗口要求;

步骤S14,获取所述测试版图对应的修正版图,所述修正版图中包括若干与所述测试图形对应的修正图形。

在上述实施例中,对所述测试版图的优化采用的是多次的光学邻近修正实现,而光学邻近修正仅可以对所述测试版图中的图形形状进行修正,对于一些由于光源系统所产生的随机光斑(flare),通过所述光学邻近修正是不可以消除或是降低的。所述光斑会对所述修正图形曝光后的曝光主图形造成一定的影响,导致曝光主图形与后续的目标主图形进行对比时,降低所述曝光主图形与所述目标主图形之间的对比度。

在此基础上,本发明提供一种光刻工艺的优化方法和光刻方法,根据所述光源掩膜优化模型对所述测试版图与所述测试光源进行预设次数的优化处理,获取每次所述优化处理后的光源掩膜优化数据;根据每次所述优化处理的光源掩膜优化数据,获取优化版图与优化光源。通过对所述测试版图与测试光源的共同优化处理,能够有效降低光斑对曝光后的曝光主图形所造成的影响,进而提升所述曝光主图形与后续目标主图形之间的图像对比度。

为使本发明的上述目的、特征和优点能够更为明显易懂,下面结合附图对本发明的具体实施例做详细地说明。

图2是本发明实施例的光刻工艺的优化方法流程图,包括:

步骤S21,提供测试版图和测试光源,所述测试版图中包括若干测试主图形、以及包围所述若干所述测试主图形的若干辅助图形;

步骤S22,获取光源掩膜优化模型;

步骤S23,根据所述光源掩膜优化模型对所述测试版图与所述测试光源进行预设次数的优化处理,在每次所述优化处理后获取光源掩膜优化数据;

步骤S24,根据预设次数的所述优化处理所获取的光源掩膜优化数据,获取优化版图与优化光源。

以下结合附图对所述光刻工艺优化方法的各步骤进行详细说明。

图3至图9,是本发明实施例的一种光刻工艺优化方法中各步骤的结构示意图。

请参考图3与图4,提供测试版图200和测试光源300,所述测试版图200中包括若干测试主图形201、以及包围若干所述测试主图形201的若干辅助图形202。

在本实施例中,所述测试版图200中的测试主图形201在后续的制程是能够形成具有实际功能结构的半导体器件的图形,而若干辅助图形202,虽然会参与后续的模拟曝光,但是这些图形是不会形成具有实际功能结构的半导体器件的,因此可以通过调整所述辅助图形202来实现优化最终测试主图形的目的。

在本实施例中,所述测试光源300为初始光源,在后续的过程中,通过所述测试光源300对所述测试版图进行模拟曝光。

请参考图5,获取光源掩膜优化模型。

对于常规光源掩膜优化模型SMO’

其中,常规测试版图中包括若干常规测试图形,EPE

同时,常规光源掩膜优化模型SMO’

其中,S(x,y)为测试光源的相关参数,M’(X,Y)为常规测试版图中的常规测试图形的相关参数。

在本实施例中,由于所述测试版图200中包括测试主图形201、以及包围所述测试主图形201的若干辅助图形202,因此本实施例中,所述光源掩膜优化模型SMO

其中,S(x,y)为所述测试光源300的相关参数,M(X,Y)为所述测试版图200中的测试主图形201的相关参数,D为所述测试版图200中的辅助图形202的密度。

根据所述光源掩膜优化模型SMO

请参考图6,根据所述光源掩膜优化模型SMO

其中,所述版图调整包括:对所述测试主图形201的尺寸调整以及对所述辅助图形202的密度调整。

请参考图7,图7是图6中A部分放大示意图,对所述测试主图形201的尺寸调整的方法包括:将所述测试主图形201的各个边长分割为若干分割段,对若干分割段中的一段或多段进行平移调整。

根据设计规则,所述测试版图200中的各个所述测试主图形201的特征尺寸CD以及各个所述测试主图形201的分布调整可以在一定阈值范围内进行调整,因此在本实施例中,可以在阈值范围内对各个所述测试主图形201的特征尺寸CD进行一定的调整,以此来满足优化的目的。

所述辅助图形202为不能形成具有实际功能结构的半导体器件的图形,其作用是辅助优化,根据设计规则,可以对所述辅助图形202的密度进行调整,以此来满足优化的目的。

在本实施例中,对所述辅助图形202的密度调整的方法包括:获取所述测试版图200的区域面积;对所述测试版图200的区域面积内的所述辅助图形202的数量进行调整。

由于测试版图200的区域面积固定,因此通过调整测试版图200中的辅助图形202数据来到达对所述辅助图形202密度的调整。

请参考图8,根据所述光源掩膜优化模型SMO

其中,所述光源调整包括:对所述测试光源300进行形状的调整、以及对所述测试光源300进行照射角度的调整。

请参考图9,根据所述中间光源600对所述中间版图500进行模拟曝光,获取曝光版图700,所述曝光版图700中包括与所述测试主图形相对应的曝光主图形701。

在本实施例中,每次所述优化处理的具体过程为:对所述测试版图200中的辅助图形202密度进行调整;在所述辅助图形202密度调整之后,对所述测试版图200中的测试主图形201以及所述测试光源300进行相应的调整;在所述测试版图200中的测试主图形201以及所述测试光源300调整之后,通过调整之后的测试光源300对调整之后的测试版图200进行模拟曝光,获取曝光版图700。

请参考图10,在进行模拟曝光之后,获取光源掩膜优化数据。

在本实施例中,获取每次所述优化处理后的光源掩膜优化数据的方法包括:提供目标版图,所述目标版图中包括与所述曝光主图形701相对应的目标主图形801;对比所述曝光主图形701与所述目标主图形801,获取每次所述优化处理后的光源掩膜优化数据。

所述目标主图形801为优化处理的目标,即理想状态下,曝光主图形701与所述目标主图形801一致。

在本实施例中,每次所述优化处理后的光源掩膜优化数据包括:所述曝光主图形701与所述目标主图形801之间的边缘位置误差(EPE)、所述曝光主图形701与所述目标主图形801之间的工艺变化带宽(PVband)以及所述曝光主图形701的聚焦偏移(Δcf)。

在本实施例中,获取所述曝光主图形701与所述目标主图形801之间的边缘位置误差的方法包括:在每个所述目标主图形801上设置若干第一采样点;在每个所述曝光主图形701上设置若干与所述第一采样点对应的第二采样点;对比所述目标主图形801与所述曝光主图形701,获取每个第一采样点与对应的第二采样点之间的差值,以所述差值作为所述曝光主图形701与所述目标主图形801之间的边缘位置误差。

在本实施例中,所述曝光主图形701与所述目标主图形801之间的工艺变化带宽是指,在集成电路制造光刻工艺中,在给定一组{聚焦点,曝光剂量}条件下用光刻仿真轮廓,工艺变化带宽就是指外轮廓703和内轮廓702之间的区域。

在本实施例中,由于曝光后的曝光主图形较为模糊,需要调整焦距进行观测,使得观测时光束聚集于一点,进而获得清晰的观测图形,因此所述曝光主图形的聚焦偏移Δcf是指将曝光主图形由模糊变为清晰的过程中所改变的焦距值。

请继续参考图10,根据预设次数的所述优化处理所获取的光源掩膜优化数据,获取优化版图与优化光源。

在本实施例中,根据预设次数的所述优化处理所获取的光源掩膜优化数据,获取优化版图与优化光源的方法包括:获取所有光源掩膜优化数据中最小的光源掩膜优化数据;获取最小光源掩膜优化数据的曝光主图形701所对应的中间版图500与所述中间光源600,且以最小光源掩膜优化数据的曝光主图形701所对应的中间版图500与所述中间光源600作为优化版图与优化光源。

最小的光源掩膜优化数据在理想状态下是指边缘位置误差(EPE)、工艺变化带宽(PVband)以及聚焦偏移(Δcf)均最小,然而在实施例中,三者同时达到最小的情况具有一定的不确定性。当边缘位置误差、工艺变化带宽以及聚焦偏移不能同时达到最小时,在本实施例中,通过先选定出三者中的任意两者同时达到最小的情况,剩余一者的选定是基于最小的两者确定情况下的相对最小的数据,并最终以该组数据作为最小的光源掩膜优化数据。

本发明实施例还提供一种光刻方法,包括:提供图2所述的优化版图与优化光源。

根据所述优化版图获取芯片掩模版。

在本实施例中,根据所述优化版图获取芯片掩模版的方法包括:通过所述优化版图形成初始芯片掩模版图,所述初始芯片掩模版图与所述优化版图相同或成比例;对所述初始芯片掩模版图进行芯片掩模优化,获取芯片掩模版图;根据所述芯片掩模版图形成芯片掩模版。

在本实施例中,所述芯片掩模优化的方法包括光学邻近效应修正方法;在其他实施例中,所述芯片掩模优化的方法还可以包括相位转移掩模方法。

所述初始芯片掩模版图与所述优化版图相同指的是,所述初始芯片掩模版图中的图形与优化版图中的图形的形状、尺寸和相对位置相同;所述初始芯片掩模版图与所述优化版图成比例指的是,所述初始芯片掩模版图中的图形与优化版图中的图形的形状和相对位置相同,且初始芯片掩模版图中的图形与优化版图中的图形相似。

提供基底。

所述基底包括衬底以及位于所述衬底上的光刻胶。

在本实施例中,所述光刻胶为光阻材料。

在本实施例中,所述衬底为硅衬底;在其他实施例中,所述衬底还可以为锗衬底、硅锗衬底、半导体上硅、半导体上锗或半导体上硅锗。

以所述芯片掩模版为掩膜,通过所述优化光源对所述基底进行曝光,在所述基底上形成光刻图形。

根据优化光源与优化版图形成的芯片掩膜版对所述基底进行曝光,能够有效降低光斑对曝光后的基底上的图形所造成的影响,进而提升所述基底上形成的图形与目标主图形之间的图像对比度。

虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

- 光刻工艺的优化方法和光刻方法

- 光刻工艺的优化方法及其优化系统和光刻方法