一种AlGaN/GaN垂直型高电子迁移率晶体管及其制作方法

文献发布时间:2023-06-29 06:30:04

技术领域

本发明涉及半导体器件,特别是涉及一种AlGaN/GaN垂直型高电子迁移率晶体管及制作该晶体管的方法。

背景技术

GaN(氮化镓)材料具有大的禁带宽度、高临界击穿电场和高电子饱和漂移速度等特点,因此其在大功率、高温以及高频的电力电子领域有非常广阔的应用前景。目前在GaN基晶体管中,AlGaN(铝镓氮)/GaN垂直型高电子迁移率晶体管是被广泛研究的对象之一。2001年,UmeshK在报告中成功制作并测试了第一个AlGaN/GaN垂直型器件,这是史上第一次成功制作GaN基垂直型器件,揭开了垂直型器件研究的新篇章,具有重要意义。

但是传统的AlGaN/GaN垂直型器件在使用时,存在较低的耐压以及较高的导通损耗的问题。

发明内容

本发明的目的是解决传统的AlGaN/GaN垂直型器件在使用时,存在较低的耐压以及较高的导通损耗的技术问题,而提供一种AlGaN/GaN垂直型高电子迁移率晶体管及其制作方法。

为实现上述目的,本发明所采用的技术方案为:

一种AlGaN/GaN垂直型高电子迁移率晶体管,包括:

GaN材料的衬底;

设置在衬底下表面的漏极;

依次生长在衬底上方的N型漂移区、GaN沟道层和AlGaN势垒层,N型漂移区为氮化镓外延层;

通过离子注入在AlGaN势垒层上表面形成的源区;

设置在源区内的源极;

其特殊之处在于,还包括:

通过对N型漂移区、GaN沟道层和AlGaN势垒层中部贯通刻蚀形成的介质沟槽;在介质沟槽两侧的N型漂移区上部经掺杂形成的P型阻挡层;依次设置在介质沟槽每侧内壁的二氧化硅薄氧化层和SIPOS场板;位于两个SIPOS场板之间且自下而上依次淀积的二氧化硅和多晶硅;设置在多晶硅上方的栅极;位于栅极上表面的钝化层;

介质沟槽两侧的两个源极共接。

进一步地,衬底的掺杂浓度为1×10

N型漂移区的掺杂浓度为8×10

P型阻挡层的掺杂浓度是1×10

进一步地,漏区掺杂浓度为1×10

源区掺杂浓度为1×10

进一步地,多晶硅和二氧化硅的分界线与P型阻挡层和N型漂移区的分界线平齐。

进一步地,N型漂移区的厚度是7um~10um;

P型阻挡层的厚度0.5um~1um;

GaN沟道层厚度为0.04um~0.08um;

AlGaN势垒层厚度为0.01um~0.05um;

二氧化硅薄氧化层厚度为0.02um~0.05um;

SIPOS场板厚度为0.05um~0.5um。

进一步地,AlGaN势垒层中Al组分比例为15%~30%;

SIPOS场板中掺氧比例为15%~35%。

进一步地,SIPOS场板的电阻率为10

本发明还提出一种上述AlGaN/GaN垂直型高电子迁移率晶体管的制作方法,其特殊之处在于:包括以下步骤:

1)在氮化镓材料N

2)在N型漂移区上方生长GaN沟道层;

3)在GaN沟道层上方生长AlGaN势垒层;

4)对N型漂移区、GaN沟道层以及AlGaN势垒层进行刻蚀,形成上下贯通,直达衬底的介质沟槽;

5)在介质沟槽两侧N型漂移区的上方通过P型离子注入和退火形成P型阻挡层;

6)通过离子注入在AlGaN势垒层上表面形成源区;

7)在AlGaN势垒层上表面刻蚀接触孔,在接触孔内淀积金属并刻蚀形成源极,并将介质沟槽两侧的源极共接;

8)在介质沟槽两侧形成二氧化硅薄氧化层;

9)在二氧化硅薄氧化层上通过淀积形成SIPOS场板,并在两侧的SIPOS场板之间下方淀积二氧化硅;

10)在二氧化硅上方淀积多晶硅,在多晶硅上表面淀积形成栅极;

11)在栅极上表面淀积钝化层;

12)衬底下表面通过离子注入形成漏区,漏区下方设置漏极。

本发明的有益效果是:

1、本发明提出的一种AlGaN/GaN垂直型高电子迁移率晶体管,在N型漂移区上部的左、右两端区域掺杂形成两处P型阻挡层,使得作为电流阻挡层的P型阻挡层以及作为缓冲层的N型漂移区之间没有间隙;在器件关断时,多数积累载流子电子消失,SIPOS场板附近漂移区恢复为低掺杂区域,同时通过SIPOS场板电场调制效应提升器件的纵向电场分布,提升了器件的击穿电压(BV)。在器件开态时,器件漂移区上形成多数载流子积累层,SIPOS场板下方高浓度电子区域相当于局部高浓度掺杂,极大的降低了器件的比导通电阻(R

因此,基于半绝缘多晶硅场板的AlGaN/GaN垂直型高电子迁移率晶体管,与传统AlGaN/GaN垂直型器件在相同漂移区厚度和掺杂浓度情况下,半绝缘多晶硅场板AlGaN/GaN器件具有更高的耐压和更低的导通损耗,因此具有更好的性能。

2、本发明提出的一种AlGaN/GaN垂直型高电子迁移率晶体管,在器件关断时,通过在N型漂移区上部经掺杂形成的P型阻挡层起到阻断源端和漏端电流的作用。

3、本发明通过设置的二氧化硅薄氧化层、SIPOS场板和漂移区表面构成一个电容,在器件导通时,受栅压的影响,会在漂移区表面形成多数载流子积累,降低了漂移区的导通电阻。

4、本发明设置在沟槽间的二氧化硅在器件反向击穿时,承担耐压的作用。

附图说明

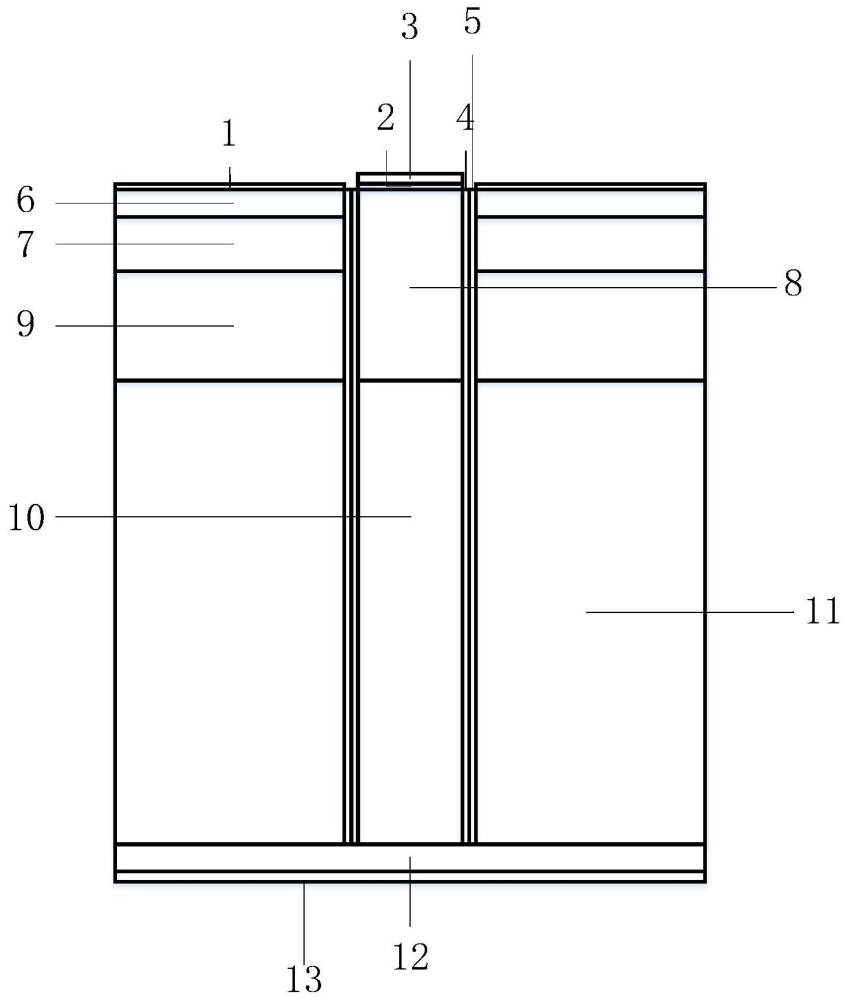

图1是本发明AlGaN/GaN垂直型高电子迁移率晶体管实施例的结构示意图;

图2是本发明实施例与传统AlGaN/GaN垂直型器件的击穿电压对照示意图;

图3是本发明实施例与传统AlGaN/GaN垂直型器件的导通电阻对照示意图。

图中,1-源极;2-栅极;3-钝化层;4-SIPOS场板;5-二氧化硅薄氧化层;6-AlGaN势垒层;7-GaN沟道层;8-多晶硅;9-P型阻挡层;10-二氧化硅;11-N型漂移区;12-衬底;13-漏极。

具体实施方式

为使本发明的目的、优点和特征更加清楚,以下结合附图和具体实施例对本发明提出的一种AlGaN/GaN垂直型高电子迁移率晶体管及其制作方法作进一步详细说明。

场板技术是一种常用的终端技术,广泛地应用于高压功率半导体器件中,通过场板技术可以有效改善器件中的电场分布,从而提高器件的击穿电压。根据工艺的不同,场板可以分为金属场板和电阻场板。电阻场板一般采用半绝缘多晶硅(SIPOS)技术,由于电阻场板为非等势场板,即在场板上有均匀电势压降,从而场板与器件表面之间具有均匀的电势差,因此会在漂移区上产生多数载流子积累,积累的电子会降低器件的比导通电阻(R

基于上述原理,本发明设计了具有半绝缘多晶硅场板的AlGaN/GaN垂直型高电子迁移率晶体管,如图1所示,该具有半绝缘多晶硅场板的AlGaN/GaN垂直型高电子迁移率晶体管结构包括:

氮化镓材料的衬底12,其掺杂浓度为1×10

在衬底12上生长氮化镓外延层作为轻掺杂漂移区,即N型漂移区11,N型漂移区11的厚度为7~10um,掺杂浓度为8×10

N型漂移区11上方形成GaN沟道层7,GaN沟道层7的厚度为0.04um~0.08um。

GaN沟道层7上方形成AlGaN势垒层6,AlGaN势垒层6的厚度为0.01um~0.05um。

在AlGaN势垒层6、GaN沟道层7以及N型漂移区11的中部通过深沟槽刻蚀技术刻介质沟槽,介质沟槽下端贯穿到衬底12。

位于介质沟槽两侧的N型漂移区11上方通过P型离子注入和退火形成P型阻挡层9,P型阻挡层9的厚度为0.5um~1um,掺杂浓度的范围为1×10

通过离子注入在AlGaN势垒层6上表面形成源区,源区掺杂浓度为1×10

在介质沟槽的两侧均形成二氧化硅薄氧化层5,其厚度为0.02um~0.05um,具体数值根据器件击穿电压要求确定。

在二氧化硅薄氧化层5表面形成一定厚度和掺氧比例的SIPOS场板4,SIPOS场板4厚度为0.05um~0.5um,掺氧比例为15%~35%,电阻率为10

位于两个SIPOS场板4之间且自下而上依次淀积二氧化硅10和多晶硅8,多晶硅8上表面形成栅极2,栅极2上表面形成钝化层3。

一种制作上述AlGaN/GaN垂直型高电子迁移率晶体管的方法,包括以下步骤:

1)在氮化镓材料N

2)在N型漂移区11上方形成GaN沟道层7;

3)在GaN沟道层7上方形成AlGaN势垒层6;

4)对AlGaN势垒层6、GaN沟道层7以及N型漂移区11进行刻蚀,形成上下贯通,直达衬底12的介质沟槽;

5)在介质沟槽两侧N型漂移区11的上方通过P型离子注入和退火形成P型阻挡层9;

6)通过离子注入在AlGaN势垒层6上表面形成源区;

7)在AlGaN势垒层6上表面刻蚀接触孔,在接触孔内淀积金属并刻蚀形成源极1,并将两处源极1共接;

8)在介质沟槽两侧形成二氧化硅薄氧化层5;

9)在二氧化硅薄氧化层5上通过淀积形成SIPOS场板4,并在两侧的SIPOS场板4之间下方淀积二氧化硅10;

10)在二氧化硅10上方淀积多晶硅8,淀积的多晶硅8形成栅极2;

11)在栅极2上表面淀积钝化层3;

12)衬底12下表面通过离子注入形成漏区,并形成漏极13。

本发明提出的一种具有半绝缘多晶硅(SIPOS)场板的AlGaN/GaN垂直型高电子迁移率晶体管,该器件具有沟槽栅结构,在N型漂移区11两侧引入两个SIPOS场板4,SIPOS场板4上方与器件的栅电极连接,穿过整个漂移区与器件的衬底12连接,在器件关断时,利用SIPOS场板4的电场调制作用使得器件漂移区电场分布更加均匀,可以提高击穿电压(BV);在器件开态时,器件漂移区上形成多数载流子积累层,SIPOS场板4下方高浓度电子区域相当于局部高浓度掺杂,极大的降低了器件的比导通电阻(R

结合以上优势,相比于传统AlGaN/GaN垂直型高电子迁移率晶体管,本发明具有更高的耐压和更低的导通损耗。

经ISE-TCAD仿真,本发明提出的新型器件的性能较之于传统AlGaN/GaN垂直型器件明显提升,两种器件具有相等的漂移区长度7um时,如图2所示,传统器件击穿电压仅为1640V左右,而新型器件的击穿电压在2087V,提高了27%;如图3所示,传统器件的比导通电阻为0.032mΩ.cm

以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明技术原理的前提下,还可以做出若干改进和替换,这些改进和替换的方案也落入本发明的保护范围。

- 一种AlGaN/GaN垂直型高电子迁移率晶体管及其制作方法

- 基于高K材料的品型栅AlGaN/GaN高电子迁移率晶体管及制作方法