一种高效的星载探测雷达CFAR检测的工程实现方法

文献发布时间:2023-06-19 09:54:18

技术领域

本发明涉及一种高效的星载探测雷达CFAR检测的工程实现方法,属于空间微波遥感技术领域。

背景技术

随着近年来各国对空间领域探索,基于雷达的空间目标探测与识别在空间攻防中扮演着越来越重要的角色。而随着雷达探测技术的发展,雷达功能日趋复杂,软件处理复杂度高,对处理实时性提出更高要求。探测雷达研究领域中一个很重要的研究方向就是如何准确地检测出目标,恒虚警(CFAR,Constant False Alarm Rate)检测是其中一个非常重要的环节,关系到整个雷达系统的好坏。由于雷达接收到的回波信号数据在距离维和多普勒维上都会存在杂波和噪声,因此探测雷达信号处理器通常采用二维CFAR检测:对经过脉冲压缩和动目标检测之后的二维数据进行恒虚警检测,用恒虚警算法,产生自适应门限,与待检测单元的采样值进行比较,若采样值比门限值大,则判断有目标,反之,则判断没有目标。

典型的探测雷达信号处理器采用FPGA+DSP架构,需要在很短的帧周期内完成对一帧数据的二维处理,而二维CFAR检测是其中复杂度较高、耗时较久的一个步骤,提高CFAR检测处理速度是星载探测雷达实时处理中的关键一环。

工程实现中,二维CFAR主要在DSP中实现。DSP的功能主要用于计算,其运算速度快和运算精度高,且对二维数据读写操作时程序设计较为灵活。但DSP只能使用串行指令,在运算时还需要考虑到指令周期,因此在完成CFAR检测中的对于二维数据的遍历和比对处理耗时较长,工程应用中处理效率并不高,不适合探测雷达这类需要快速搜索捕获的处理需求。

而在FPGA资源足够的情况下,也可以通过FPGA实现CFAR检测。相比较于DSP,FPGA具备并行处理能力,逻辑运算速度快、集成度高,但CFAR检测需要对数据进行遍历,不适合于并行处理,难以发挥FPGA的并行处理优势,且FPGA主工作钟速率有限,实际应用中基于FPGA实现CFAR检测算法效率也不够高,难以满足处理实时性的需求。

发明内容

本发明要解决的技术问题是:克服现有技术的不足,提供了一种高效的星载探测雷达CFAR检测的工程实现方法,FPGA对回波数据进行脉冲压缩和动目标检测等处理后,获取二维数据,并对二维数据分块查找最大值,同时计算噪声区域的功率均值,并将最大值信息和噪声功率均值转发给DSP。DSP完成帧内多个过门限点的聚类和帧之间的聚类,输出目标信息。本专利克服了现有CFAR检测工程实现方法计算速度慢、不利于对目标快速捕获的缺点,通过优化实现流程、拆解检测步骤,显著降低了时间开销,并利于工程实现;并通过帧内和帧之间两次聚类处理降低了虚警率,并实现了对目标的快速捕获,提升了目标检测性能。

本发明目的通过以下技术方案予以实现:

一种高效的星载探测雷达CFAR检测的工程实现方法,包括如下步骤:

S1、FPGA对回波数据进行脉冲压缩和动目标检测后,获取二维数据;

S2、将所述二维数据分为N块;在二维数据中选取噪声区域;

S3、FPGA按S2中的分块结果,获得每块数据中的最大值和该最大值在二维数据中的行列位置;FPGA统计噪声区域的功率均值;

S4、FPGA将每块数据中的最大值和该最大值在二维数据中的行列位置、噪声区域的功率均值发送给DSP;其中行坐标对应于目标的距离信息,列坐标对应于目标的速度信息;

S5、当前处理的为第i帧数据;

S6、DSP根据噪声区域的功率均值、预设的虚警概率计算检测门限,将每块数据中的最大值与检测门限比较,确定大于等于检测门限的M

S7、如果M

S8、如果M

S9、如果M

S10、如果i等于1,则输出当前帧的目标信息;如果i大于1,DSP判断上一帧是否有检测结果,若无则输出当前帧的目标信息,若有则将当前帧的目标信息与上一帧的目标信息进行聚类,得到T

S11、如果T

上述高效的星载探测雷达CFAR检测的工程实现方法,优选的,S9中,DSP对M

上述高效的星载探测雷达CFAR检测的工程实现方法,优选的,S10中,当前帧的目标信息与上一帧的目标信息进行聚类的方法为:

将当前帧的每一个目标信息点与上一帧的任何一个目标信息点进行比较,计算行和列的位置差,如果行坐标差小于等于D

一种高效的星载探测雷达CFAR检测装置,包括FPGA和DSP;

其中,FPGA用于获取回波二维数据;然后将所述二维数据分为N块;在二维数据中选取噪声区域;FPGA按分块结果,获得每块数据中的最大值和该最大值在二维数据中的行列位置,FPGA统计噪声区域的功率均值;FPGA将每块数据中的最大值和该最大值在二维数据中的行列位置、噪声区域的功率均值发送给DSP;其中行坐标对应于目标的距离信息,列坐标对应于目标的速度信息;

DSP根据噪声区域的功率均值、预设的虚警概率计算检测门限,将每块数据中的最大值与检测门限比较,确定大于等于检测门限的M

上述高效的星载探测雷达CFAR检测装置,优选的,当一帧数据中M

上述高效的星载探测雷达CFAR检测装置,优选的,DSP对M

上述高效的星载探测雷达CFAR检测装置,优选的,DSP对当前帧的目标信息与上一帧的目标信息进行聚类的方法为:

将当前帧的每一个目标信息点与上一帧的任何一个目标信息点进行比较,计算行和列的位置差,如果行坐标差小于等于D

本发明相比于现有技术具有如下有益效果:

(1)本发明充分发挥了FPGA与DSP的优势,将CFAR中最为耗时的数据遍历过程嵌入FPGA数据流中,显著降低时间开销,实现了对星载探测雷达回波数据的实时处理。

(2)本发明预设的分块信息可以结合目标特性灵活设定,适用于多种应用场景。对于非探测范围的速度、距离区域可以减少分块个数,在重点检测区域增加分块个数,便于快速定位目标。

(3)本发明通过帧内、帧之间两级聚类有效降低了虚警率,提升了目标检测性能。本发明帧内聚类通过预设的距离、速度上限判决,帧之间聚类增加了对距离下限的判决,可以快速剔除静止目标,特别适用于星载探测雷达应用领域中对动目标的搜索跟踪前景。

(4)本发明采取了帧内、帧之间两级聚类,相比于常规的单次聚类,在单目标跟踪场景中,可以实现两帧处理周期内快速由捕获转为跟踪,响应速度快。

(5)本发明相比于传统过的CFAR工程实现,通过优化实现流程、拆解检测步骤,降低了CFAR算法的工程实现难度,代码通用性强、移植性强。

附图说明

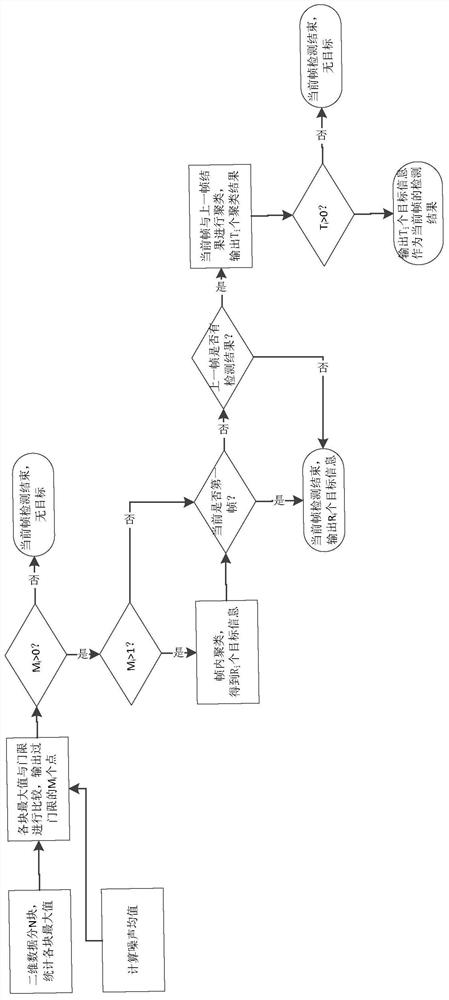

图1为星载探测雷达CFAR检测的工程实现方法流程图。

图2为FPGA分块处理示意图。

具体实施方式

为使本发明的目的、技术方案和优点更加清楚,下面将结合附图对本发明的实施方式作进一步详细描述。

一种高效的星载探测雷达CFAR检测装置及工程实现方法,如图1所示:

(1)FPGA中实现脉压处理和MTD等处理;

(2)结合目标特性对步骤(1)得到的二维数据进行分块,如图2所示,假设数据分为N块;选取噪声区域;

(3)FPGA中在输出平方率检波结果时按照步骤(2)中的分块对各块数据流进行比对,输出各块的最大值和其行列位置,假设第n块最大值为A

(4)FPGA将步骤(3)计算出N个最大值的幅度和行列位置以及噪声区域的功率均值发给DSP;

(5)假设当前处理的为第i帧数据。

(6)DSP根据噪声区域的功率均值计算检测门限,并将收到的各块最大值与门限进行比较输出过门限的M

(7)如果M

(8)如果M

(9)如果M

(10)如果当前处理的为第一帧数据,即i等于1,则无需进行帧之间聚类,直接输出当前帧的目标信息;

(11)如果i大于1,DSP需要判断上一帧是否有检测结果,如果无结果则直接输出当前帧的目标信息;如果上一帧有检测结果,则需将步骤(8)中计算得到的1个目标(M

步骤(9)中的帧内聚类方法为:M

步骤(11)中的帧之间聚类方法为:当前帧的R

步骤(9)中给定值W、V取值方法如下,典型的星载探测雷达为对单个运动目标的捕获和跟踪,设定W和V为了避免出现距离向或方位向的波形主瓣出现在两个块中,因此W设定为距离向主瓣所占行坐标宽度,V设定为方位向主瓣所占列坐标宽度。

步骤(11)中给定值D

本发明说明书中未作详细描述的内容属本领域技术人员的公知技术。

本发明虽然已以较佳实施例公开如上,但其并不是用来限定本发明,任何本领域技术人员在不脱离本发明的精神和范围内,都可以利用上述揭示的方法和技术内容对本发明技术方案做出可能的变动和修改,因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化及修饰,均属于本发明技术方案的保护范围。

- 一种高效的星载探测雷达CFAR检测的工程实现方法

- 一种基于毫米波雷达动态保护单元的CFAR检测方法