FPGA在轨重构控制系统及方法

文献发布时间:2023-06-19 12:10:19

技术领域

本发明涉及在轨重构技术,尤其与一种FPGA在轨重构控制系统及方法有关。

背景技术

目前,航天电路中FPGA重构的主要方法是通过一个FPGA(控制FPGA)采用Selectmap的方法去重构另外一个FPGA(重构FPGA)。控制FPGA外部连接多块不同的FLASH,每块FLASH中存储不同的重构FPGA的程序,根据重构FPGA在不同时刻的功能需要控制FPGA通过Selectmap时序将相应的程序加载到重构FPGA,实现位流的切换。这种方法能够实现重构FPGA位流切换的种类有限,控制系统复杂,不能够发挥重构FPGA的灵活配置的功能,控制FPGA外部的FLASH中的程序都是在器件上天之前烧写好的,一旦器件上天之后,它的程序将无法更改,不能够满足重构FPGA位流根据地面需求变化实时变化的要求,并且这种方式没有考虑到重构FPGA的单粒子翻转、锁定等问题,在航天领域应用具有较大的风险性。

发明内容

针对上述相关现有技术不足,本发明提供一种FPGA在轨重构控制系统及方法,在重构失败时可通过上位机控制SoC让其复位,自动加载引导程序,提高了软件上注控制的可靠性,并能定时刷新,增加抗辐射能力,降低了FPGA软件在轨重构的风险性。

为了实现本发明的目的,拟采用以下方案:

一种FPGA在轨重构控制系统,包括:CPU处理器以及与其连接的一个重构FPGA芯片、一个SRAM芯片、三个FLASH芯片、一个刷新芯片,刷新芯片连接重构FPGA芯片,并连接有一个配置FLASH;

CPU处理器采用SoC2008芯片,用于通过以太网接口芯片或1553B接口芯片从上位机接收FPGA原始重构程序、CPU引导程序、FPGA重构程序,并分别存储于一个FLASH芯片中;并用于通过以太网接口芯片或1553B接口芯片从上位机接收复位重启信号;

刷新芯片用于将SoC2008芯片传输的FPGA重构程序或FPGA原始重构程序加载于配置FLASH,并用于根据SoC2008芯片发送的复位信号进行复位以实现将FPGA重构程序或FPGA原始重构程序加载于重构FPGA芯片,实现在轨重构。

SRAM芯片是抗辐照512k 40位的存储器。

一个FLASH芯片用于存储CPU引导程序以作为备份,一个FLASH芯片用于存储FPGA原始重构程序以作为备份,一个FLASH芯片用于缓存FPGA重构程序。

进一步,系统还包括电源供电芯片,电源供电芯片连接外部程控电源,用于将程控电源的输入转换后为各芯片供电。

进一步,SoC2008芯片还连接有四路差分驱动器,四路差分驱动器通过RS422接口连接上位机,用于从上位机接收数据至SoC2008芯片。

一种FPGA在轨重构控制方法,采用FPGA在轨重构控制系统实现,包括如下步骤:

S100、重构软件上传:

SoC2008芯片通过以太网接口芯片或1553B接口芯片从上位机接收FPGA原始重构程序、CPU引导程序,并分别存储于一个FLASH芯片中,作为原始备份;

SoC2008芯片通过以太网接口芯片或1553B接口芯片从上位机接收一个复位重启信号,并重启自动加载CPU引导程序和FPGA原始重构程序,用于实现CPU的引导程序自动加载和FPGA重构功能验证;

S200、FPGA软件在轨重构:

SoC2008芯片通过以太网接口芯片或1553B接口芯片从上位机接收当前需要加载的FPGA重构程序,并在一个FLASH芯片中缓存;

SoC2008芯片通过UART串口将缓存的FPGA重构程序经过刷新芯片加载到配置FLASH;

加载完成后,通过SoC2008芯片给刷新芯片发送一个复位信号,使刷新芯片复位;

通过预先配置刷新芯片的状态寄存器将其设置为复位后主动加载配置FLASH中的FPGA重构程序数据到重构FPGA,实现FPGA软件在轨重构。

步骤S100中,FLASH芯片对CPU引导程序进行存放时,从FLASH芯片的起始地址开始存放,在SoC2008芯片重启时,默认从FLASH芯片的0x00000000地址开始访问,SoC2008芯片自动加载CPU引导程序,原始功能保持不变。

步骤S200中,在重构FPGA被重构后出现不正常时,SoC2008芯片通过UART串口将FPGA原始重构程序经过刷新芯片加载到配置FLASH;加载完成后,通过SoC2008芯片给刷新芯片发送一个复位信号,使刷新芯片复位,通过预先配置刷新芯片的状态寄存器将其设置为复位后主动加载配置FLASH中的FPGA原始重构程序数据到重构FPGA,使重构FPGA恢复正常。

进一步,在以太网接口芯片或1553B接口芯片于上位机的上注链路中其中一个出错时,SoC2008芯片给上位机发送切换信号,上位机将切换至另一个上注链路进行数据传输。

进一步,每次SoC2008芯片加载CPU引导程序成功后,将给上位机发送CPU加载成功信号;每次FPGA加载成功后,向SoC2008芯片发送FPGA重构成功信号,SoC2008芯片将FPGA重构成功信号发送于上位机,上位机对CPU加载成功信号及FPGA重构成功信号予以显示。

本发明的有益效果在于:

1、在重构失败时可通过上位机控制SoC让其复位,自动加载引导程序,提高了软件上注控制的可靠性,并能定时刷新,增加抗辐射能力,降低了FPGA软件在轨重构的风险性;

2、充分考虑到了航天电路的软件维护困难、可靠性和抗辐照性要求高等特点,提高了软件上注控制的可靠性,降低了FPGA软件在轨重构的风险性,在航天领域具有较大的应用前景;

3、实现高可靠性、低故障率的FPGA在轨重构控制,并实现对上传链路的冗余控制;节约系统成本,还可实现卫星等航天器的FPGA控制器在轨修改程序的功能,系统操作简单。

附图说明

本文描述的附图只是为了说明所选实施例,而不是所有可能的实施方案,更不是意图限制本申请的范围。

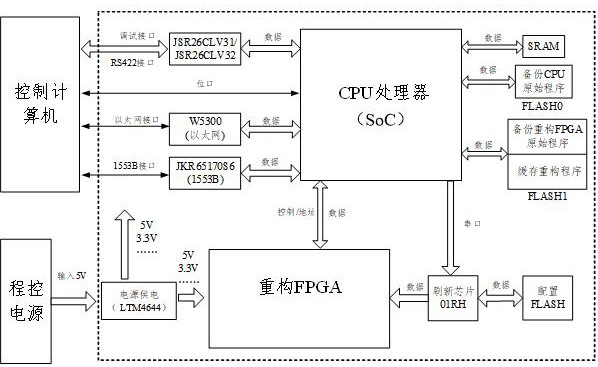

图1为本申请实施例的系统结构图。

图2为本申请实施例的CPU引导程序注入流程示意框图。

图3为本申请实施例的FPGA重构程序在轨重构数据流路径示意框图。

图4为本申请实施例的CPU和FPGA重构失败后的保护措施示意框图。

图5为本申请实施例的FPGA加载过程的原理图。

图6为本申请实施例的FPGA配置FLASH编程时的数据口D0的波形。

图7为本申请实施例的FPGA重构成功时标志位DONE的波形。

图8为本申请实施例的刷新芯片设置每5s刷新一次时CCLK的波形。

具体实施方式

为使本发明实施例的目的、技术方案和优点更加清楚,下面结合附图对本发明的实施方式进行详细说明,但本发明所描述的实施例是本发明一部分实施例,而不是全部的实施例。

本实例提供一种FPGA在轨重构控制系统及基于该系统的控制方法。

具体的,如图1所示,FPGA在轨重构控制系统包括:CPU处理器以及与其连接的一个重构FPGA芯片、一个SRAM芯片、三个FLASH芯片、一个刷新芯片、电源供电芯片,刷新芯片连接重构FPGA芯片,并连接有一个配置FLASH。

重构FPGA芯片采用JFM4VSX55RT,内部包含了可编程逻辑模块(CLB)、通用输入输出模块(IOB)以及多种IP资源,可通过JTAG、串行模式或并行模式现场配置,灵活实现各种所需功能。

CPU处理器采用SoC2008芯片,用于通过以太网接口芯片或1553B接口芯片从上位机接收FPGA原始重构程序、CPU引导程序、FPGA重构程序,并分别存储于一个FLASH芯片中。具体的,一个FLASH芯片用于存储CPU引导程序以作为备份,一个FLASH芯片用于存储FPGA原始重构程序以作为备份,一个FLASH芯片用于缓存FPGA重构程序。

SoC2008芯片还用于通过以太网接口芯片或1553B接口芯片从上位机接收复位重启信号。

刷新芯片采用JFMRS01RH,具备刷新、回读和重构等功能,用于将SoC2008芯片传输的FPGA重构程序或FPGA原始重构程序加载于配置FLASH,并用于根据SoC2008芯片发送的复位信号进行复位以实现将FPGA重构程序或FPGA原始重构程序加载于重构FPGA芯片,实现在轨重构。

SRAM芯片是抗辐照512k 40位的存储器。

电源供电芯片连接外部程控电源,用于将程控电源的输入转换后为各芯片供电。电源供电芯片可以采用电源转换芯片LTM4464,将外部的5V转换为3.3V、1.2V、1.8V等电压给各芯片供电。

SoC2008芯片还连接有四路差分驱动器,四路差分驱动器通过RS422接口连接上位机,用于从上位机接收数据至SoC2008芯片。

本实例的FPGA在轨重构控制方法,包括如下步骤:

S100、重构软件上传:

控制计算机/上位机通过以太网接口芯片或1553B接口芯片将FPGA原始重构程序、CPU引导程序传输到SoC2008芯片,SoC2008芯片将它们分别存储于一个FLASH芯片中,作为原始备份。传输完成后,控制计算机/上位机通过以太网接口芯片或1553B接口芯片向SoC2008芯片发送一个复位重启信号,SoC2008芯片接收复位重启信号后,进行重启并自动加载CPU引导程序和FPGA原始重构程序,实现CPU的引导程序自动加载和FPGA重构功能验证。

其中,SoC2008芯片外面的两个FLASH芯片,分别独立存储CPU引导程序、FPGA原始重构程序,保证重构失败后CPU的原功能不变。具体数据路线图如图 2所示。SoC2008芯片重启时,默认会从外部存储器的0x00000000地址开始访问,因此外部的FLASH存储程序时,CPU引导程序从FLASH的起始地址开始存放,这样可以保证如果FPGA重构失败,通过上位机控制SoC2008芯片让其复位重启,SoC2008芯片可以自动加载引导程序,其原始功能可以保证不变,提高CPU控制系统的可靠性。

S200、FPGA软件在轨重构:

本系统通过刷新芯片对 NOR 型64Mb FLASH存储器JFM29LV641RH,即配置FLASH进行码流擦除、编程,对FPGA软件进行加载重构。具体数据路线图如图 3所示。

控制计算机/上位机通过以太网接口芯片或1553B接口芯片将当前需要加载的FPGA重构程序发送到SoC2008芯片,SoC2008芯片将其缓存于一个FLASH芯片中。SoC2008芯片通过UART串口将缓存的FPGA重构程序经过刷新芯片加载到配置FLASH;加载完成后,通过SoC2008芯片给刷新芯片发送一个复位信号,使刷新芯片复位;通过预先配置刷新芯片的状态寄存器将其设置为复位后主动加载配置FLASH中的FPGA重构程序数据到重构FPGA,实现FPGA软件在轨重构。

其中,SoC2008芯片外面的一个FLASH芯片存储有重构前FPGA的程序,即FPGA原始重构程序,可以保证一旦FPGA重构后功能不正常,SoC2008芯片可以把重构前FPGA的程序通过以上流程加载到FPGA中,使得即使重构后FPGA功能出现问题,也能保证其之前的功能不变,并且刷新芯片也具备定时刷新的功能,增加了FPGA的抗辐照能力,提高了FPGA的可靠性,对于FPGA在航天上的应用具有重要意义。

本实例的控制系统及控制方法具有重构可靠性和安全性控制技术,如图4所示,具体是:

在步骤S100中,FLASH芯片对CPU引导程序进行存放时,从FLASH芯片的起始地址开始存放,在SoC2008芯片重启时,默认从FLASH芯片的0x00000000地址开始访问,SoC2008芯片自动加载CPU引导程序,原始功能保持不变。

在步骤S200中,在重构FPGA被重构后出现不正常时,SoC2008芯片通过UART串口将FPGA原始重构程序经过刷新芯片加载到配置FLASH;加载完成后,通过SoC2008芯片给刷新芯片发送一个复位信号,使刷新芯片复位,通过预先配置刷新芯片的状态寄存器将其设置为复位后主动加载配置FLASH中的FPGA原始重构程序数据到重构FPGA,使重构FPGA恢复正常。

本实例的控制系统及控制方法还具有上注链路故障的安全性措施,具体是:

在以太网接口芯片或1553B接口芯片于上位机的上注链路中其中一个出错时,SoC2008芯片给上位机发送切换信号,上位机将切换至另一个上注链路进行数据传输。

本实例的重构成功的验证方式:

每次SoC2008芯片加载CPU引导程序成功后,将给上位机发送CPU加载成功信号;每次FPGA加载成功后,向SoC2008芯片发送FPGA重构成功信号,SoC2008芯片将FPGA重构成功信号发送于上位机,上位机对CPU加载成功信号及FPGA重构成功信号予以显示。

试验结果:

板子上电后,首先控制计算机/上位机通过以太网接口芯片将FPGA的重构程序加载到SoC2008芯片外部的FLASH芯片中,SoC2008芯片的串口以115200 b/s的速度把程序经过刷新芯片写入重构FPGA外部的配置FLASH中,由于重构FPGA的数据位流有30Mb左右,再加上串口传输过程的校验码,这个写入过程大约需要8分钟。程序经过串口写入配置FLASH中后,SoC2008芯片的GPIO给刷新芯片发送一个复位信号,刷新芯片复位后自动加载配置FLASH中的数据,通过重构FPGA的Selectmap接口将配置位流通过并行方式加载到重构FPGA中,这个过程大约几秒钟就可以完成。FPGA加载过程的原理图如图 5所示。

FPGA配置FLASH编程时的数据口D0的波形如图 6所示。FPGA配置FLASH编程结束后,SoC2008芯片控制刷新芯片复位,复位后刷新芯片自动加载程序,重构FPGA开始重构,重构成功后,重构FPGA的DONE管脚会由低电平变为高电平,具体的DONE电平变化波形如图 7所示,重构FPGA加载成功后会向SoC2008芯片的GPIO发送一个信号,SoC2008芯片将重构成功的结果发送给上位机,在上位机界面中显示出来。

刷新芯片设置每5s刷新一次,刷新时CCLK的波形如8图所示,证明刷新正常。

本实例充分考虑到了航天电路的软件维护困难、可靠性和抗辐照性要求高等特点,提高了软件上注控制的可靠性,降低了FPGA软件在轨重构的风险性,在航天领域具有较大的应用前景。

以上所述仅为本发明的优选实施例,并不表示是唯一的或是限制本发明。本领域技术人员应理解,在不脱离本发明的范围情况下,对本发明进行的各种改变或同等替换,均属于本发明保护的范围。

- FPGA在轨重构控制系统及方法

- 一种基于FPGA的宇航电子系统在轨重构方法及系统