用于5G NR的快速伪随机序列生成方法和系统

文献发布时间:2023-06-19 18:34:06

技术领域

本发明涉及通信技术领域,具体地,涉及用于5G NR的快速伪随机序列生成方法和装置。

背景技术

对于典型的5G NR通信系统如图1所示,基站侧下行信息通过伪随机序列加扰(Scrambling)后发送出去,用户设备接收到信号后,需要解扰(De-Scrambling)恢复出下行信息;用户设备将上行信息通过加扰后发送出去,基站接收信号后,通过解扰恢复上行信息。

5G NR通信场景复杂,不同场景下的伪随机序列内容由初始值x

硬件系统通常基于线性反馈移位寄存器(Linear Feedback Shift Register,orLFSR)结构,每次生成一个1bit伪随机数据,对于一般场景,通过1600次运算找到其伪随机序列的有效开始位置;对于PBCH编码输出数据加扰/解扰过程,最多需要7648次运算才能找到其伪随机序列的有效开始位置;对于PDSCH DMRS序列的生成过程,最多需要47800次运算才能找到其伪随机序列的有效开始位置。而这些有效开始位置之后得到的伪随机序列才能用于相关数据加扰/解扰或信号生成,因此该运算过程造成系统处理极大延时并功耗的浪费。

专利文献US08793295B2(申请号:US13184646)公开了一种包括第一电路和第二电路的装置。第一电路可以被配置为响应于第一m序列和第二m序列产生伪随机序列,其中第一m序列以预先计算的常数初始化,并且第二m序列被初始化在预定义的初始序列和预先计算的值的表上,指示初始序列的哪些组分参与初始化第二个m序列。第二电路可以被配置为存储预先计算的值的表。该专利仅支持LTE应用场景,且当序列的长度N值较大时,需要极大的存储成本。

专利文献CN109375897B(申请号:201710657524.1)公开了一种伪随机序列的生成方法,根据N个第一初始数据和N个第二初始数据,分别计算N个第一数据和N个第二数据,并分别作为第一移位寄存器的初始数据和第二移位寄存器的初始数据。根据第一移位寄存器和第二移位寄存器的初始数据可通过一个时钟周期生成伪随机序列中的第一个数据,并且每一个时钟周期产生伪随机序列中的一个数据,最终生成伪随机序列。

发明内容

针对现有技术中的缺陷,本发明的目的是提供一种用于5G NR的快速伪随机序列生成方法及系统。

根据本发明提供的一种用于5G NR的快速伪随机序列生成方法,包括:

步骤S1:识别伪随机序列应用场景的有效起始位置n

步骤S2:基于识别的伪随机序列应用场景的有效起始位置n

步骤S3:利用预设应用场景有效起始位置的状态变量X1

优选地,所述伪随机序列应用场景包括PBCH编码数据加扰/解码过程场景、PDSCHDMRS生成过程场景以及预设一般场景;

所述PBCH编码数据加扰/解码过程场景的伪随机比特的有效起始位置n

n

所述PDSCH DMRS生成过程场景的伪随机比特的有效起始位置n

n

所述预设一般场景的伪随机比特的有效起始位置n

优选地,所述步骤S2采用:

步骤S2.1:获取预设应用场景下第1个m序列有效起始位置n

步骤S2.2:第1个m序列预计算值选择器根据当前场景的条件,从存储的数据中选择1个数据赋值给当前有效起始位置的状态变量X1

步骤S2.3:第2个m序列状态变量生成器将初始状态变量X2

优选地,所述步骤S2.3采用:第2个m序列状态变量生成器基于当前场景n路专用跳转模块选择1路专用跳转模块激活,初始状态变量X2

优选地,在所述专用跳转模块中,第一路专用跳转模块对输入状态变量X2

优选地,在所述初始跳转模块中,输入数据X2

所述31cycle处理采用:28bit的处理,先配置1个54bit寄存器d,高26bit填0,低28bit填充X2

reg2=d

然后寄存器d左移1位,低位补0。

优选地,在所述初始跳转模块中,定义F为P次运算的状态转换矩阵,且当前状态转换矩阵为31*31维度,X2

优选地,在所述共用跳转模块中,输入数据X2

所述31cycle处理采用:28bit的处理,先配置1个54bit寄存器d,高26bit填0,低28bit填充X2

reg2=d

然后寄存器d左移1位,低位补0;

若当前L=0,则共用跳转模块不工作,初始跳转模块的输出X2

优选地,所述步骤S5采用:根据HW电路的需求,得到相应的状态转换矩阵,将更新后的状态变量X1

根据本发明提供的一种用于5G NR的快速伪随机序列生成系统,包括:

模块M1:识别伪随机序列应用场景的有效起始位置n

模块M2:基于识别的伪随机序列应用场景的有效起始位置n

模块M3:利用预设应用场景有效起始位置的状态变量X1

与现有技术相比,本发明具有如下的有益效果:

1、本发明通过采用初始跳转模块,从而可以节省处理延时和功耗;

2、本发明通过采用共用跳转模块及初始跳转模块采用2部分单独处理的方法和装置,对于HW电路设计,是一种低成本/低复杂度的装置;

3、本发明通过采用n选1的专用跳转模块结构,从而可以节省处理延时和功耗;

4、本发明通过采用初始跳转模块和共用跳转模块,从而可以节省处理延时和功耗,且是一种低成本/低复杂度的装置;

5、本发明通过采用第1个m序列预计算值选择器,从而可以节省处理延时和功耗;

6、本发明通过采用灵活的伪随机比特生成器,对于HW电路设计,可以灵活支持各种场景和硬件速度需求。

附图说明

通过阅读参照以下附图对非限制性实施例所作的详细描述,本发明的其它特征、目的和优点将会变得更明显:

图1为基站同用户设备间的通信示意图。

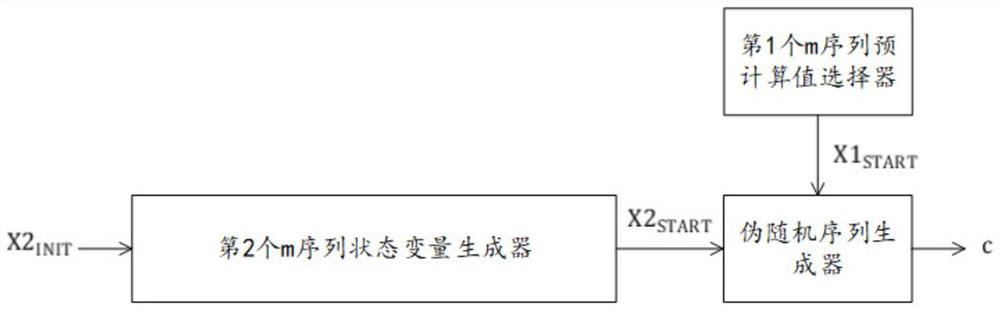

图2为低成本且快速伪随机序列生成装置示意图。

图3为第2个m序列状态变量极高速生成器装置示意图。

图4为第2个m序列状态变量极低成本且高速生成器装置示意图。

图5为初始跳转模块低成本系统示意图。

图6为共用跳转模块低成本装置示意图。

具体实施方式

下面结合具体实施例对本发明进行详细说明。以下实施例将有助于本领域的技术人员进一步理解本发明,但不以任何形式限制本发明。应当指出的是,对本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变化和改进。这些都属于本发明的保护范围。

本发明采用一种低复杂度且低成本的方法和装置,用于快速获取伪随机序列的有效位置的状态变量,在后续调度或处理中实现参考信号或数据的加扰和解扰功能,参见图2。

根据本发明提供的一种用于5G NR的快速伪随机序列生成方法,包括:

步骤S1:识别伪随机序列应用场景的有效起始位置n

对于NR通信系统,伪随机序列应用场景较为复杂,不仅包括WCDMA、LTE、LTE-A通信系统中一个明确的数字(本实施例中,优选为n

具体地,所述PBCH编码数据加扰/解扰过程相关的伪随机比特的有效起始位置为n

所述PDSCH DMRS生成过程相关的伪随机比特的有效起始位置为n

所述预设一般场景的伪随机比特的有效起始位置n

步骤S2:基于识别的伪随机序列应用场景的有效起始位置n

具体地,所述步骤S2采用:

步骤S2.1:获取预设应用场景下第1个m序列有效起始位置n

例如,对于PBCH编码数据加扰/解扰过程场景:

预先通过(1600+864*0)次状态转化后得到状态变量X1

预先通过(1600+864*1)次状态转化后得到状态变量X1

预先通过(1600+864*2)次状态转化后得到状态变量X1

预先通过(1600+864*3)次状态转化后得到状态变量X1

预先通过(1600+864*4)次状态转化后得到状态变量X1

预先通过(1600+864*5)次状态转化后得到状态变量X1

预先通过(1600+864*6)次状态转化后得到状态变量X1

预先通过(1600+864*7)次状态转化后得到状态变量X1

然后将这8个数据存储起来。

对于PDSCH DMRS生成过程场景:

预先通过(1600+0)次状态转化后得到状态变量X1

预先通过(1600+275*8*1)次状态转化后得到状态变量X1

预先通过(1600+275*8*2)次状态转化后得到状态变量X1

预先通过(1600+275*8*3)次状态转化后得到状态变量X1

预先通过(1600+275*8*4)次状态转化后得到状态变量X1

预先通过(1600+275*8*5)次状态转化后得到状态变量X1

预先通过(1600+275*8*6)次状态转化后得到状态变量X1

预先通过(1600+275*8*7)次状态转化后得到状态变量X1

预先通过(1600+275*12*1)次状态转化后得到状态变量X1

预先通过(1600+275*12*2)次状态转化后得到状态变量X1

预先通过(1600+275*12*3)次状态转化后得到状态变量X1

预先通过(1600+275*12*4)次状态转化后得到状态变量X1

预先通过(1600+275*12*5)次状态转化后得到状态变量X1

预先通过(1600+275*12*6)次状态转化后得到状态变量X1

预先通过(1600+275*12*7)次状态转化后得到状态变量X1

预先通过(1600+275*24*1)次状态转化后得到状态变量X1

预先通过(1600+275*24*2)次状态转化后得到状态变量X1

预先通过(1600+275*24*3)次状态转化后得到状态变量X1

预先通过(1600+275*24*4)次状态转化后得到状态变量X1

预先通过(1600+275*24*5)次状态转化后得到状态变量X1

预先通过(1600+275*24*6)次状态转化后得到状态变量X1

预先通过(1600+275*24*7)次状态转化后得到状态变量X1

然后将这22个数据存储起来。

步骤S2.2:第1个m序列预计算值选择器根据当前场景的条件,从存储的数据中选择1个数据赋值给当前有效起始位置的状态变量X1

对于PBCH编码数据加扰/解扰过程场景:选择8个中的某1个数据,即:X1

对于PDSCH DMRS生成过程场景:根据X,ScsIdx两者取值组合做选择,如果X=8,ScsIdx=4,则X1

步骤S2.3:第2个m序列状态变量生成器将初始状态变量X2

其中,第2个m序列状态变量生成器,可以由多个方案实现。图3给出一个极高速生成器方法和装置,而图4给出一个极低成本且高速生成器方法和装置;

图3专用跳转模块1对输入状态变量X2

图4中的初始跳转模块完成P次状态转换,将输入状态变量X2

其中,初始跳转模块可以通过2种方法和装置实现。图5给出一个低成本方法和装置,输入数据分成2部分处理,第一部分简单逻辑处理后存储在reg1,第二部分通过31cycle处理后存储在reg2,最后reg1和reg2做异或处理后得到X2

输入数据X2

a=mod(X2

reg1(0)=0;

reg1(1)=0;

reg1(2)=a;

reg1(3)=X2

reg1(4)=X2

reg1(5)=X2

reg1(6)=a;

reg1(7)=X2

reg1(8)=X2

reg1(9)=X2

reg1(10)=a;

reg1(11)=mod(X2

reg1(12)=mod(X2

reg1(13)=mod(X2

reg1(14)=X2

reg1(15)=0;

reg1(16)=0;

reg1(17)=0;

reg1(18)=a;

reg1(19)=X2

reg1(20)=X2

reg1(21)=X2

reg1(22)=0;

reg1(23)=0;

reg1(24)=0;

reg1(25)=0;

reg1(26)=a;

reg1(27)=X2

reg1(28)=X2

reg1(29)=X2

reg1(30)=a;

此处的reg1可以是HW电路中的寄存器,也可以是SW中的变量。

输入数据X2

reg2=d

然后寄存器d左移1位,低位补0。

举例描述如下,假设

X2

cycle#1:000000000000000000000000000011111000000000000000000000

cycle#2:000000000000000000000000000111110000000000000000000000

cycle#3:000000000000000000000000001111100000000000000000000000

cycle#4:000000000000000000000000011111000000000000000000000000

cycle#5:000000000000000000000000111110000000000000000000000000

cycle#6:000000000000000000000001111100000000000000000000000000

cycle#7:000000000000000000000011111000000000000000000000000000

cycle#8:000000000000000000000111110000000000000000000000000000

cycle#9:000000000000000000001111100000000000000000000000000000

cycle#10:000000000000000000011111000000000000000000000000000000

cycle#11:000000000000000000111110000000000000000000000000000000

cycle#12:000000000000000001111100000000000000000000000000000000

cycle#13:000000000000000011111000000000000000000000000000000000

cycle#14:000000000000000111110000000000000000000000000000000000

cycle#15:000000000000001111100000000000000000000000000000000000

cycle#16:000000000000011111000000000000000000000000000000000000

cycle#17:000000000000111110000000000000000000000000000000000000

cycle#18:000000000001111100000000000000000000000000000000000000

cycle#19:000000000011111000000000000000000000000000000000000000

cycle#20:000000000111110000000000000000000000000000000000000000

cycle#21:000000001111100000000000000000000000000000000000000000

cycle#22:000000011111000000000000000000000000000000000000000000

cycle#23:000000111110000000000000000000000000000000000000000000

cycle#24:000001111100000000000000000000000000000000000000000000

cycle#25:000011111000000000000000000000000000000000000000000000

cycle#26:000111110000000000000000000000000000000000000000000000

cycle#27:001111100000000000000000000000000000000000000000000000

cycle#28:011111000000000000000000000000000000000000000000000000

cycle#29:111110000000000000000000000000000000000000000000000000

cycle#30:111100000000000000000000000000000000000000000000000000

cycle#31:111000000000000000000000000000000000000000000000000000

reg1和reg2做异或处理,输出X2

初始跳转模块另外一种极高速方法和装置描述如下,定义F为P次运算的状态转换矩阵,该矩阵为31*31维度,因此X2

共用跳转模块实现方法和装置同初始跳转模块相似,输入数据X2

图6以PBCH编码数据加扰/解码过程跳转864bit为例,描述该场景共用跳转模块的实现。

输入数据X2

a=mod(X2

reg1(0)=mod(X2

reg1(1)=mod(X2

reg1(2)=mod(X2

reg1(3)=mod(X2

reg1(4)=mod(X2

reg1(5)=X2

reg1(6)=X2

reg1(7)=a;

reg1(8)=mod(X2

reg1(9)=mod(X2

reg1(10)=mod(X2

reg1(11)=X2

reg1(12)=0;

reg1(13)=0;

reg1(14)=0;

reg1(15)=0;

reg1(16)=0;

reg1(17)=a;

reg1(18)=mod(X2

reg1(19)=mod(X2

reg1(20)=mod(X2

reg1(21)=X2

reg1(22)=0;

reg1(23)=a;

reg1(24)=mod(X2

reg1(25)=mod(X2

reg1(26)=mod(X2

reg1(27)=X2

reg1(28)=0;

reg1(29)=0;

reg1(30)=0;

输入数据X2

reg2=d

reg1和reg2做异或处理,输出结果

专用跳转模块1~专用跳转模块8实现从输入状态变量X2

步骤S3:利用预设应用场景有效起始位置的状态变量X1

当获取到X1

伪随机序列生成器的输入参数是X1

假设K=2时,

第一步,用输入的参数X1

y1(0)=X1

y1(1)=X1

y1(2)=X1

y1(3)=X1

y1(4)=X1

y1(5)=X1

y1(6)=X1

y1(7)=X1

y1(8)=X1

y1(9)=X1

y1(10)=X1

y1(11)=X1

y1(12)=X1

y1(13)=X1

y1(14)=X1

y1(15)=X1

y1(16)=X1

y1(17)=X1

y1(18)=X1

y1(19)=X1

y1(20)=X1

y1(21)=X1

y1(22)=X1

y1(23)=X1

y1(24)=X1

y1(25)=X1

y1(26)=X1

y1(27)=X1

y1(28)=X1

y1(29)=mod(X1

y2(29)=mod(X2

y1(30)=mod(X1

y2(30)=mod(X2

第二步,输出伪随机比特s(0)和s(1):

s(0)=mod(y1(29)+y2(29),2),

s(1)=mod(y1(30)+y2(30),2),

第三步,更新X1

X1

X2

本发明提供的用于5G NR的快速伪随机序列生成系统,可以通过本发明提供的用于5G NR的快速伪随机序列生成方法中的步骤流程实现。本领域技术人员,可以将所述用于5G NR的快速伪随机序列生成方法理解为用于5G NR的快速伪随机序列生成系统的一个优选例。

本领域技术人员知道,除了以纯计算机可读程序代码方式实现本发明提供的系统、装置及其各个模块以外,完全可以通过将方法步骤进行逻辑编程来使得本发明提供的系统、装置及其各个模块以逻辑门、开关、专用集成电路、可编程逻辑控制器以及嵌入式微控制器等的形式来实现相同程序。所以,本发明提供的系统、装置及其各个模块可以被认为是一种硬件部件,而对其内包括的用于实现各种程序的模块也可以视为硬件部件内的结构;也可以将用于实现各种功能的模块视为既可以是实现方法的软件程序又可以是硬件部件内的结构。

以上对本发明的具体实施例进行了描述。需要理解的是,本发明并不局限于上述特定实施方式,本领域技术人员可以在权利要求的范围内做出各种变化或修改,这并不影响本发明的实质内容。在不冲突的情况下,本申请的实施例和实施例中的特征可以任意相互组合。

- 用于生成伪随机序列数据的数据序列的生成方法及设备

- 用于生成伪随机序列数据的数据序列的生成方法及设备