闪存器件本征击穿时间的测量方法及系统

文献发布时间:2023-06-19 10:06:57

技术领域

本发明涉及半导体器件及测量技术领域,具体地,涉及一种闪存器件本征击穿时间的测量方法及系统。

背景技术

MONOS(Metal-Oxide-Nitride-Oxide-Silicon),金属-氧化物-氮化物-氧化物-硅结构是组成三维堆垛NAND闪存的基本结构单元。以MONOS结构为基础的3D NAND闪存器件,因为其高密度、低损耗、高性能的特点被广泛应用于半导体存储领域中。随着3D闪存产品越来越普及,提高闪存器件的工作寿命、安全性和可靠性迫在眉睫,分析失效机理成为了改善闪存性能过程中至关重要的一环。作为失效分析过程中一项重要的参考数据,准确测量闪存器件的本征击穿时间在研究失效机理方面具有重大的意义。

目前对MONOS结构的3D NAND闪存器件进行失效分析,主要是依靠人为控制加压条件进行本征击穿,从而获得失效器件。常规的做法是在大量闪存器件上施加持续一定时间的直流电压,然后通过电学性能测试找到发生本征击穿的器件。这种方法存在的问题是为了稳定获得失效器件,浪费大量材料,不经济,同时由于加压时间固定,难以获得准确的本征击穿时间数据。因此,需要寻求新的适合于测量闪存器件本征击穿时间的实用方法。

专利文献CN105161136B一种闪存器件的测试结构及其制造方法,在第一金属互连层制造完成后就可以直接进行字线和控制栅极、字线与位线、位线与位线之间的桥接漏电测试,节约了现有技术中等待第二金属互连层、第三金属互连层的制作时间,同时第一金属互连层与有源区线、字线、控制栅极线之间的连接方式简化了第二金属互连层、第三金属互连层的互连结构。

发明内容

针对现有技术中的缺陷,本发明的目的是提供一种闪存器件本征击穿时间的测量方法及系统。

根据本发明提供的一种闪存器件本征击穿时间的测量方法,包括:

加压方案确定步骤:设置或获取闪存器件本征击穿的加压方案,所述加压方案包括单次加压循环的时间、电压波形以及峰谷数值;

测试方案确定步骤:设置或获取闪存器件漏电情况的测试方案,所述测试方案包括测量电压的大小范围、测量节点个数以及测量节点间隔;

循环测试步骤:重复执行加压方案-测试方案的测试循环,直至本征击穿时停止;

计算步骤:根据本征击穿所需的测试循环次数计算本征击穿的时间。

优选地,所述加压方案确定步骤包括:

采用电学性能分析测试仪器的脚本编写功能设定单次加压循环的时间为50ms;

设定单次加压循环内含有22次方波脉冲,占空比为75%;

设定单次脉冲的最高峰值电压为20V-24V范围内的一定值,最低电压为0V。

优选地,所述测试方案确定步骤包括:

漏电情况的测量电压范围设定为从0V逐渐递增到4.9V;

测量节点间隔设定为0.1V,从0V到4.9V共50个测量节点。

优选地,所述循环测试步骤包括:

获取加压方案和测试方案;

将输出结果设定为每一个节点的电流-电压数据;

定义测试中节点的电流数值大于250nA时发生本征击穿。

优选地,所述计算步骤包括:

根据记录的测试循环次数,本征击穿的时间定义为单次加压时间50ms与测试循环次数的乘积;

调整加压方案中的最高峰值电压,计算不同电压下本征击穿的时间,绘制电压强度-击穿时间曲线图。

根据本发明提供的一种闪存器件本征击穿时间的测量系统,包括:

加压方案确定模块:设置或获取闪存器件本征击穿的加压方案,所述加压方案包括单次加压循环的时间、电压波形以及峰谷数值;

测试方案确定模块:设置或获取闪存器件漏电情况的测试方案,所述测试方案包括测量电压的大小范围、测量节点个数以及测量节点间隔;

循环测试模块:重复执行加压方案-测试方案的测试循环,直至本征击穿时停止;

计算模块:根据本征击穿所需的测试循环次数计算本征击穿的时间。

优选地,所述加压方案确定模块包括:

采用电学性能分析测试仪器的脚本编写功能设定单次加压循环的时间为50ms;

设定单次加压循环内含有22次方波脉冲,占空比为75%;

设定单次脉冲的最高峰值电压为20V-24V范围内的一定值,最低电压为0V。

优选地,所述测试方案确定模块包括:

漏电情况的测量电压范围设定为从0V逐渐递增到4.9V;

测量节点间隔设定为0.1V,从0V到4.9V共50个测量节点。

优选地,所述循环测试模块包括:

获取加压方案和测试方案;

将输出结果设定为每一个节点的电流-电压数据;

定义测试中节点的电流数值大于250nA时发生本征击穿。

优选地,所述计算模块包括:

根据记录的测试循环次数,本征击穿的时间定义为单次加压时间50ms与测试循环次数的乘积;

调整加压方案中的最高峰值电压,计算不同电压下本征击穿的时间,绘制电压强度-击穿时间曲线图。

与现有技术相比,本发明具有如下的有益效果:

1、本发明流程简单,操作容易,经济成本低,可以有效测量闪存器件的本征击穿时间。

2、本发明基于电学性能分析测试仪器的脚本编写功能设定闪存器件本征击穿的加压方案和漏电情况的测试方案,快速建立测量本征击穿时间的方法;

3、采用的脚本编写、执行加压和漏电测试等功能,不需要依赖其他加压和分析测试仪器的帮助,可快速完成闪存器件本征击穿的时间测量过程,避免了闪存器件在不同仪器间施加电压时,因为仪器参数和工作原理的不同而造成的误差;

4、具有准确性高和针对性强的优点,将本方面的测量结果用于失效机理的分析,可以帮助推进改善闪存性能的研究,提高闪存器件的工作寿命、可靠性和安全性。

附图说明

通过阅读参照以下附图对非限制性实施例所作的详细描述,本发明的其它特征、目的和优点将会变得更明显:

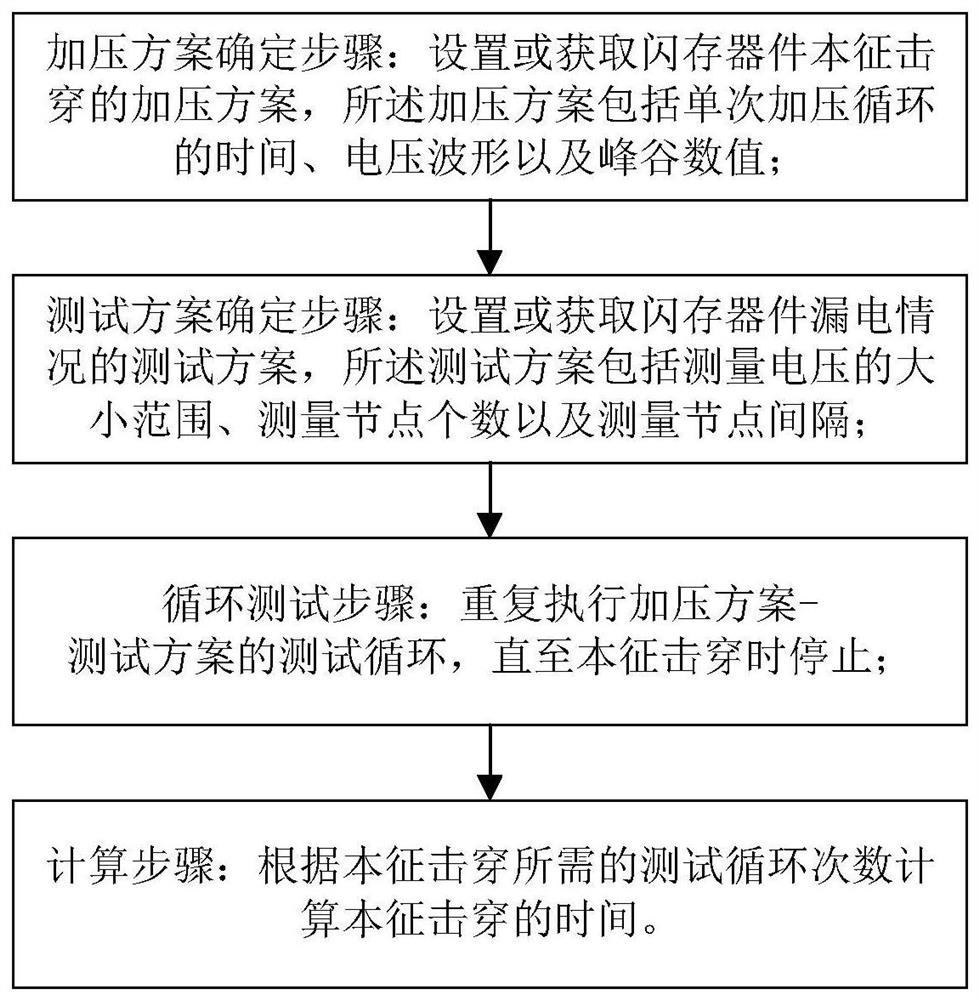

图1为本发明的工作流程图;

图2为闪存器件本征击穿的加压方案示意图;

图3为闪存器件漏电情况的输出结果示意图;

图4为调整加压方案中的最高峰值电压,计算本征击穿时间得到的电压强度-击穿时间曲线图。

具体实施方式

下面结合具体实施例对本发明进行详细说明。以下实施例将有助于本领域的技术人员进一步理解本发明,但不以任何形式限制本发明。应当指出的是,对本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变化和改进。这些都属于本发明的保护范围。

如图1所示,本发明提供的一种闪存器件本征击穿时间的测量方法,包括:

加压方案确定步骤:设置或获取闪存器件本征击穿的加压方案,加压方案包括单次加压循环的时间、电压波形以及峰谷数值;

测试方案确定步骤:设置或获取闪存器件漏电情况的测试方案,测试方案包括测量电压的大小范围、测量节点个数以及测量节点间隔;

循环测试步骤:重复执行加压方案-测试方案的测试循环,直至本征击穿时停止;

计算步骤:根据本征击穿所需的测试循环次数计算本征击穿的时间,通过调整加压数值可以对比时间长短。

实施例一:

A1:设计闪存器件本征击穿的加压方案;

如图2所示,闪存器件本征击穿的加压方案主要包括单次加压循环的时间,电压波形以及峰谷数值。

(1)单次加压循环时间的设定,采用电学性能分析测试仪器Nano_NT的脚本编写功能设定单次加压的时间为50ms。

(2)电压波形的设定,单次加压循环内含有22次方波脉冲,占空比为75%。

(3)峰谷数值的设定,根据测量需要,单次脉冲的最高峰值电压为20V-24V范围内的某一定值,最低电压为0V。

A2:设计闪存器件漏电情况的测试方案;

如图3所示,闪存器件漏电情况的测试方案主要包括电压的大小范围,测试节点个数以及节点间隔。

(1)漏电情况的测量电压范围设定为从0V逐渐递增到4.9V。

(2)测量节点间隔设定为0.1V,从0V到4.9V共50个测量节点。

A3:重复执行加压-测试的循环,检测到本征击穿时停止;

利用电学性能分析测试仪器Nano_NT对闪存器件进行单次加压,然后进行漏电测试,最后输出电流-电压数据。重复这一过程,直到发生本征击穿时停止。

(1)在电学性能分析测试仪器Nano_NT中设定要执行的操作,包括闪存器件的击穿加压方案和漏电测试方案。

(2)输出结果设定为漏电测试每一个节点的电流-电压数据。

(3)本征击穿的定义,漏电测试中4.9V节点的电流数值大于250nA时,定义为发生了本征击穿。

如图4所示,A4:根据击穿需要的加压循环次数,计算本征击穿的时间。

(1)本征击穿时间的计算,根据记录的加压循环次数,击穿时间定义为单次加压时间50ms与加压循环次数的乘积。

(2)调整加压方案中的最高峰值电压,计算不同电压下本征击穿的时间,绘制电压强度-击穿时间曲线图。

在上述一种闪存器件本征击穿时间的测量方法的基础上,本发明还提供一种闪存器件本征击穿时间的测量系统,包括:

加压方案确定模块:设置或获取闪存器件本征击穿的加压方案,所述加压方案包括单次加压循环的时间、电压波形以及峰谷数值;

测试方案确定模块:设置或获取闪存器件漏电情况的测试方案,所述测试方案包括测量电压的大小范围、测量节点个数以及测量节点间隔;

循环测试模块:重复执行加压方案-测试方案的测试循环,直至本征击穿时停止;

计算模块:根据本征击穿所需的测试循环次数计算本征击穿的时间。

本领域技术人员知道,除了以纯计算机可读程序代码方式实现本发明提供的系统及其各个装置、模块、单元以外,完全可以通过将方法步骤进行逻辑编程来使得本发明提供的系统及其各个装置、模块、单元以逻辑门、开关、专用集成电路、可编程逻辑控制器以及嵌入式微控制器等的形式来实现相同功能。所以,本发明提供的系统及其各项装置、模块、单元可以被认为是一种硬件部件,而对其内包括的用于实现各种功能的装置、模块、单元也可以视为硬件部件内的结构;也可以将用于实现各种功能的装置、模块、单元视为既可以是实现方法的软件模块又可以是硬件部件内的结构。

以上对本发明的具体实施例进行了描述。需要理解的是,本发明并不局限于上述特定实施方式,本领域技术人员可以在权利要求的范围内做出各种变化或修改,这并不影响本发明的实质内容。在不冲突的情况下,本申请的实施例和实施例中的特征可以任意相互组合。

- 闪存器件本征击穿时间的测量方法及系统

- 时间分辨激光诱导击穿光谱测量方法