一种邻层环栅纳米线/片CMOS结构

文献发布时间:2023-06-19 10:24:22

技术领域

本发明属于半导体技术领域,具体涉及一种邻层环栅纳米线/片CMOS 结构。

背景技术

随着集成电路特征尺寸突破10nm,短沟道效应和漏致势垒降低效应会 使晶体管性能变得很不稳定。同时,泄漏电流因量子隧穿效应而显著增加, 使整个器件的性能进一步恶化。而且,在该尺寸下晶体管制备过程中工艺 更为复杂,这使摩尔定律的发展举步维艰。

为了抑制短沟道效应,研究者们已经提出了多种新型纳米器件结构, 包括双栅、三栅、π型栅、S型栅、Ω型栅和环栅,这些结构随 MOSFET(Metal-Oxide-SemiconductorField-Effect Transistor,金属-氧化物半 导体场效应晶体管)器件尺寸不断缩小,有望提升传统平面MOSFET的性 能。

在这些新型器件结构中,环栅纳米线场效应晶体管(gate-all-around nanowireFET,GAA NWFET)和环栅纳米片场效应晶体管(gate-all-around nanosheet FET,GAANSFET)可以更好地抑制短沟道效应、漏致势垒降低效 应(Drain Induced BarrierLowering(简称DIBL)Eflect),因而更具发展潜力, 且与当前CMOSFET(ComplementaryMetal Oxide Semiconductor Field Effect Transistor,互补金属氧化物半导体场效应晶体管,简称CMOS)工艺兼容, 将是下一代CMOS有希望的关键结构。

但是,环栅纳米线/片场效应晶体管目前仍然存在制造工艺步骤多、技 术复杂、成本高于常规CMOS等问题。

发明内容

为了解决现有技术中存在的上述问题,本发明提供了一种邻层环栅纳 米线/片CMOS结构。本发明要解决的技术问题通过以下技术方案实现:

一种邻层环栅纳米线/片CMOS结构,包括:衬底;所述衬底上设置有 串行连接的nMOS和pMOS;所述nMOS包括第一纳米体结构和环绕所述 第一纳米体结构的第一栅电极,所述pMOS包括第二纳米体结构和环绕所 述第二纳米体结构的第二栅电极;

所述第一纳米体结构和所述第二纳米体结构设置于相邻的两层;且由 相同导电类型的半导体材料形成;

所述第一栅电极与所述第二栅电极由相同功函数的导电材料形成;

所述衬底材料为体Si或SOI;

所述第一纳米体结构的材料为Si,所述第二纳米体结构的材料为SiGe。

在本发明的一个实施例中,所述第一纳米体结构与所述第二纳米体结 构的材料为掺杂浓度相同的n型半导体材料。

在本发明的一个实施例中,所述第一纳米体结构与所述第二纳米体结 构的材料为掺杂浓度相同的p型半导体材料。

在本发明的一个实施例中,所述第一栅电极和所述第二栅电极的功函 数的范围为4.6~5.1eV。

在本发明的一个实施例中,所述第一栅电极和所述第二栅电极的功函 数的范围为4.1~4.5eV。

在本发明的一个实施例中,所述第一栅电极与所述第二栅电极为同一 导电材料。

在本发明的一个实施例中,所述nMOS的第一源极区、第一漏极区为 n型掺杂,所述pMOS的第二源极区、第二漏极区为p型掺杂。

在本发明的一个实施例中,所述第一纳米体结构包括至少一个第一纳 米体,在所述第一纳米体的数量大于或者等于两个时,所有所述第一纳米 体呈堆叠方式排列,所述第二纳米体结构包括至少一个第二纳米体,在所 述第二纳米体的数量大于或者等于两个时,所有所述第二纳米体呈堆叠方 式排列。

在本发明的一个实施例中,所述第一纳米体结构和所述第二纳米体结 构的导电类型在外延生长叠层结构时形成,或后续过程形成。

在本发明的一个实施例中,所述第一纳米体结构和所述第二纳米体结 构同时一次制备;所述第一栅电极和所述第二栅电极同时一次制备。

本发明的有益效果:

本发明的nMOS和pMOS在相同导电类型和优选相同掺杂浓度的半导体 材料上制备,这样便不需要分别对形成纳米线/片的半导体材料进行掺杂。 同时,由于本发明的nMOS和pMOS的栅电极所采取的材料为相同功函数的 导电材料,优选为同一导电材料,由此不需要分别制备nMOS的栅电极和 pMOS的栅电极,所以本发明的邻层环栅纳米线/片CMOS结构结构减少了制 备环栅CMOS的工艺步骤,缩减了工艺过程,从而降低制备成本和工艺难度, 由此对增强邻层环栅纳米线/片CMOS结构及其集成电路的性能与可靠性大 有益处。

以下将结合附图及实施例对本发明做进一步详细说明。

附图说明

图1是现有技术提供的一种nMOS和pMOS在同一层的环栅纳米线/片 CMOS的结构示意图;

图2是现有技术提供的一种nMOS和pMOS在相邻上下层的环栅纳米线/ 片CMOS的结构示意图;

图3是本发明实施例提供的一种邻层环栅纳米线/片CMOS结构结构的 示意图;

图4是本发明实施例提供的一种邻层环栅纳米线/片CMOS结构的原理 示意图;

图5a~图5j是本发明实施例提供的一种堆叠邻层环栅纳米线/片CMOS 的制备过程示意图;

图6a~图6d是本发明实施例提供的另一种堆叠邻层环栅纳米线/片 CMOS的制备过程示意图。

具体实施方式

下面结合具体实施例对本发明做进一步详细的描述,但本发明的实施 方式不限于此。

为了更好地理解本方案,在介绍本发明所提供的邻层环栅纳米线/片 CMOS结构之前,首先对现有的堆叠环栅纳米线/片CMOS结构进行说明。

环栅,又称围栅(gate-all-around,简称GAA),即栅极金属环绕MOSFET 的沟道区,环栅纳米线与环栅纳米片差别仅在前者环栅围的是线状半导体, 后者环栅围的是片状半导体,纳米线为纳米级线型的半导体材料,纳米片 为纳米级厚度的片型半导体材料。

环栅纳米线/片CMOS由环栅纳米线/片nMOS和环栅纳米线/片pMOS 串接组成,环栅nMOS的纳米线/片是p型半导体,环栅pMOS的纳米线/ 片是n型半导体。环栅纳米线/片CMOS的纳米线/片可以有单层、多层,当 为多层时,即为堆叠环栅纳米线/片CMOS,堆叠环栅纳米线/片CMOS指 堆叠的环栅纳米线/片nMOS和堆叠的环栅纳米线/片pMOS在垂直方向金属 化连接而成的结构。

通常,堆叠环栅纳米线/片CMOS结构的类型有两种,第一种为nMOS 的纳米线/片和pMOS的纳米线/片在同一半导体层上,例如请参见图1,第 二种为nMOS的纳米线/片和pMOS的纳米线/片分别在相邻的上下半导体层 上,例如请参见图2。其中,纳米线为纳米级线型的半导体材料,纳米片为 纳米级厚度的片型半导体材料。

对于环栅纳米线/片CMOS结构而言,其nMOS的纳米线/片由p型半 导体材料制备,pMOS的纳米线/片由n型半导体材料制备。本发明以在形 成鳍式结构之后为例说明纳米线/片由p型半导体材料制备和纳米线/片由n 型半导体材料制备的方法,具体地,在衬底上形成鳍式结构之后进行离子 注入或掺杂等工艺,分别形成制备nMOS的p型鳍和制备pMOS的n型鳍, 也就是说,nMOS的鳍为p型的,因此需要p型掺杂,在制备时需要采用 介质屏蔽pMOS区域,采用相应工艺对nMOS区域的鳍进行p型掺杂,以 制备p型鳍;而pMOS的鳍为n型的,因此需要n型掺杂,在制备时需要 采用介质屏蔽nMOS区域,采用相应工艺对pMOS区域的鳍进行n型掺杂, 以制备n型鳍。其中,鳍是作为形成纳米线/片的材料。

另外,在制备栅电极时,需首先在nMOS的纳米线/片和pMOS的纳米 线/片表面同时淀积栅介质,之后在nMOS的栅介质表面和pMOS的栅介质 表面分别淀积不同功函数的栅金属以分别形成nMOS的栅电极和pMOS的 栅电极。

环栅纳米片与环栅纳米线的差别仅在前者是纳米片状,后者是纳米线 状。因此制备堆叠环栅纳米片CMOS时,其与制备堆叠环栅纳米线CMOS 的区别仅在于纳米片和纳米线形状的不同。

综上,在当前制备技术中,无论是堆叠环栅纳米片CMOS,还是堆叠 环栅纳米线CMOS,都存在下述二方面缺点:

1.环栅nMOS的纳米片/线和环栅pMOS的纳米片/线需要不同导电类型 的半导体材料;

2.环栅纳米片/线nMOS的栅电极和环栅纳米片/线pMOS的栅电极需要 不同功函数的导电材料。

虽然仅是两项技术,但这两项关键技术的实现分别需要独立的步骤、 方法和过程,且工序繁多,工艺复杂,既增加工艺的成本,也会引入工艺 缺陷,影响器件和电路的性能及可靠性,因此,这二项关键技术,对各种 形式的环栅纳米线/片CMOS,包括堆叠环栅纳米线/片CMOS而言,构成 了一致性的缺点。

为了解决上述现有堆叠环栅纳米线/片CMOS存在的缺点,本发明实施 例提供了一种邻层环栅纳米线/片CMOS结构。下面对该结构进行详细说明。

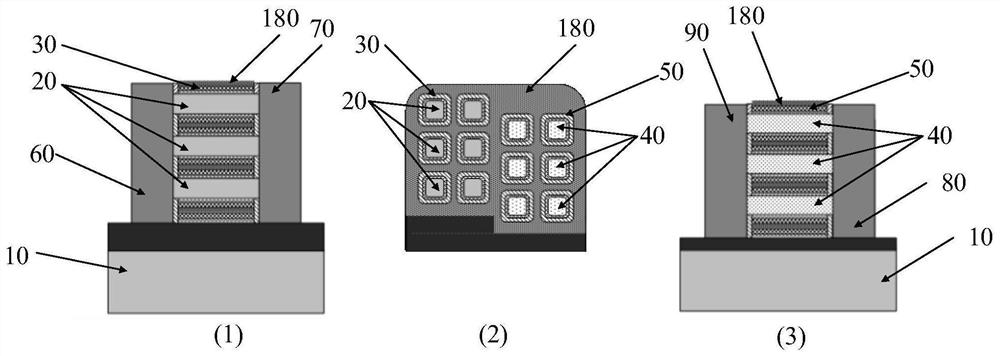

请参见图3,图3是本发明实施例提供的一种邻层环栅纳米线/片CMOS 结构的示意图,其中,图3(1)、图3(3)为侧视图的剖面图,图3(2)为正视图 的剖面图。如图3所示的邻层环栅纳米线/片CMOS结构,包括衬底10;衬 底10上设置有串行连接的nMOS和pMOS;nMOS包括第一纳米体结构20 和环绕第一纳米体结构20的第一栅电极30,pMOS包括第二纳米体结构40和环绕第二纳米体结构40的第二栅电极50;第一纳米体结构20和第二 纳米体结构40设置于相邻的两层,且由相同导电类型的半导体材料形成; 第一栅电极30与第二栅电极50由相同功函数的导电材料形成;衬底10的 材料为体Si或SOI;第一纳米体结构20的材料为Si,第二纳米体结构40 的材料为SiGe。

本发明实施例选择衬底10的材料为体Si或SOI,区别仅在于形成鳍结 构时刻蚀的浅沟槽的深度不同,最终制备的邻层环栅纳米线/片CMOS结构 是相同的。

第一纳米体结构20和第二纳米体结构40的材料可以为Si、SiGe、Ge、 SiC、Ⅲ-Ⅳ族等半导体材料,只要能满足第一纳米体结构20的材料和第二 纳米体结构40的材料之间能构成叠层结构时可以互为牺牲层材料即可。而 本发明实施例中第一纳米体结构20的材料选择Si,第二纳米体结构40的 材料选择SiGe,是最佳组合,可以同时满足nMOS和pMOS高性能的要求。

需要说明的是,第一纳米体结构20和第二纳米体结构40的厚度和掺 杂浓度应满足在栅电极功函数作用下完全耗尽的要求。

在一个实施例中,第一纳米体结构20与第二纳米体结构40的材料为 掺杂浓度相同的n型半导体材料,nMOS的第一源极区60、第一漏极区70 为n型掺杂,pMOS的第二源极区80、第二漏极区90为p型掺杂。

进一步地,若第一纳米体结构20和第二纳米体结构40的材料为掺杂浓 度相同的n型半导体材料,那么,第一栅电极30和第二栅电极50采用功函数 在该n型半导体材料价带顶附近的同一导电材料,且所选取的第一栅电极30 和第二栅电极50功函数要使纳米体结构完全耗尽,优选地第一栅电极30和 第二栅电极50的功函数的范围为4.6~5.1eV,具体取值以纳米体结构的厚度 和掺杂浓度等参数而定,此处不做任何限定。此外,为了缩减工艺步骤, 提高邻层环栅纳米线/片CMOS结构电路的性能及可靠性,第一栅电极与第 二栅电极优选采用同一导电材料,导电材料选用现有邻层环栅纳米线/片 CMOS结构常见的栅电极材料即可,在此不作限制。

在另一个实施例中,第一纳米体结构20与第二纳米体结构40的材料 为掺杂浓度相同的p型半导体材料,nMOS的第一源极区60、第一漏极区 70为n型掺杂,pMOS的第二源极区80、第二漏极区90为p型掺杂。

进一步地,若第一纳米体结构20与第二纳米体结构40都在掺杂浓度相 同的p型半导体材料上制备,那么,第一栅电极30和第二栅电极50采用功函 数在该p型半导体材料导带底附近的同一导电材料,且所选取的第一栅电极 30和第二栅电极50功函数要使纳米体结构完全耗尽,优选地第一栅电极30 和第二栅电极50的功函数范围的范围为4.1~4.5eV,具体取值以纳米体结构 的厚度和掺杂浓度等参数而定,此处不做任何限定。同样地,为了缩减工 艺步骤,提高邻层环栅纳米线/片CMOS结构电路的性能及可靠性,第一栅 电极与第二栅电极优选采用同一导电材料,导电材料选用现有邻层环栅纳 米线/片CMOS结构常见的栅电极材料即可,在此不作限制。

在本发明的实施例中,第一纳米体结构20包括至少一个第一纳米体, 在第一纳米体的数量大于或者等于两个时,所有第一纳米体呈堆叠方式排 列,第二纳米体结构40包括至少一个第二纳米体,在第二纳米体的数量大 于或者等于两个时,所有第二纳米体呈堆叠方式排列。

由于本发明实施例的邻层环栅纳米线/片CMOS结构中,第一纳米体结 构20和第二纳米体结构40是由相同导电类型的半导体材料形成,且第一 栅电极30与第二栅电极50由相同功函数的导电材料形成,因此,本发明 实施例的nMOS和pMOS可以在同一衬底上同时制备,也即,第一纳米体 结构20和第二纳米体结构40同时一次制备,第一栅电极30和第二栅电极50同时一次制备。也因此,第一纳米体结构和第二纳米体结构的导电类型 可以在外延生长叠层结构时形成,也可以在后续过程形成。

请参见图4,图4是本发明实施例提供的一种邻层环栅纳米线/片CMOS 结构的原理示意图。通过本发明实施例所提供的邻层环栅纳米线/片CMOS 结构和图5可知,当电源施加正电压V

本发明实施例的nMOS的第一纳米体结构和pMOS的第二纳米体结构在 相同导电类型的半导体材料上制备,且为相同或相近掺杂浓度,优选相同 的掺杂浓度,即nMOS的第一纳米体结构和pMOS的第二纳米体结构在一定 掺杂浓度的p型半导体材料上制备,或在一定掺杂浓度的n型半导体材料上 制备,这样便不需要分别对环栅nMOS的纳米片/线和环栅pMOS的纳米片/ 线分别制备不同导电类型的半导体材料,从而本发明实施例的邻层环栅纳米线/片CMOS结构可以省去分别制备不同导电类型的半导体材料的工艺过 程,虽然表面上看省去的是制作n型半导体材料或者p型半导体材料的关键 工艺,但却可减少多次工序步骤,这对缩短工艺周期,控制工艺误差,降 低芯片工艺成本,提升器件和电路的性能及可靠性等是极为有益和有利的, 而该问题恰是业界所重视和长期关注的核心问题之一。同时,又由于本发 明实施例的nMOS和pMOS的栅电极所采取的材料为相同功函数的导电材料, 或者优选为同一导电材料,当采用同一导电材料作为栅电极时,则不需要 分开制备nMOS的栅电极和pMOS的栅电极,据此,虽然是缩减了制备栅电 极的关键工艺,但同样可减少多次工艺步骤,缩短工艺周期,控制工艺误 差,降低芯片工艺成本。另外,本发明实施例的邻层环栅纳米线/片CMOS结 构的栅电极区域是其敏感区域,栅电极控制CMOS的性能,且栅电极制备的 工艺过程会影响CMOS的性能,因此,nMOS的栅电极和pMOS的栅电极采 用功函数相同的同一种导电材料,且只需制备一次,有利于提升邻层环栅 纳米线/片CMOS结构电路的性能及可靠性。

综上,本发明实施例通过上述方式简化了邻层环栅纳米线/片CMOS结构 的两项关键工艺技术,减少了制备邻层环栅纳米线/片CMOS结构的工艺步骤, 缩减了工艺过程、工艺难度,从而可以降低制备成本,由此还可以提升邻 层环栅纳米线/片CMOS结构及其集成电路的成品率、性能与可靠性。另外, 本发明实施例所提供的邻层环栅纳米线/片CMOS结构还可增加阈值电压调 控维度,即提升开关速度。

下面对本发明实施例的邻层环栅纳米线/片CMOS结构的制备方法进行 说明。

请参见图5a~图5j,图5a~图5j是本发明实施例提供的一种堆叠邻层 环栅纳米线/片CMOS的制备过程示意图,本发明实施例基于上述内容,还 提供一种堆叠邻层环栅纳米线/片CMOS的制备方法,该制备方法是nMOS 的纳米线/片(第二材料层)为Si、pMOS的纳米线/片(第一材料层)为SiGe为 例进行说明,该制备方法包括:

步骤1、请参见图5a,提供半导体衬底10。

具体地,半导体衬底10是SOI。

步骤2、外延生长叠层材料。

叠层材料将是堆叠环栅CMOS的纳米线/片,叠层材料的导电类型可以 是n型,也可以是p型,按设计要求,本发明实施例的nMOS和pMOS共 用同一种导电类型的半导体材料。

具体地,请参见图5b,在半导体衬底10表层交替生长SiGe层101和 Si层102。

进一步地,SiGe层101和Si层102相互间具备可以选择性刻蚀的属性。 本发明实施例中,外延的首层材料为SiGe,之后Si/SiGe交替生长。本发明 实施例的叠层厚度和层数按设计要求,本发明实施例对此不做具体限定。

本发明实施例叠层材料的导电类型可以在叠层外延生长时原位掺杂实 现,也可在后续过程通过离子注入、扩散等工艺完成。

步骤3、形成鳍结构。

请参见图5c,其中,图5c(1)为正视图,图5c(2)为侧视图,同时刻蚀 SiGe层101和Si层102,以刻蚀出第一材料叠层100和第二材料叠层110, 第一材料叠层100和第二材料叠层110即为鳍结构,在刻蚀SiGe层101和 Si层102时,可以刻蚀到SOI的SiO

步骤4、请参见图5d,其中,图5d(1)、图5d(3)为侧视图,图5d(2)为 剖面图,在nMOS区域的鳍结构之间淀积介质,形成介质层120,在nMOS 区域的鳍间淀积的介质的表面与第一层SiGe的下表面对齐,pMOS区域的 鳍间不淀积的介质。

步骤5、形成赝栅介质、赝栅电极。

具体地,请参见图5e,其中,图5e(1)和图5e(2)为侧视图,首先在第 一材料叠层100和第二材料叠层110上制备赝栅介质,之后在赝栅介质上 制备赝栅电极140,膺栅介质与赝栅电极140重合,制备赝栅电极140的作 用是为了后续制备源、漏电极,及确定沟道长度。

步骤6、请继续参见图5e,其中,图5e(1)、10e(2)为侧视图,在赝栅 电极140的侧面形成隔离层150,隔离层150的作用是为了避免下述制备的 器件的栅电极与其源、漏电极形成短路。

步骤7、请参见图5f,其中,图5f(1)和图5f(3)为侧视图,图5f(2)为 图5f(1)对应的剖面图、图5f(4)为图5f(3)对应的剖面图,刻蚀掉赝栅电极 140及其侧面的隔离层150之外的鳍,在nMOS区域,采用异性刻蚀方法, 刻蚀掉隔离层所遮挡的SiGe部分,在pMOS区域,采用异性刻蚀方法,刻 蚀掉隔离层所遮挡的Si部分,在刻蚀掉的牺牲层处形成内隔离层160。

步骤8、请参见图5g,分别在所划分的nMOS和pMOS的隔离层二侧, 对nMOS外延n型半导体材料,形成nMOS的第一源极区60和第一漏极区 70,对pMOS外延p型半导体材料,形成pMOS的第二源极区80和第二漏 极区90。

步骤9、请参见图5h,其中,图5h(1)和图5h(2)为侧视图,刻蚀掉赝栅 电极140及其下面的膺栅介质,且保留赝栅电极140侧面的隔离层150,裸 漏出膺栅介质130下表面的鳍,利用Si和SiGe各向异性的腐蚀特性,刻蚀 掉nMOS区域的SiGe层,留下Si层作为nMOS的纳米线/片,刻蚀掉pMOS 区域的Si层,留下SiGe层作为pMOS的纳米线/片,被留下的Si层作为nMOS的第一纳米体结构20、被留下的SiGe层作为pMOS的第二纳米体结 构40。

步骤10、淀积栅介质层和制备栅电极。

具体地,请参见图5i,其中,图5h(1)和图5h(2)为侧视图的剖面图,首 先在被释放的裸漏的nMOS的Si纳米线/片和pMOS的SiGe纳米线/片周围 共同淀积栅介质层170;之后,在nMOS的Si纳米线/片和pMOS的SiGe 纳米线/片周围的栅介质层170之上,共同淀积同一功函数的栅金属,形成 第一栅电极30和第二栅电极50。

需要说明的是,本发明实施例的栅电极的功函数的具体数值需基于电 学特性要求,由纳米线/片的厚度、掺杂浓度等优化决定,且其要保障在零 偏下纳米线/片全耗尽。

步骤11、金属化。

具体地,请参见图5j,其中,图5j(1)、图5j(3)为侧视图的剖面图,图5j(2)为正视图的剖面图,最后通过金属化金属180实现金属化连接,金属化的目的是将堆叠环栅纳米线/片nMOS的第一栅电极30与pMOS的第二栅电极50连接在一起,以及将nMOS的第一漏极区70与pMOS的第二漏极区90连在一起,形成堆叠邻层环栅纳米线/片CMOS结构。

需要说明的是,本发明实施例的纳米线/片可以为n型,也可以为p型, 叠层纳米线/片的导电类型,可以在外延生长叠层材料时原位掺杂形成,也 可以在后续裸露用于形成纳米线/片的材料的过程形成,例如离子注入、扩 散等工艺。

另外,当本发明实施例的半导体衬底10为体Si时,其与半导体衬底 10为体SOI的区别仅在步骤1-步骤4,其余步骤均与半导体衬底10为SOI 的相同,因此本发明实施例对于半导体衬底10为体Si的堆叠邻层环栅纳米 线/片CMOS仅介绍步骤1-步骤4,请参见图6a~图6d,当本发明实施例的 半导体衬底10为体Si时,制备方法包括:

步骤1、请参见图6a,提供半导体衬底10。

具体地,半导体衬底10是体Si。

步骤2、外延生长叠层材料。

具体地,请参见图6b,在半导体衬底10表层交替生长SiGe层101和 Si层102。

进一步地,SiGe层101和Si层102相互间具备可以选择性刻蚀的属性。 本发明实施例中,外延的首层材料为SiGe,之后Si/SiGe交替生长。本发明 实施例的叠层厚度和层数按设计要求,本发明实施例对此不做具体限定。

本发明实施例叠层材料的导电类型可以在叠层外延生长时原位掺杂实 现,也可在后续过程通过离子注入、扩散等工艺完成。

步骤3、形成鳍结构。

请参见图6c,同时刻蚀SiGe层101和Si层102,以刻蚀出第一材料叠 层100和第二材料叠层110,第一材料叠层100和第二材料叠层110即为鳍 结构,在刻蚀SiGe层101和Si层102时,可以刻蚀到体Si的表面,也可 刻蚀到体Si的界面之下,其中,第一材料叠层100用于形成nMOS的纳米 线/片,第二材料叠层110用于形成pMOS的纳米线/片,纳米线/片的几何尺寸按设计要求制备。

步骤4、请参见图6d,其中,图6d(1)、图6d(3)为侧视图的剖面图,图 6d(2)为正视图的剖面图,在nMOS区域的鳍结构之间和pMOS区域的鳍结 构之间淀积介质,形成介质层120,在nMOS区域的鳍间淀积的介质的表 面与SiGe的下表面对齐,在pMOS区域的鳍间淀积的介质的表面与Si的 下表面对齐。

对于半导体衬底10为体Si,在体Si上形成介质层120之后的步骤与 本发明实施例的半导体衬底10为SOI的制备步骤相同,在此不再赘述。

以上内容是结合具体的优选实施方式对本发明所作的进一步详细说明, 不能认定本发明的具体实施只局限于这些说明。对于本发明所属技术领域 的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干简 单推演或替换,都应当视为属于本发明的保护范围。

- 一种邻层环栅纳米线/片CMOS结构

- 一种同层环栅纳米线/片CMOS结构