一种隧穿电流触发的SCR器件

文献发布时间:2023-06-19 11:17:41

技术领域

本发明属于集成电路静电放电防护技术领域,涉及一种隧穿电流触发的SCR器件。

背景技术

静电放电(ESD)是自然界普遍存在的一种现象,集成电路中的栅氧化层和pn结都很容易被ESD电流击穿,因此,集成电路都必须带有ESD保护电路。随着集成电路工艺的不断进步,器件的尺寸不断缩小,器件天然的抗ESD损伤的能力越来越低,这给ESD电路设计带来了更多的挑战。

晶闸管(简称SCR)可用于ESD保护,SCR中的两个寄生的NPN与PNP双极晶体管交叉耦合,构成一个正反馈结构,当外界作用使得该正反馈结构导通时,便可高效泄放ESD电流,因此,SCR具有高鲁棒性。但是,传统SCR器件需要首先发生雪崩击穿,再通过雪崩击穿产生的电流来建立正反馈导通机制,导致其触发电压太高,即SCR两端电压首先需要上升到较高水平才能使得SCR开启放电。高的触发电压意味着ESD放电的初始阶段,被保护器件的端电压很高,然后随着SCR的导通,该端电压才会逐渐下降,因此,被保护器件的失效概率更大。通常,可以通过增加辅助触发电路来降低触发电压,常用的是二极管触发的SCR结构(Diodetriggered SCR,简称DTSCR),如图1所示。然而,这种DTSCR需要额外引入若干个二极管,具体的二极管数目由电路的工作电压决定,对于1V工作电压的电路,一般额外引入2个或者3个二极管。从图1可以看到,即使只引入2个二极管,其带来的版图面积也增加了约1倍。

目前,一些新型结构和材料被引入到先进集成电路工艺中,这也为进一步提升SCR的性能提供了更多可能的方法。

发明内容

本发明的目的是提供一种隧穿电流触发的SCR器件,解决了现有技术中DTSCR中由于额外引入了二极管,导致版图面积增加较多的问题。

本发明所采用的技术方案是,一种隧穿电流触发的SCR器件,包括P衬底,在P衬底上表面依序分别设置有第一P+注入区、第一沟槽和第一N+注入区、栅氧化层、第二N+注入区、第二沟槽和第二P+注入区;栅氧化层内部包裹有栅电极;在第一P+注入区、第一沟槽和第一N+注入区的一部分三者下方共同设置有N阱;第一N+注入区和栅氧化层之间通过P衬底间隔设置;第一P+注入区与电学阳极连接,栅电极、第二N+注入区第二P+注入区均与电学阴极连接。

本发明的隧穿电流触发的SCR器件,其特征还在于:

所述的第一沟槽和第二沟槽均为浅沟槽。

所述的第一N+注入区采用Ge材料。

所述的N阱、P衬底均采用Si材料。

所述的第一P+注入区、第一N+注入区、第二N+注入区、第二P+注入区均采用Si材料。

本发明的有益效果是,使得SCR器件具有更小的面积。

附图说明

图1是现有技术的DTSCR的剖面图;

图2是点隧穿的P型隧道晶体管的剖面图;

图3是线隧穿的U形栅的P型隧道晶体管的剖面图;

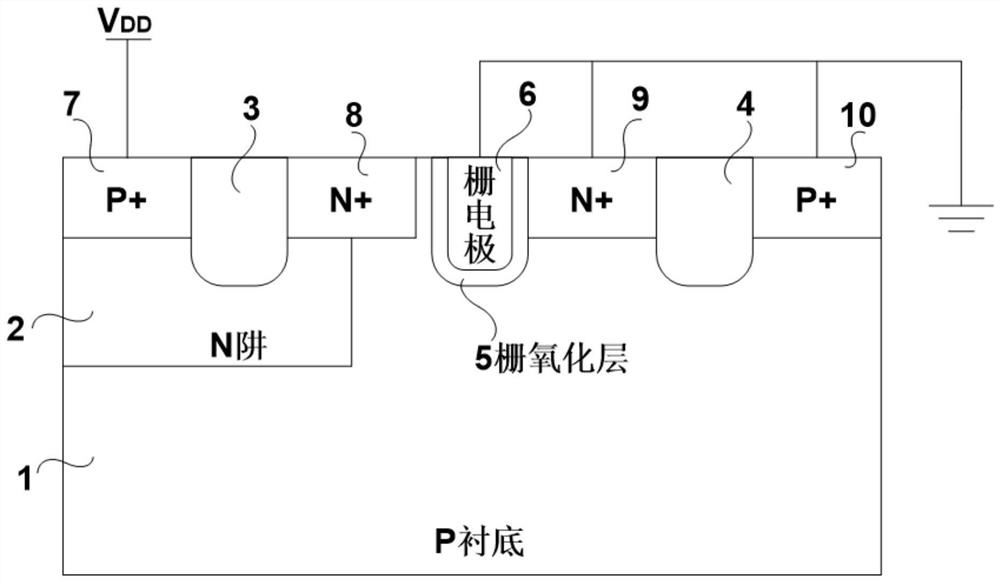

图4是本发明器件结构的剖面图;

图5是本发明器件结构在ESD放电的初始时刻电流路径的示意图;

图6是本发明器件结构与现有技术DTSCR在传输线脉冲测试条件下的电压仿真对比图。

图中,1.P衬底,2.N阱,3.第一沟槽,4.第二沟槽,5.栅氧化层,6.栅电极,7.第一P+注入区,8.第一N+注入区,9.第二N+注入区,10.第二P+注入区。

具体实施方式

下面结合附图和具体实施方式对本发明进行详细说明。

参照图1,是现有技术DTSCR的剖面图,以含有3个二极管的结构为例,其中二极管D01和二极管D02为常规P+/N阱二极管,二极管D03由晶闸管SCR0的阳极区构成,这3个二极管之间是串联关系,构成一个二极管串。晶闸管SCR0阳极的P+区(相当于发射极)、晶闸管SCR0的N阱(相当于基极)和P衬底(相当于集电极)构成一个寄生PNP双极晶体管。当ESD事件发生时,VDD上的电压升高,当VDD超过3个二极管的阈值电压之和时,3个二极管都导通。那么二极管D03导通,相当于寄生PNP双极晶体管的基射结正偏,那么该PNP双极晶体管导通。该PNP晶体管的导通又促使晶闸管SCR0中寄生的NPN双极晶体管导通乃至正反馈机制建立,从而泄放ESD电流。

参照图2,是现有技术点隧穿的P型隧道晶体管的剖面图,当源极接高电位、栅极和漏极接低电位时,该隧道晶体管内会产生从源极到漏极的电流,即晶体管导通。相关原理如下:由于栅极接低电位,通过电场调制效应,会在栅氧化层下几个纳米范围内方积累空穴,形成一个高浓度P型半导体薄层,即P+沟道区;该P+沟道区和N+源极区的界面形成了一个高掺杂浓度的pn结;由于源极接高电位,该高掺杂浓度的pn结处于反偏状态,N+源极区的能带足够低,P+沟道区的能带足够高,因此发生带带隧穿效应、产生隧穿电流;又源极电位高于漏极接低电位,在电场作用下,隧穿电流会从源极流向漏极,即隧道晶体管导通。

参照图3,是现有技术线隧穿的U形栅P型隧道晶体管的剖面图,N+源极区的右边界和栅氧化层的左边界有较大的重叠区,重叠区的范围就是N+源极区的厚度。该重叠区内都可以发生隧穿,因此,可以通过增加N+源极区的厚度来增大隧穿电流。采用U形栅的目的是把隧穿区域分布在竖直方向,减小了占用的水平方向的版图面积,这种是一种常见方法,参见文献1和文献2。还可以通过采用隧穿率高的材料来提高隧穿电流,比如在N+源极区使用Ge材料。

上述的图2结构是基本型隧道晶体管,图3结构是对图2的改进,而本发明主要是基于对图3结构的进一步改进。

参照图4,本发明隧穿电流触发的SCR器件的结构是,包括P衬底1,在P衬底1上表面依序分别设置有第一P+注入区7、第一沟槽3和第一N+注入区8、栅氧化层5、第二N+注入区9、第二沟槽4和第二P+注入区10;栅氧化层5内部包裹有栅电极6;在第一P+注入区7、第一沟槽3和第一N+注入区8的一部分三者下方共同设置有N阱2;第一N+注入区8和栅氧化层5之间通过P衬底1间隔设置;第一P+注入区7与电学阳极连接,栅电极6、第二N+注入区9、第二P+注入区10共同与电学阴极连接。

第一沟槽3和第二沟槽4的材料是二氧化硅(此处不需要强调尺寸范围,“浅沟槽”是一种通常叫法而已),用于实现不同导电类型区域之间的隔离,第一沟槽3实现第一P+注入区7与第一N+注入区8的隔离,第二沟槽4实现第二N+注入区9与第二P+注入区10的隔离;栅氧化层5是实现电场调制效应的介质;为了增大隧穿电流,第一N+注入区8采用Ge材料,N阱2、P衬底1和其他注入区均采用Si材料。

由图4可见,第二P+注入区10与P衬底1相连,实现P衬底1电位接地的效果;第一P+注入区7、N阱2、P衬底1构成一个PNP型双极晶体管;N阱2、P衬底1和第二N+注入区9构成一个NPN型双极晶体管;PNP型双极晶体管和NPN型双极晶体管交叉耦合构成正反馈结构。另外,第一N+注入区8、栅氧化层5、栅电极6、P衬底1和第二P+注入区10构成一个线隧穿的U形栅P型隧道晶体管,其中第一N+注入区8是源极,P衬底1是沟道,第二P+注入区10是漏极。

参照图5,本发明器件结构的工作原理是,当ESD电流从VDD进入器件时,初始时刻,ESD电流首先进入第一P+注入区7,再流过由第一P+注入区7和N阱2构成的pn结到达N阱2,再从N阱2流入第一N+注入区8;随后在第一N+注入区8和栅氧化层5之间通过隧穿效应流入P衬底1,并最终通过P衬底1的寄生电阻或者P衬底1和第二N+注入区9形成的pn结流向电学阴极(接地);随后,随着流入器件的电流继续增大,第一P+注入区7和N阱2构成的pn结正偏更加强烈,第一P+注入区7、N阱2和P衬底1组成的寄生PNP晶体管导通,进而引起N阱2、P衬底1和第二N+注入区9组成的寄生NPN晶体管导通,实现正反馈导通并大量泄放ESD电流。

仿真验证:

以电源电流10ns内上升到0.01A/μm并持续100ns的条件来仿真本发明器件在传输线脉冲测试下的状态,仿真结果为电压。仿真结果如图6所示,对比仿真了额外带有2个二极管的DTSCR和本发明器件在传输线脉冲测试条件下的电压箝位效果,其电压峰值分别为3.2V和2.6V,说明本发明器件可以及时开启SCR,本发明器件的箝位效果略好于对比器件。

综上所述,本发明的器件在传统SCR器件中嵌入了隧穿晶体管,在ESD放电初始时刻通过电场调制的隧穿效应实现了SCR器件N阱区到P衬底区之间的电流导通,进而通过该隧穿电流促进正反馈导通的快速建立。本发明器件的版图面积比DTSCR的小,这从图1和图4也可以反映出来,已有技术的DTSCR使用了7个沟槽和8个注入区,而本发明器件使用了2个沟槽和4个注入区,版图面积明显减小。隧道晶体管的栅极设置为U形,也避免了占用更多版图面积。本发明优选地在第一N+注入区采用了具有高的隧穿率Ge材料,隧道晶体管采用线隧穿晶体管,都增加了隧穿电流,对SCR正反馈导通更为有利。事实上,可以选用材料和结构形状有很多种,只要是在SCR器件中嵌入隧道晶体管,通过电场调制的隧穿效应实现SCR器件N阱区到P衬底区之间的电流导通,都可以产生隧穿电流促进正反馈导通的建立,区别在于隧穿电流是否足够大、这种促进作用是否明显,以及制造工艺的可行性和复杂度。

参考文献:

[1]S.W.Kim,J.H.Kim,T.-J.K.Liu,W.Y.Choi,and B.G.Park.“Demonstration ofL-shaped tunnel field-effect transistors,”IEEE Trans.Electron Devices,vol.63,no.4,pp.1774-1778,Mar.2016.DOI:

[2]W.Wang,P.F.Wang,C.M.Zhang,X.Lin,X.Y.Liu,Q.Q.Sun,P.Zhou,andD.W.Zhang.“Design of U-shape channel tunnel FETs with SiGe source regions,”IEEE Trans.Electron Devices,vol.61,no.1,pp.193–197,Jan.2014.DOI:

- 一种隧穿电流触发的SCR器件

- 具有高触发电流的SCR器件及静电放电电路结构