半导体结构及封装方法

文献发布时间:2023-06-19 11:54:11

技术领域

本申请涉及半导体技术领域,尤其涉及一种半导体结构及封装方法。

背景技术

近年来,随着计算机行业的迅速发展,高性能计算(High PerformanceComputing,HPC)的应用越来泛应用,例如在高性能网路和服务器应用等领域,特别是人工智能(Artificial Intelligence,AI)相关的产品。HPC类应用需要满足高数据传输速率、大带宽和低延迟等性能要求,为了满足上述要求,在芯片内集成高带宽存储器(HighBandwidth Memory,HBM)和处理器成为一个可行的解决方案,因其通过较短的连线相连,会减少延迟、降低功耗;而晶圆级芯片封装(Chip on Wafer on Substrate,CoWoS)提供了一种可行的封装方式。

CoWoS属于一种集成型先进半导体封装技术,可实现将具有高运算能力的逻辑芯片与具有大容量和频宽的存储器芯片整合在一起。作为一种2.5D/3D封装工艺,CoWoS可以让芯片尺寸更小,同时拥有更高的输入/输出(Input/Output,I/O)带宽。具体地,CoWoS是晶圆段延伸的先进封装技术,其先将半导体芯片通过晶圆级芯片(Chip on Wafer,CoW)封装连接至矽晶圆,再把CoW芯片与基板连结,集成得到CoWoS。

现有技术中,CoWoS封装技术,通常将多个高带宽存储器和处理器并排放置在中介层上,此种封装方式会到导致封装尺寸过大,另一方面增加中介层的使用,导致封装成本增加。

发明内容

本申请实施例提供一种半导体结构及封装方法,以解决现有技术中,CoWoS封装技术导致封装尺寸过大以及成本增加的问题。

一方面,本申请实施例提供了一种半导体结构,所述半导体结构包括:

第一半导体衬底130;

第一重布线层210,设置于所述第一半导体衬底130之上,

第一模塑组合物层400,设置于所述第一重布线层210之上;其中,所述第一模塑组合物层400的第一结构面403设置有凹槽401;

存储器502,至少部分设置于所述凹槽401中;

第二重布线层220,设置于所述第一结构面403上所述凹槽401以外的区域;

处理器501,设置于所述第二重布线层220之上,并与所述存储器502至少部分重叠设置;所述处理器501分别与所述存储器502、所述第一重布线层210的第一焊盘218电连接。

可选地,所述半导体装置还包括:

第二模塑组合物层500,覆盖所述第二重布线层220以及所述处理器501、所述存储器502;

电源基板504,与所述存储器502的接触面连接。

可选地,所述第一模塑组合物层400设置有贯穿于所述第一模塑组合物层400的金属穿孔302;所述金属穿孔302内填充有金属;

所述金属穿孔302的第一端裸露于所述第一模塑组合物层400的第一结构面403;

所述金属穿孔302的第二端与所述第一焊盘218电连接。

可选地,所述处理器501依次通过所述第二重布线层220的第二焊盘217、所述金属穿孔302与所述第一焊盘218电连接。

可选地,所述第一重布线层210包括第一绝缘层212,所述第一焊盘218贯穿于所述第一绝缘层212。

另一方面,本申请实施例还提供一种半导体封装方法,所述方法包括:

提供一第二半导体衬底;

在所述第二半导体衬底之上覆盖一保护层;

在所述保护层之上设置覆盖一层第一重布线层;

在所述第一重布线层之上覆盖模塑组合物,形成第一模塑组合物层;

在所述第一模塑组合物层的第一结构面上形成凹槽;

在所述第一结构面上所述凹槽以外的区域覆盖第二重布线层;

在所述凹槽中放置存储器;

在所述第二重布线层之上放置处理器;其中,所述处理器分别与所述存储器、所述第一重布线层的第一焊盘电连接;

移除所述保护层以及所述第二半导体衬底,将所述第一重布线层与第一半导体衬底连接,形成半导体结构。

可选地,所述在所述保护层之上设置覆盖一层第一重布线层之后,所述方法包括:

在所述第一重布线层之上覆盖一层模版层;

对所述模版层进行光刻处理,形成贯穿于所述模版层的穿孔;

在所述穿孔填充金属,形成金属穿孔,移除模版层;

其中,所述金属穿孔贯穿于所述第一模塑组合物层。

可选地,所述移除所述保护层以及所述第二半导体衬底之前,所述方法还包括:

通过所述存储器的接触面以及所述第二重布线层的第二焊盘,与电源基板连接;

通过模塑组合物覆盖所述第二重布线层以及所述处理器、所述存储器,形成第二模塑组合物层。

又一方面,本申请实施例还提供一种电子设备,该电子设备包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,所述处理器执行所述计算机程序时实现如上所述的半导体封装方法中的步骤。

再一方面,本申请实施例还提供一种计算机可读存储介质,该计算机可读存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现如上所述的半导体封装方法中的步骤。

在本申请实施例中,在所述半导体结构中,存储器502通过设置在作为中介层的第一模塑组合物层400的凹槽401内,降低了所述半导体结构的整体封装高度;处理器501与存储器502至少部分重叠设置,减少了第一模塑组合物层400的使用面积,节省第一模塑组合物层400的使用成本。

附图说明

为了更清楚地说明本申请实施例的技术方案,下面将对本申请实施例的描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

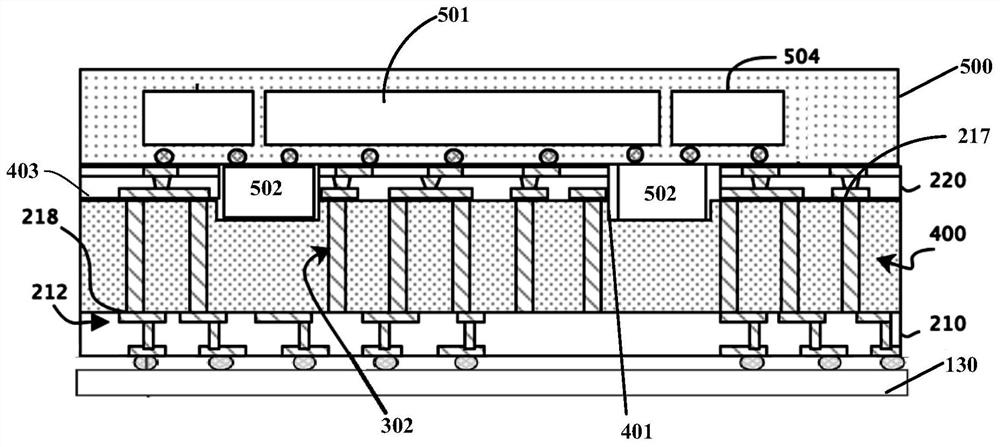

图1为本申请实施例提供的半导体封装结构的示意图;

图2为本申请实施例提供的半导体封装方法的步骤流程图;

图3为本申请实施例提供的半导体封装方法的示意图之一;

图4为本申请实施例提供的半导体封装方法的示意图之二;

图5为本申请实施例提供的半导体封装方法的示意图之三;

图6为本申请实施例提供的半导体封装方法的示意图之四;

图7为本申请实施例提供的半导体封装方法的示意图之五;

图8为本申请实施例提供的半导体封装方法的示意图之六;

图9为本申请实施例提供的半导体封装方法的示意图之七;

图10为本申请实施例提供的半导体封装方法的示意图之八;

图11为本申请实施例提供的电子设备的结构框图。

附图标记说明:

100,第二半导体衬底;110,保护层;130,第一半导体衬底;210,第一重布线层;212,第一绝缘层;217,第二焊盘;218,第一焊盘;220,第二重布线层;221、阻焊层;300,模版层;301,穿孔;302,金属穿孔;400,第一模塑组合物层;401,凹槽;403,第一结构面;500,第二模塑组合物层;501,处理器;502,存储器;504,电源基板。

具体实施方式

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

应理解,说明书通篇中提到的“一个实施例”或“一实施例”意味着与实施例有关的特定特征、结构或特性包括在本申请的至少一个实施例中。因此,在整个说明书各处出现的“在一个实施例中”或“在一实施例中”未必一定指相同的实施例。此外,这些特定的特征、结构或特性可以任意适合的方式结合在一个或多个实施例中。

在本申请的各种实施例中,应理解,下述各过程的序号的大小并不意味着执行顺序的先后,各过程的执行顺序应以其功能和内在逻辑确定,而不应对本申请实施例的实施过程构成任何限定。

参见图1,本申请实施例提供了一种半导体结构,包括:

第一半导体衬底130;其中,所述第一半导体衬底130的材质可以是玻璃、硅、陶瓷、金属或其他材质;在封装所述半导体结构的过程中,可以先使用封装半导体衬底,并在封装的最后步骤中,移除封装半导体衬底,替换为第一半导体衬底130。

第一重布线层210,设置于所述第一半导体衬底130之上,重布线层(Re-Distribution Layer,RDL)用于扇出半导体裸片(第一半导体衬底130)上的输入/输出点。

第一模塑组合物层400,设置于所述第一重布线层210之上;其中,所述第一模塑组合物层400的第一结构面403设置有凹槽401;第一模塑组合物层400设置于两个重布线层之间,且凹槽401用于容置存储器502;其中,第一模塑组合物层400作为下层中介层,用于放置逻辑芯片等模块。

存储器502,至少部分设置于所述凹槽401中;所述存储器502可以是高带宽内存(High Bandwidth Memory,HBM)、动态随机存取存储器(Dynamic Random-Access Memory,DRAM)、静态随机存取存储器(Static Random-Access Memory,SRAM)或固态存储器(如闪存设备)中的至少一种;可以理解的是,所述半导体结构中可以包括一个或至少两个存储器,如图1中所示,两个存储器502分别设置于所述凹槽401中,以降低半导体结构的整体封装高度。

第二重布线层220,设置于所述第一结构面403上所述凹槽401以外的区域;即第二重布线层220与凹槽401均设置在第一结构面403上。

处理器501,设置于所述第二重布线层220之上,并与所述存储器502至少部分重叠设置,如图1所示,这样,减少了占用第一模塑组合物层400的面积,进而节省第一模塑组合物层400的使用成本。

所述处理器501分别与所述存储器502、所述第一重布线层210的第一焊盘218电连接,实现处理器501与存储器502的通信,以及所述处理器501与第一重布线层210的通信。其中,处理器501可以是中央处理器(Central Processing Unit,CPU)、图形处理器(GraphicsProcessing Unit,GPU)、数字信号处理器(Digital Signal Process,DSP)等处理器中任意一种。可以理解的是,所述半导体结构中可以包括一个或至少两个处理器501。

可选地,本申请实施例中,所述处理器501与所述存储器502可以为倒装芯片。

本申请实施例中,在所述半导体结构中,存储器502通过设置在作为中介层的第一模塑组合物层400的凹槽401内,降低了所述半导体结构的整体封装高度;处理器501与存储器502至少部分重叠设置,减少了第一模塑组合物层400的使用面积,节省第一模塑组合物层400的使用成本。本申请实施例解决了现有技术中,CoWoS封装技术导致封装尺寸过大以及成本增加的问题。

在一个可选实施例中,所述半导体结构还包括:

第二模塑组合物层500,覆盖所述第二重布线层220以及所述处理器501、所述存储器502;

电源基板504,与所述存储器502的接触面连接,其中,所述电源基板504一部分与存储器502的接触面连接,另一部分与第二重布线层22的焊盘连接。

在一个可选实施例中,所述第一模塑组合物层400设置有贯穿于所述第一模塑组合物层400的金属穿孔302;所述金属穿孔302内填充有金属;金属穿孔302高度等于模版层300。

所述金属穿孔302的第一端裸露于所述第一模塑组合物层400的第一结构面403;可对第一模塑组合物层400的表面进行研磨,使金属穿孔302上第一端裸露出来。

所述金属穿孔302的第二端与所述第一焊盘218电连接。

在一个可选实施例中,所述处理器501依次通过所述第二重布线层220的第二焊盘217、所述金属穿孔302与所述第一焊盘218电连接,实现处理器501与第一重布线层210之间的信号传输或者数据传输。

在一个可选实施例中,所述第一重布线层210包括第一绝缘层212,所述第一焊盘218贯穿于所述第一绝缘层212,第一焊盘218形成第一重布线层210的金属区域。

本申请实施例中,在所述半导体结构中,存储器502通过设置在作为中介层的第一模塑组合物层400的凹槽401内,降低了所述半导体结构的整体封装高度;处理器501与存储器502至少部分重叠设置,减少了第一模塑组合物层400的使用面积,节省第一模塑组合物层400的使用成本。

以上介绍了本申请实施例提供的半导体结构,下面将结合附图介绍所述半导体结构的封装方法。

参见图2,本申请实施例提供了一种半导体封装方法,包括步骤201至步骤209;具体地,

步骤201,提供一第二半导体衬底100。

其中,如图3所示,第二半导体衬底100为可移除的基底材料,如玻璃、硅、陶瓷、金属等材质。

步骤202,在所述第二半导体衬底之上覆盖一保护层110。

如图3所示,保护层110的材质可以是有机材料聚酰亚胺(Polyimide,PI)或无机材料,无机材料例如氮化硅或氧化硅等。

步骤203,在所述保护层110之上设置覆盖一层第一重布线层210。

如图4所示,第一重布线层210用于扇出半导体裸片上的输入/输出点。

步骤204,在所述第一重布线层210之上覆盖模塑组合物,形成第一模塑组合物层400。

如图5所示,第一模塑组合物层400覆盖第一重布线层210;第一模塑组合物层400作为下层中介层,用于放置逻辑芯片等模块。

步骤205,在所述第一模塑组合物层400的第一结构面403上形成凹槽401。

如图5所示,凹槽401用于容置存储器502。可通过研磨的方式,在第一模塑组合物层400的预留无金属穿孔302的区域研磨,形成凹槽401。

步骤206,在所述第一结构面403上所述凹槽401以外的区域覆盖第二重布线层220。

如图6所示,第二重布线层220与凹槽401均设置在第一结构面403上。第二重布线层220包括一个绝缘层和一个由金属穿孔302形成的金属层,焊盘暴露于上绝缘层,在焊盘上生成锡球(solder ball);其中,221为阻焊层(solder mask)。

步骤207,在凹槽401中放置存储器502。

所述存储器502可以是HBM、DRAM、SRAM或固态存储器(如闪存设备)中的至少一种;可以理解的是,所述半导体结构中可以包括一个或至少两个存储器,如图1中所示,两个存储器502分别设置于所述凹槽401中,以降低半导体结构的整体封装高度。

步骤208,在所述第二重布线层220之上放置处理器501;其中,所述处理器501分别与所述存储器502、所述第一重布线层210的第一焊盘218电连接。

所述处理器501分别与所述存储器502、所述第一重布线层210的第一焊盘218电连接,实现处理器501与存储器502的通信,以及所述处理器501与第一重布线层210的通信。其中,处理器501可以是CPU、GPU、DSP等处理器中任意一种。可以理解的是,所述半导体结构中可以包括一个或至少两个处理器501。

可选地,本申请实施例中,所述处理器501与所述存储器502可以为倒装芯片。

步骤209,移除所述保护层110以及所述第二半导体衬底100,将所述第一重布线层210与第一半导体衬底130连接,形成半导体结构。

移除保护层110和第二半导体衬底100,在第一重布线层210的焊盘上生成锡球,锡球直接第一半导体衬底130,最后,晶元级封装被切片成独立芯片。

这样,在封装所述半导体结构中,存储器502通过设置在作为中介层的第一模塑组合物层400的凹槽401内,降低了所述半导体结构的整体封装高度;处理器501与存储器502至少部分重叠设置,减少了第一模塑组合物层400的使用面积,节省第一模塑组合物层400的使用成本。

在一个可选实施例中,步骤203之后,所述方法包括以下第一步至第三步;

第一步,在所述第一重布线层210之上覆盖一层模版层300。

参见图7,模版层300覆盖在第一重布线层210之上;模版层300的材质可以可能是光刻胶或者定向自组装材料。

第二步,对所述模版层300进行光刻处理,形成贯穿于所述模版层300的穿孔301;

参见图8,光刻过程包括曝光和显影,形成贯穿模版层300的穿孔301。

第三步,在所述穿孔301填充金属,形成金属穿孔302,移除模版层300;

其中,所述金属穿孔302贯穿于所述第一模塑组合物层400。

参见图9,穿孔301形成后,向其内填充金属,如铜、钨、铝、氮化钛或其他金属;具体地,可以采用沉积、丝网印刷工艺填充。可选地,填充金属之后,还可采用化学机械研磨(Chemical-Mechanical Polishing,CMP)工艺移除溢出于穿孔301的金属,金属穿孔302高度等于模版层300。可选地,可对第一模塑组合物层400的表面进行研磨,使金属穿孔302上部暴露出来。

参见图10,金属穿孔302形成后,移除模版层300,保留金属穿孔302;若300包含光刻胶,可以采用等离子刻蚀或灰化工艺,此时焊盘218裸露出来。

在一个可选实施例中,步骤209之前,所述方法还包括:

通过所述存储器502的接触面以及所述第二重布线层220的第二焊盘217,与电源基板连接;

通过模塑组合物覆盖所述第二重布线层220以及所述处理器501、所述存储器502,形成第二模塑组合物层500。

其中,所述电源基板504一部分与存储器502的接触面连接,另一部分与第二重布线层22的焊盘连接。

作为第一示例,所述半导体封装方法的应用过程,主要包括以下步骤1至步骤14:

步骤1,提供一第二半导体衬底100;

步骤2,在所述第二半导体衬底之上覆盖一保护层110;

步骤3,在所述保护层110之上设置覆盖一层第一重布线层210;所述第一重布线层210包括第一绝缘层212以及贯穿于所述第一绝缘层212的第一焊盘218;所述第一焊盘218的第一端与所述保护层110连接;

步骤4,在所述第一重布线层210之上覆盖一层模版层300;

步骤5,对所述模版层300进行光刻处理,形成贯穿于所述模版层300的穿孔301;

步骤6,在所述穿孔301填充金属,形成金属穿孔302,移除模版层300;

步骤7,通过模塑组合物覆盖所述金属穿孔302以及第一重布线层210,形成第一模塑组合物层400;所述金属穿孔302的第一端裸露于所述第一模塑组合物层400的第一结构面403;

步骤8,在所述第一结构面403上形成凹槽401;

步骤9,在所述第一结构面403上所述凹槽401以外的区域覆盖第二重布线层220;

步骤10,在凹槽401中放置存储器502;

步骤11,在所述第二重布线层220之上放置处理器501。

其中,所述处理器501与所述存储器502电连接;所述处理器501分别通过所述第二重布线层220的第二焊盘217、所述金属穿孔302与所述第一焊盘218电连接。

步骤12,通过所述存储器502的接触面以及所述第二焊盘217,与电源基板连接;

步骤13,通过模塑组合物覆盖所述第二重布线层220以及所述处理器501、所述存储器502,形成第二模塑组合物层500;

步骤14,移除所述保护层110以及所述第二半导体衬底100,将所述第一重布线层210与第一半导体衬底130连接,形成半导体结构。

本申请实施例中,在封装所述半导体结构中,存储器502通过设置在作为中介层的第一模塑组合物层400的凹槽401内,降低了所述半导体结构的整体封装高度;处理器501与存储器502至少部分重叠设置,减少了第一模塑组合物层400的使用面积,节省第一模塑组合物层400的使用成本。本申请实施例解决了现有技术中,CoWoS封装技术导致封装尺寸过大以及成本增加的问题。

另一方面,本申请实施例还提供了一种电子设备,包括存储器、处理器、总线以及存储在存储器上并可在处理器上运行的计算机程序,所述处理器执行所述程序时实现上述半导体封装方法中的步骤。

举个例子如下,图11示出了一种电子设备的实体结构示意图。

如图11所示,该电子设备可以包括:处理器(processor)1110、通信接口(Communications Interface)1120、存储器(memory)1130和通信总线1140,其中,处理器1110,通信接口1120,存储器1130通过通信总线1140完成相互间的通信。处理器1110可以调用存储器1130中的逻辑指令,以执行如下方法:

提供一第二半导体衬底;

在所述第二半导体衬底之上覆盖一保护层;

在所述保护层之上设置覆盖一层第一重布线层;

在所述第一重布线层之上覆盖模塑组合物,形成第一模塑组合物层;

在所述第一模塑组合物层的第一结构面上形成凹槽;

在所述第一结构面上所述凹槽以外的区域覆盖第二重布线层;

在所述凹槽中放置存储器;

在所述第二重布线层之上放置处理器;其中,所述处理器分别与所述存储器、所述第一重布线层的第一焊盘电连接;

移除所述保护层以及所述第二半导体衬底,将所述第一重布线层与第一半导体衬底连接,形成半导体结构。

此外,上述的存储器1130中的逻辑指令可以通过软件功能单元的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可读取存储介质中。基于这样的理解,本申请的技术方案本质上或者说对现有技术做出贡献的部分或者该技术方案的部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质中,包括若干指令用以使得一台计算机设备(可以是个人计算机,服务器,或者网络设备等)执行本申请各个实施例所述方法的全部或部分步骤。而前述的存储介质包括:U盘、移动硬盘、只读存储器(ROM,Read-Only Memory)、随机存取存储器(RAM,Random Access Memory)、磁碟或者光盘等各种可以存储程序代码的介质。

再一方面,本申请实施例还提供了一种计算机可读存储介质,其上存储有计算机程序,该计算机程序被处理器执行时实现以执行上述各实施例提供的半导体封装方法,例如包括:

提供一第二半导体衬底;

在所述第二半导体衬底之上覆盖一保护层;

在所述保护层之上设置覆盖一层第一重布线层;

在所述第一重布线层之上覆盖模塑组合物,形成第一模塑组合物层;

在所述第一模塑组合物层的第一结构面上形成凹槽;

在所述第一结构面上所述凹槽以外的区域覆盖第二重布线层;

在所述凹槽中放置存储器;

在所述第二重布线层之上放置处理器;其中,所述处理器分别与所述存储器、所述第一重布线层的第一焊盘电连接;

移除所述保护层以及所述第二半导体衬底,将所述第一重布线层与第一半导体衬底连接,形成半导体结构。

以上所描述的装置实施例仅仅是示意性的,其中所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部模块来实现本实施例方案的目的。本领域普通技术人员在不付出创造性的劳动的情况下,即可以理解并实施。

通过以上的实施方式的描述,本领域的技术人员可以清楚地了解到各实施方式可借助软件加必需的通用硬件平台的方式来实现,当然也可以通过硬件。基于这样的理解,上述技术方案本质上或者说对现有技术做出贡献的部分可以以软件产品的形式体现出来,该计算机软件产品可以存储在计算机可读存储介质中,如ROM/RAM、磁碟、光盘等,包括若干指令用以使得一台计算机设备(可以是个人计算机,服务器,或者网络设备等)执行各个实施例或者实施例的某些部分所述的方法。

最后应说明的是:以上实施例仅用以说明本申请的技术方案,而非对其限制;尽管参照前述实施例对本申请进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本申请各实施例技术方案的精神和范围。

- 半导体封装结构、半导体封装结构的形成方法以及半导体组装结构的形成方法

- 半导体封装、半导体封装结构及制造半导体封装的方法