新型功率器件及其划片方法、芯片级封装方法和封装结构

文献发布时间:2023-06-19 11:57:35

技术领域

本发明涉及微电子技术领域,尤其涉及新型功率器件及其划片方法、芯片级封装方法和封装结构。

背景技术

为进一步降低功率MOSFET的导通电阻,晶圆背面厚金属层是常用的手段;常见的晶圆正面划片工艺为晶圆背面贴膜,从晶圆正面划片,由于背面厚的金属层易粘附在划片刀上,极易出现拉丝等现象,造成晶圆正面源极(Source)与晶圆正面栅极(Gate)之间、晶圆正面源极(Source)与晶圆背面漏极(Drain)之间短路、晶圆正面栅极(Gate)与晶圆背面漏极(Drain)之间短路。在一些特殊的封装工艺中,有时需要从晶圆背面对晶圆进行切割,因为晶圆背面没有划片道,如何使位于晶圆背面一侧的切割刀对准位于晶圆正面的划片道就成了一个棘手的问题。

发明内容

本发明提供新型功率器件及其划片方法、芯片级封装方法和封装结构,旨在解决现有技术中功率器件划片时出现拉丝导致短路、背面划片困难等技术问题。

一种新型功率器件的划片方法,包括如下步骤:

步骤A1,在晶圆的有生长多个管芯,晶圆的正面相邻的管芯之间通过划片道进行隔离;

步骤A2,对晶圆的正面的每个划片道分别进行第一次划片形成划片槽;

步骤A3,在划片槽内填充树脂层;

步骤A4,对晶圆的背面进行研磨减薄,使填充于划片槽的树脂层暴露于晶圆的背面;

步骤A5,对减薄后的晶圆的背面进行蚀刻,使树脂层的背面高于晶圆的背面,从而在晶圆的背面形成若干突出部分,突出部分与划片道的位置一一对应;

步骤A6,在晶圆的背面进行金属化形成背面金属化层,背面金属化层覆盖晶圆的背面和树脂层的突出部分,使得背面金属化层在树脂层的突出部分形成金属突起;

步骤A7,对金属突起和突出部分进行第二次划片或者蚀刻,去除突出部分以及突出部分邻近的金属;

步骤A8,对准晶圆的背面露出的树脂进行第三次划片,将各个管芯进行分离形成单个功率器件。

进一步的,在步骤A2中,划片槽的深度大于晶圆在步骤A4中减薄后的剩余厚度。

进一步的,所述步骤A7中所述第二次划片所使用的划片刀的宽度大于所述步骤A2中所述第一次划片所使用的划片刀的宽度。

进一步的,步骤A8中第三次划片所使用的划片刀的宽度小于步骤A2中第二次划片所使用的划片刀的宽度。

进一步的,在步骤A1中,每一个管芯的源极和栅极位于晶圆的正面,源极和栅极之间采用介质层进行隔离,在晶圆的背面分别形成每一个管芯的漏极;

则在步骤A6中,背面金属化层分别与每一个管芯的漏极电接触。

一种新型功率器件,使用前述的一种功率器件的划片方法制备而成,包括:

半导体衬底;

管芯,管芯的源极和栅极位于半导体衬底的正面,源极和栅极之间采用介质层进行隔离,管芯的漏极位于半导体衬底的背面;

背面金属化层,分别与管芯的漏极电接触;

半导体衬底的四个侧面均由树脂层包裹,树脂层的背面低于半导体衬底的背面并形成台阶;

背面金属化层在半导体衬底的背面且不与树脂层接触。

一种新型功率器件的芯片级封装方法,其特征在于,包括如下步骤:

步骤B1,在晶圆的正面有多个管芯,,晶圆的正面的相邻的管芯之间通过划片道进行隔离,每一个管芯的源极和栅极位于晶圆的正面,在源极和栅极的表面制作凸块;

步骤B2,对晶圆的正面的每一个划片道分别进行第一次划片形成划片槽;

步骤B3,在晶圆的正面铺设树脂层,使树脂层覆盖管芯和划片道,并填充划片槽;

步骤B4,对晶圆的正面的树脂层进行研磨减薄,使凸块表面显露出来;

步骤B5,对晶圆的背面进行研磨减薄,使划片槽以及填充于划片槽的树脂层暴露于晶圆的背面;

步骤B6,对减薄后的晶圆的背面进行蚀刻,使树脂层的背面高于晶圆的背面,从而在晶圆的背面形成若干突出部分,突出部分与划片道的位置一一对应;

步骤B7,在晶圆的背面进行金属化形成背面金属化层,背面金属化层覆盖晶圆的背面和树脂层的突出部分,使得背面金属化层在树脂层的突出部分形成金属突起;

步骤B8,对金属突起和突出部分进行第二次划片或者蚀刻,去除突出部分以及突出部分邻近的金属;

步骤B9,对准晶圆的背面露出的树脂层,进行第三次划片,将各个管芯进行分离形成单个功率器件封装结构。

进一步的,在步骤B2中,划片槽的深度大于晶圆在步骤B5中减薄后的剩余厚度。

进一步的,步骤B8中第二次划片所使用的划片刀的宽度大于步骤B2中所述第一次划片所使用的划片刀的宽度。

进一步的,步骤B9中第三次划片所使用的的划片刀的宽度小于步骤B2中第一次划片所使用的划片刀的宽度。

进一步的,在步骤B1中,源极和栅极之间采用介质层进行隔离,在晶圆的背面分别形成每一个管芯的漏极;

在步骤B7中,背面金属化层分别与每一个管芯的漏极电接触。

一种新型功率器件封装结构,其特征在于,使用前述的一种功率器件的芯片级封装方法制备而成,包括:

半导体衬底;

管芯,管芯的源极和栅极位于半导体衬底的正面,源极和栅极之间采用介质层进行隔离,管芯的漏极位于半导体衬底的背面;

背面金属化层,分别与管芯的漏极电接触;

管芯还包括分别设置于源极的表面和栅极的表面的凸块;

半导体衬底的四个侧面、正面均由树脂层包裹;

其中,凸块的正表面暴露于树脂层;

其中,树脂层的背面低于半导体衬底的背面并形成台阶;

背面金属化层在半导体衬底的背面且不与树脂层接触。

本发明的有益技术效果是:避免因金属化层在划片过程中出现拉丝现象而导致的短路想象,减低背面划片困难,金属沟槽作为对位标记有利于从晶圆背面进行划片。

附图说明

图1为本发明新型功率器件及其划片方法的准备晶圆的结构示意图;

图2为本发明新型功率器件及其划片方法的形成划片槽的结构示意图;

图3为本发明新型功率器件及其划片方法的填充树脂的结构示意图;

图4为本发明新型功率器件及其划片方法的背面减薄结构示意图;

图5为本发明新型功率器件及其划片方法的背面腐蚀形成台阶结构示意图;

图6为本发明新型功率器件及其划片方法的背面金属化结构示意图;

图7为本发明新型功率器件及其划片方法的背面划片化结构示意图;

图8为本发明新型功率器件及其划片方法的形成的单个功率器件结构示意图;

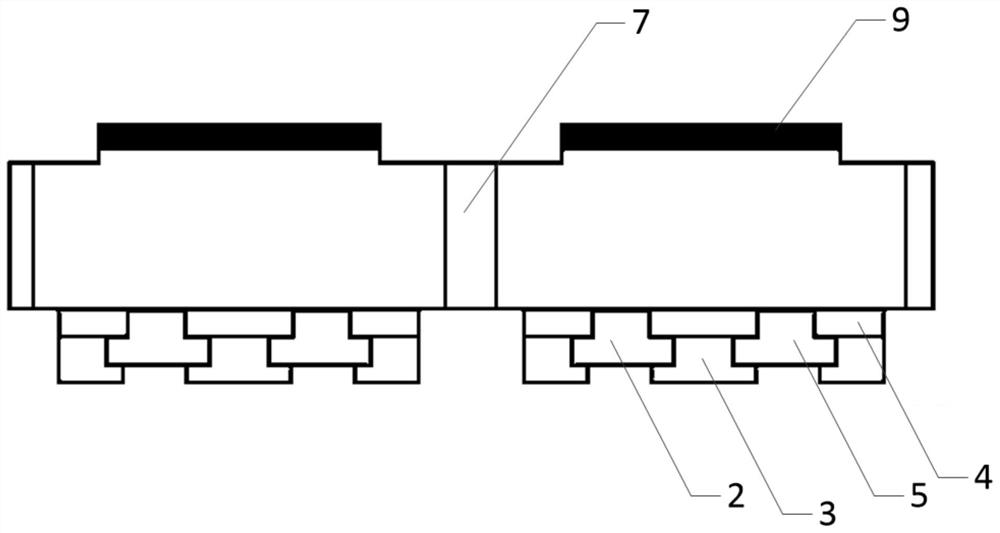

图9为本发明新型功率器件及其划片方法的形成的单个功率器件封装结构示意图;

图10为本发明新型功率器件及其划片方法的步骤流程图;

图11为本发明一新型功率器件的芯片级封装方法的步骤流程图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动的前提下所获得的所有其他实施例,都属于本发明保护的范围。

需要说明的是,在不冲突的情况下,本发明中的实施例及实施例中的特征可以相互组合。

下面结合附图和具体实施例对本发明作进一步说明,但不作为本发明的限定。

参见图1-8和图10,本发明一种新型功率器件的划片方法,包括如下步骤:

步骤A1,提供一包括若干管芯的晶圆(1),即在晶圆的正面有多个管芯,晶圆的正面的相邻管芯之间通过划片道进行隔离;

步骤A2,对晶圆(1)的正面的每个划片道分别进行第一次划片形成划片槽(6);

步骤A3,在划片槽(6)内填充树脂层(7);

步骤A4,对晶圆(1)的背面进行研磨减薄,使填充于划片槽(6)的树脂层(7)暴露于晶圆(1)的背面;

步骤A5,对减薄后的晶圆(1)的背面进行蚀刻,使树脂层(7)的背面高于晶圆(1)的背面,从而在晶圆的背面形成若干突出部分,突出部分与划片道的位置一一对应;即使树脂层(7)突出晶圆背面;

步骤A6,在晶圆(1)背面进行金属化形成背面金属化层(9),背面金属化层(9)覆盖晶圆(1)的背面和树脂层(7)的突出部分,使得背面金属化层(9)在树脂层(7)处形成金属突起(10);

步骤A7,对金属突起(10)进行第二次划片或者蚀刻,去除树脂层高于晶圆的背面的突出部分以及突出部分邻近的金属;

步骤A8,对准晶圆的背面露出的树脂层(7)进行第三次划片,将各个管芯进行分离形成单个功率器件。

具体的,通过本发明从晶圆背面进行划片将管芯分离,即便出现拉丝现象,也不会造成晶圆正面源极(Source)与晶圆正面栅极(Gate)之间、晶圆正面源极(Source)与晶圆背面漏极(Drain)之间短路、晶圆正面栅极(Gate)与晶圆背面漏极(Drain)之间各种短路现象。

具体的,将晶圆背面露出的树脂作为对位标记,使得背面划片即第三次划片更加容易实现。

具体的,在步骤A3和A4之间还包括在晶圆正面贴敷划片膜以对晶圆和管芯进行保护的步骤。

具体的,晶圆为半导体,具体的为硅片。

具体的,由于在背面金属化之前,已经有晶圆(1)背面和树脂层(7)的背面形成台阶(8),即晶圆背面比树脂层(7)的背面低,形成的台阶,也就是树脂突出晶圆背面,形成突出部分,晶圆背面进行金属化时自然而然在树脂层(7)的背面因为台阶而形成金属突起(10),有利于知晓树脂位置所在,便于在步骤A7中对金属突起进行第二次划片或者蚀刻,进一步去掉树脂突出晶圆背面的部分,以及去掉树脂突出部分周围邻近的金属,露出的树脂正好作为背面划片的对位标记。

具体的,背面金属化层(9)是通过金属蒸发的方式沉积在晶圆背面,或者通过溅射镀膜的方式沉积在晶圆的背面。

具体的,功率器件是MOSFET管。

进一步的,在步骤A2中,划片槽(6)的深度大于晶圆(1)在步骤A4中减薄后的剩余厚度。

具体的,划片槽(6)不可穿透减薄前晶圆的厚度,这样直接是正面划片即第一次划片使得管芯分离。划片槽(6)的深度如果过小,在晶圆进行减薄处理至预定厚度时树脂(7)仍然不会暴露出来,便无法形成台阶和对位标记。因此,对划片槽(6)的深度有一定要求。

进一步的,步骤A7中第二次划片所使用的的划片刀的宽度大于步骤A2中所述第一次划片所使用的划片刀的宽度。

进一步的,步骤A8中第三次划片所使用的划片刀的宽度小于步骤A2中第一次划片所使用的划片刀的宽度,使每个功率器件的四个侧面被树脂层(7)包裹。

具体的,步骤A8中背面划片即第三次划片的划片刀的宽度要小于步骤A2中正面划片的划片刀的宽度,这样在进行背面划片时会使得晶圆侧面也就是功率器件的侧面保留有树脂部分;如果步骤B8中的划片刀的宽度大于步骤B2中正面划片即第一次划片的划片刀的宽度,这样不会在进行第三次划片时会使得晶圆侧面也就是功率器件的侧面保留有树脂部分。

进一步的,在步骤A1中,每一个管芯的源极(2)和栅极(5)位于晶圆(1)的正面,源极(2)和栅极(5)之间采用介质层进行隔离,在晶圆(1)的背面分别形成每一个管芯的漏极;

在步骤A6中,背面金属化层(9)分别与每一个管芯的漏极电接触。

具体的,在晶圆(1)正面具有第一介质层(4),将源极(2)和栅极(5)隔开,在制备源极(2)和栅极(5)之后,第一介质层(4)上还制作第二介质层(3),进一步将源极(2)和栅极(5)隔开。

本发明还提供新型功率器件,使用前述的一种功率器件的划片方法制备而成,包括:

半导体衬底;

管芯,管芯的源极(2)和栅极(5)位于半导体衬底的正面,源极(2)和栅极(5)之间采用介质层进行隔离,管芯的漏极位于半导体衬底的背面;

背面金属化层(9),分别与管芯的漏极电接触;

半导体衬底的四个侧面均由树脂层(7)包裹,树脂层(7)低于半导体衬底的背面并形成台阶;

背面金属化层(9)在半导体衬底的背面且不与树脂层(7)接触。

参见图1-9和图11,本发明还提供一种新型功率器件的芯片级封装方法,包括如下步骤:

步骤B1,提供一包括若干管芯的晶圆(1),即在晶圆的正面有多个管芯,晶圆(1)的正面相邻的管芯之间通过划片道进行隔离,每一个管芯的源极(2)和栅极(5)位于晶圆(1)的正面,在源极(2)和栅极(5)的表面制作凸块(11);

步骤B2,对晶圆(1)的正面的每一个划片道分别进行第一次划片形成划片槽(6);

步骤B3,在晶圆(1)的正面铺设树脂层(7),使树脂层(7)覆盖管芯和划片道,并填充划片槽(6);

步骤B4,对晶圆(1)的正面的树脂层(7)进行研磨减薄,使凸块(11)表面显露出来;

步骤B5,对晶圆(1)的背面进行研磨减薄,使填充于划片槽(6)的树脂层(7)暴露于在晶圆(1)的背面;

步骤B6,对减薄后的晶圆(1)的背面进行蚀刻,使树脂层(7)的背面高于晶圆(1)的背面,即使得树脂层(7)的背面突出晶圆的背面,从而在晶圆的背面形成若干突出部分(8),突出部分(8)与划片道的位置一一对应;

步骤B7,在晶圆(1)的背面进行金属化形成背面金属化层(9),背面金属化层(9)覆盖晶圆(1)背面和树脂层(7)的突出部分(8),使得背面金属化层(9)在树脂的突出部分(8)形成金属突起(10);

步骤B8,对金属突起(10)和树脂(7)的突出部分(8)进行第二次划片或者蚀刻,去除树脂层(7)的突出部分以及突出部分邻近的金属;

步骤B9,对准晶圆的背面露出的树脂层进行第三次划片,将各个管芯进行分离形成单个功率器件封装结构。

具体的,通过本发明从晶圆背面进行划片将管芯分离,即便出现拉丝现象,也不会造成晶圆正面源极(Source)与晶圆正面栅极(Gate)之间、晶圆正面源极(Source)与晶圆背面漏极(Drain)之间短路、晶圆正面栅极(Gate)与晶圆背面漏极(Drain)之间各种短路现象。

具体的,将晶圆的背面露出的树脂作为对位标记,使得背面划片即第三次划片更加容易实现。

具体的,在步骤B4和B5之间还包括在晶圆正面贴敷划片膜以对晶圆和管芯进行保护的步骤。

具体的,晶圆为半导体,具体的为硅片。

具体的,由于在背面金属化之前,已经有晶圆(1)背面和树脂层(7)的背面形成突出部分(8),即晶圆背面比树脂层(7)的背面低,形成的台阶,也就是树脂层突出晶圆背面,晶圆背面进行金属化自然而然在树脂层(7)的背面因为台阶而形成突起,利用此突起可以作为背面划片的对位标记,有利于知晓树脂位置所在,便于在步骤A7中对金属突起进行第二次划片,进一步去掉树脂突出晶圆背面的部分,以及去掉树脂突出部分周围邻近的金属,露出的树脂正好作为背面划片的对位标记。

具体的,背面金属化层(9)是通过金属蒸发的方式沉积在晶圆背面,或者通过溅射镀膜的方式沉积在晶圆背面。

具体的,功率器件是MOSFET管。

进一步的,在步骤B2中,划片槽(6)的深度大于晶圆(1)在步骤B5中减薄后的剩余厚度。

具体的,划片槽(6)不可穿透减薄前晶圆的厚度,这样直接是正面划片使得管芯分离。划片槽(6)的深度如果过小,在晶圆进行减薄处理至预定厚度时树脂(7)仍然不会暴露出来,便无法形成台阶和对位标记。因此,对划片槽(6)的深度有一定要求。

进一步的,步骤B9中第三次划片所使用的划片刀的宽度要小于步骤B2中第一次划片所使用的划片刀的宽度,使每个功率器件封装结构的四个侧面被树脂层(7)包裹。

具体的,步骤B9中背面划片即第三次划片的划片刀的宽度要小于步骤B2中正面划片的划片刀的宽度,这样在进行背面划片时会使得晶圆侧面也就是功率器件封装结构的侧面保留有树脂部分;步骤B9中背面划片的划片刀的宽度要大于步骤B2中正面划片的划片刀的宽度,这样在进行背面划片时不会使得晶圆侧面也就是功率器件封装结构的侧面保留有树脂部分。

进一步的,在步骤B1中,源极(2)和栅极(5)之间采用介质层进行隔离,在晶圆(1)的背面分别形成每一个管芯的漏极;

在步骤B7中,背面金属化层(9)分别与每一个管芯的漏极电接触。

具体的,在晶圆(1)正面具有第一介质层(4),将源极(2)和栅极(5)隔开,在制备源极(2)和栅极(5)之后,第一介质层(4)上还制作第二介质层(3),进一步将源极(2)和栅极(5)隔开。

本发明还提供一种新型功率器件封装结构,使用前述的一种功率器件的芯片级封装方法制备而成,包括:

半导体衬底;

管芯,管芯的源极(2)和栅极(5)位于半导体衬底的正面,源极(2)和栅极(5)之间采用介质层进行隔离,管芯的漏极位于半导体衬底的背面;

背面金属化层(9),分别与管芯的漏极电接触;

管芯还包括分别设置于源极(2)的表面和栅极(5)的表面的凸块(11);

半导体衬底的四个侧面、正面均由树脂层(7)包裹;

其中,凸块(11)的正表面暴露于树脂层(7);

其中,树脂层(7)的背面低于半导体衬底的背面并形成台阶;

背面金属化层(9)在半导体衬底的背面且不与树脂层接触。

以上仅为本发明较佳的实施例,并非因此限制本发明的实施方式及保护范围,对于本领域技术人员而言,应当能够意识到凡运用本发明说明书及图示内容所作出的等同替换和显而易见的变化所得到的方案,均应当包含在本发明的保护范围内。

- 新型功率器件及其划片方法、芯片级封装方法和封装结构

- 一种新型功率器件封装结构及其制备方法