防止针对重排序缓冲器的基于定时的安全攻击

文献发布时间:2023-06-19 12:02:28

本申请要求于2018年12月5日提交的、申请序列号为16/210,609、名称为“防止针对重排序缓冲器的基于定时的安全攻击(Protection against Timing-based SecurityAttacks on Re-Order Buffers)”的美国专利申请的优先权,其全部公开内容在此引入作为参考。

技术领域

本文所公开的至少一些实施例总体上涉及计算机体系结构,并且更具体地但不限于,涉及防止针对重排序缓冲器的安全攻击的技术。

背景技术

指令通常被编程为按顺序执行。指令的程序顺序是指令被编程用于在处理器中执行的顺序。

可以根据替代顺序执行一些指令,并且获得与根据程序顺序执行指令相同的结果。

乱序执行已在一些处理器中实现,以提高处理器的处理能力的利用率并提高执行具有指令序列的程序的整体速度。

例如,当处理器将要处理被配置成用于对操作数进行操作的指令时,该操作数可处于从高速缓冲存储器或主存储器或存储装置加载的过程中。然而,程序顺序中的下一指令的操作数可能已经准备就绪在处理器中进行处理。因此,处理器可执行下一指令,而非暂停指令的执行以等待正从高速缓冲存储器、主存储器或存储装置加载的操作数。

指令的“数据顺序”是指令的数据或操作数在处理器中变得可用于处理的顺序。数据顺序通常不同于当代处理器设计中的程序顺序。处理器可以被配置成用于根据指令的数据顺序而不是指令的程序顺序来执行指令。

重排序缓冲器可用于在时间上保持在其程序顺序之外执行的指令的执行结果。例如,可以按照指令的数据顺序来执行指令。存储在重排序缓冲器中的结果可以以相应指令的程序顺序移出重排序缓冲器,就好像通过根据程序顺序执行指令来生成结果一样。例如,3个指令的序列可为用以将操作数A加载到第一寄存器中的第一指令(例如,“加载A,r1”),用以将另一操作数B加载到第二寄存器中的第二指令(例如,“加载B,r2”),以及用以将数字添加到第二寄存器的第三指令(例如,“添加#1,r2”)。可以在执行第一指令(例如“加载A,r1”)之前乱序执行第二指令(例如“加载B,r2”),执行第三指令(例如“添加#1,r2”),然后执行第一指令(例如“加载A,r1”)。当存储器系统可在操作数A之前返回操作数B时,此替代执行序列可为合意的。例如,当数据以B,#1,A的顺序就绪时,指令可以以“加载B,r2”、“添加#1,r2”和“加载A,r1”的顺序执行,这不同于程序顺序“加载A,r1”、“加载B,r2”和“添加#1,r2”。

乱序执行的实现可能存在安全漏洞。计算机处理器中的这种安全漏洞的示例包括2018年公开的Meltdown和Spectre。例如,安全漏洞可允许从特权安全边界高速缓存数据,从而导致可被定时以泄漏特权信息的竞争条件。特权安全边界中的数据的实例是位于操作系统内核中的数据。

附图说明

在附图中以示例而非限制的方式示出了实施例,在附图中相同的附图标记表示相同的元件。

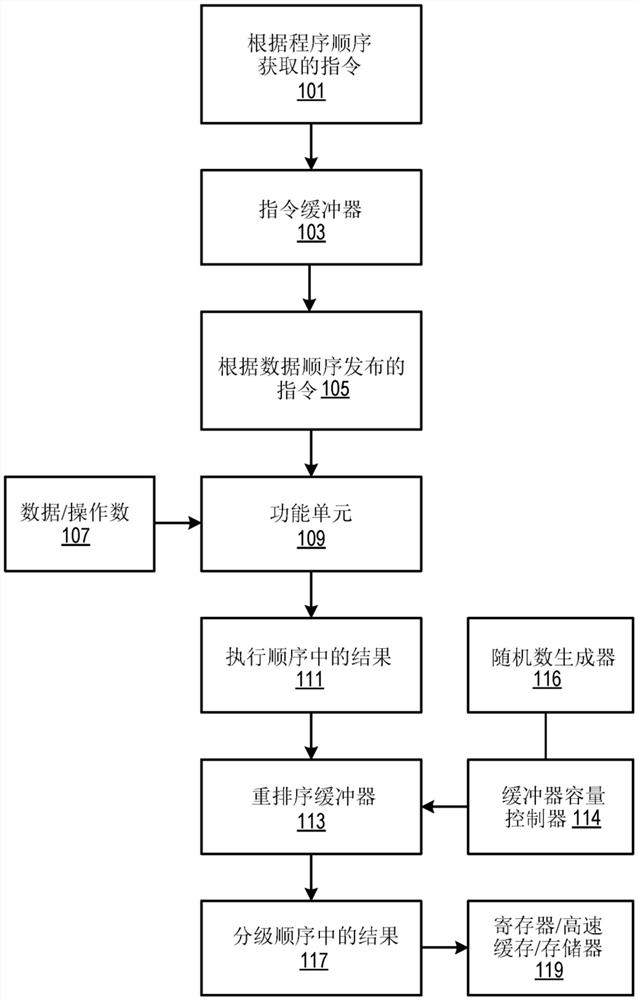

图1示出了根据一个实施例被配置成用于防止针对重排序缓冲器的基于定时的安全攻击的缓冲器控制器。

图2示出了根据一个实施例由缓冲器容量控制器控制的乱序执行。

图3示出了根据一个实施例防止针对重排序缓冲器的基于定时的安全攻击的方法。

图4示出了其中可以实现图3的方法的计算系统。

具体实施方式

本公开包括用于防止针对重排序缓冲器的基于定时的安全攻击的技术。

基于定时的安全攻击依赖于重排序缓冲器中的结果的定时模式。通过随机化在重排序缓冲器中结果的定时模式,可以防止和/或使得难以实施这种攻击。

例如,重排序缓冲器中的结果的定时模式可以取决于重排序缓冲器的操作容量。可用于对在其程序顺序之外执行的指令的结果重新排序的重排序缓冲器的实际/操作容量可随时间随机改变,使得定时模式随时间改变。这种容量调整可以在时间上随机地执行,或者周期性地执行,以在重排序缓冲器中的结果的定时中引入随机性。

图1示出了根据一个实施例被配置成用于防止针对重排序缓冲器(113)的基于定时的安全攻击的缓冲器控制器(115)。例如,缓冲器控制器(115)可以在图4所示的计算机系统的处理器中实现。

在图1中,重排序缓冲器(113)被配置成用于以执行指令的顺序接收指令的结果。重排序缓冲器(113)中的结果可移出重排序缓冲器(113)以用于基于“分级顺序”提交到处理器(例如,图4中的181)的寄存器堆、处理器的高速缓冲存储器、和/或处理器外部的存储器中。指令在重排序缓冲器(113)中的结果的分级顺序是指令的结果被提交和指令被引退完成的顺序;并且分级顺序(引退顺序或提交顺序)通常被配置成与指令的程序顺序一致。即将在程序顺序中较早执行的指令的执行结果将较早从重排序缓冲器(113)分级。当在程序顺序中的指令之前编程的指令的结果准备就绪移出重排序缓冲器(113)以供提交时,可将指令的结果移出重排序缓冲器(113)以供提交。在一些示例中,一些指令可以在并行单元、线程或流水线中执行;并且来自重排序缓冲器(113)的分级顺序(引退顺序或提交顺序)保持顺序一致性。通常,顺序一致性要求任何执行的结果与指令按其程序指定的顺序执行的结果相同。对寄存器的提交可称为对寄存器的写入。因此,可通过被配置成用于将结果写入到寄存器的处理器将结果提交到寄存器。

重排序缓冲器(113)的容量确定了在结果可以从重排序缓冲器(113)分级之前可以乱序执行的指令序列的深度。使用不同容量的重排序缓冲器(例如,113)执行的同一组指令可以在重排序缓冲器(113)中具有不同的结果缓冲定时。因此,改变重排序缓冲器(113)的容量可以改变乱序执行的模式。使重排序缓冲器(113)的容量的改变随机化可以在重排序缓冲器(113)中的数据定时中引入随机性,并且因此去除重排序缓冲器(113)中的定时的可预测性,并且阻止或防止针对重排序缓冲器(113)的基于定时的安全攻击。

在一些示例中,重排序缓冲器(113)具有预定的全容量。缓冲器控制器(115)识别重排序缓冲器(113)的可用容量,用于对按指令的实际执行/完成的顺序提供的输入结果(111)进行排序。当达到由缓冲器控制器(115)识别的可用容量时,防止超出用于每个重排序缓冲器(113)的指令集的指令的乱序执行可以缓冲其结果,直到重排序缓冲器中的一些结果从重排序缓冲器(113)分级。

重排序缓冲器(113)的可用容量可以是重排序缓冲器(113)的预定全容量的随机部分。重排序缓冲器(113)的可用容量中的随机性可以破坏或削弱重排序缓冲器(113)的定时的可预测性,从而防止对重排序缓冲器(113)的基于定时的安全攻击。

在一些示例中,重排序缓冲器(113)可以具有动态分配的容量,用于将执行顺序(111)中的结果排序为分级顺序(117)中的结果。缓冲器控制器(115)控制重排序缓冲器(113)的容量的动态分配(例如,基于随机数生成器的输出)。

在一些示例中,多个处理核心可分别具有多个重排序缓冲器(例如,113)。缓冲器控制器(115)可以为多个重排序缓冲器(例如,113)动态地重新分配共享缓冲器容量。例如,并非在多个重排序缓冲器(例如,113)之间均匀地划分共享缓冲器容量,缓冲器控制器(115)可以随机化多个重排序缓冲器(例如,113)之间的容量分配的比率,以引起定时的随机性。

在一些示例中,缓冲器控制器(115)以规则的预定时间间隔周期性地重新配置重排序缓冲器(113)的可用容量。可替换地,可以为重排序缓冲器(113)配置可用容量用于随机时间周期操作;并且在此随机时间周期操作之后,重排序缓冲器(113)的可用容量可以被重新配置用于另一随机周期的操作。操作的时间周期可以被称为,例如,第一时间周期和在第一时间周期之后的第二时间周期。在两个或多个恒定可用容量的操作周期长度中的随机性也可降低或破坏重排序缓冲器(113)中的定时可预测性。

图2示出了根据一个实施例由缓冲器容量控制器(114)控制的乱序执行。例如,可以使用具有随机数发生器(116)的图2的缓冲器容量控制器(114)来实现图1的缓冲器控制器(115),以使指令的乱序执行随机化。随机数生成器(116)可以被配置成用于防止攻击者检测从随机数生成器(116)和/或其用于生成随机化输出的算法生成的输出序列。例如,在随机数发生器(116)中可以使用计算机总线上的统计随机噪声,以防止攻击者精确地预测随机数发生器(116)的输出。电噪声通常不能精确建模。这种随机过程在理论上是完全不可预测的;而该理论关于不可预测的断言有待经过实验检验。通常,可以使用用于防止随机数发生器(116)攻击的任何技术。因此,本公开不限于随机数生成器的任何特定实现。

在图2中,在指令缓冲器(103)中缓冲根据指令的程序顺序提取的指令(101)。可以从处理器的高速缓冲存储器、计算机系统的存储器和/或计算机系统的存储装置(例如,如图6所示)获取指令(101)。

当指令的数据/操作数(107)对功能单元可用时,可以在处理器的功能单元(109)中执行指令缓冲器(103)中的指令。

通常,可从处理器的高速缓冲存储器、从计算机系统的存储器和/或从计算机系统的存储装置(例如,如图6所示)加载指令的一些数据操作数(107)。指令的其它数据操作数(107)可以是其它指令的执行结果。这种结果可以在处理器的寄存器/寄存器堆中和/或在重排序缓冲器(113)中获得。

加载某些数据项(例如,从高速缓冲存储器、主存储器或存储装置)可能花费比处理一或多个数据就绪指令更长的时间周期。功能单元(109)可在短时间周期内使用数据就绪指令的数据/操作数(107)。因此,可以将指令缓冲器(103)中的这种数据就绪指令发布到功能单元(109),以便根据不同于程序顺序的数据顺序来执行。

功能单元(109)以指令的执行/完成的顺序生成结果(111);并且结果(111)暂时存储在重排序缓冲器(113)中用于它们的分级。当在相应指令之前的指令的结果在重排序缓冲器(113)中并且准备就绪进行分级时,或者已经从重排序缓冲器(113)分级时,每个相应指令的结果可以从重排序缓冲器(113)分级/退出/提交。

可以将与其指令(101)的程序顺序一致的分级顺序中的结果(117)移出重排序缓冲器(113),以便提交到寄存器(寄存器堆、高速缓存\主存储器和/或存储装置)(119)中。

当重排序缓冲器(112)的容量固定时,安全攻击可以预测,确定和/或利用给定指令集的重排序缓冲器(112)中的结果(111)的定时,以获得关于指令和/或其数据的执行的未授权知识。

为了破坏、降低或削弱进入重排序缓冲器(113)的结果(111)和/或离开重排序缓冲器(113)的结果(117)的定时的可预测性,缓冲器容量控制器(114)可以通过在对结果(111/117)进行排序时随机化重排序缓冲器(113)的可用容量来在定时中注入随机性。

例如,缓冲器容量控制器(114)可包括或耦合到随机数发生器(116)。随机数生成器(116)的输出可以在缓冲器容量控制器(114)中使用,以在对结果(111/117)进行排序时确定重排序缓冲器(113)的可用部分的限制。

例如,当结果集从重排序缓冲器(113)分级时,缓冲器容量控制器(114)可以在对结果(111/117)进行排序时确定对重排序缓冲器(113)的可用部分的调整。可以通过将伪结果添加到重排序缓冲器(113)中,或者删除先前已添加到重排序缓冲器(113)中的伪结果来进行调整。已添加到重排序缓冲器(113)中的队列的前面或后面(或另一位置)的伪结果有效地减少了重排序缓冲器(113)的用于对结果(111/117)进行排序的可用部分。

例如,可以将随机数发生器(116)的输出转换为伪结果的计数,以在重排序缓冲器(113)中保存重排序缓冲器的下一操作时间周期。伪结果的计数对应于重排序缓冲器(113)的全部容量的一小部分。如果重排序缓冲器(113)中的伪结果的当前计数大于从随机数生成器(116)的输出转换的期望计数,则缓冲器容量控制器(114)从重排序缓冲器(113)中删除一或多个伪结果,就好像伪结果要从重排序缓冲器(113)中分级一样。如果重排序缓冲器(113)中的伪结果的当前计数小于从随机数生成器(116)的输出转换的期望计数,则缓冲器容量控制器(114)将一或多个伪结果添加到重排序缓冲器(113)中(例如,在由最近从重排序缓冲器(113)分级的结果(117)空出的槽中),就好像伪结果是由功能单元(109)作为执行伪指令的结果而生成的。

可替换地,缓冲器容量控制器(114)可以被配置成用于根据随机数生成器(116)来调整限定缓冲器容量控制器(114)的容量的重排序缓冲器(112)的一或多个边界。

在一些示例中,随机数发生器(115)的输出控制缓冲器容量控制器(114)何时调整重排序缓冲器(113)的可用容量。

例如,随机数发生器(115)的输出可用于设置两个连续调整之间的重排序缓冲器的操作周期的阈值计数。在先前调整之后的操作周期的阈值计数之后,缓冲器容量控制器(114)可以再次调整重排序缓冲器(113)的容量。

在一个实施例中,可基于处理器的指令周期(或时钟周期)的预定数目来计数重排序缓冲器的操作周期。

可替换地,操作周期可以被计数为在来自重排序缓冲器(113)的结果集(117)的两个连续分级之间。在这种情况下,周期的长度相对于时钟周期和/或指令周期可以不是恒定的。

图3示出了根据一个实施例防止针对重排序缓冲器的基于定时的安全攻击的方法。例如,可以使用图1的缓冲器控制器(115)或图2的缓冲器容量控制器(114)来实现图3的方法。

在框131处,处理器(例如,图4中的181)以与指令被编程的程序顺序不同的顺序执行指令。

例如,处理器可根据其中指令的数据/操作数在处理器中准备就绪进行处理的数据顺序来执行指令。

在框133处,处理器在重排序缓冲器(113)中缓冲指令的执行结果(111)。

例如,指令的执行结果(111)可以以不同于指令的程序顺序的顺序进入重排序缓冲器(113)。例如,第一指令可以被编程为比第二指令更早进行处理;由于乱序执行,第二指令的执行结果可以比第一指令的结果更早到达重排序缓冲器(113)中;并且在这种情况下,第二指令的执行结果可在重排序缓冲器(113)中等待,直到第一指令的结果到达重排序缓冲器(113)中,从而可以根据指令的程序顺序从重排序缓冲器(113)提供第一和第二指令的结果。

在框135处,重排序缓冲器(113)根据指令被编程的顺序输出指令的结果。

在框137处,控制器(例如,115或114)确定是否调整重排序缓冲器(113)的容量。

例如,控制器(例如,115或114)可以以规则的时间间隔确定是否调整重排序缓冲器(113)的容量。

例如,控制器(例如,115或114)可以确定当一些结果可以移出重排序缓冲器(113)以根据程序顺序进行分级时是否调整重排序缓冲器(113)的容量。

例如,控制器(例如,115或114)可以确定当多于阈值数目的结果可以移出重排序缓冲器(113)以根据程序顺序进行分级时是否调整重排序缓冲器(113)的容量。

例如,控制器(例如,115或114)可以确定当多于阈值数目的批次的结果已经移出重排序缓冲器(113)以便根据程序顺序进行分级时是否调整重排序缓冲器(113)的容量。

在框139处,如果控制器(例如,115或114)决定调整重排序缓冲器(113)的容量,则控制器(例如,115或114)根据随机数生成器(116)的输出来确定对重排序缓冲器(113)的容量的调整。

例如,控制器(例如,115或114)可以决定将重排序缓冲器(113)的容量增加或减少基于随机数生成器(116)的输出计算的随机量。

在一些示例中,控制器(例如,115或114)可以决定在由随机数发生器(116)控制的随机化时间情况下增加或减少重排序缓冲器(113)的容量(例如,增加或减少预定量)。

可选地,控制器(例如,115或114)可以决定在由随机量控制的随机时间增加或减少重排序缓冲器(113)的容量。

在框141处,控制器(例如,115或114)实现对重排序缓冲器(113)的容量的随机化调整。

例如,控制器(例如,115或114)可调整插入到重排序缓冲器(113)中的伪结果的数目以控制重排序缓冲器(113)在对结果进行排序时的有用容量。

例如,控制器(例如,115或114)可调整重排序缓冲器(113)的边界以控制重排序缓冲器(113)在排序结果中的有用容量。

例如,控制器(例如,115或114)可以再分割被配置成用于多个重排序缓冲器(例如,113)的一组存储器单元以调整其容量,包括重排序缓冲器(113)的容量。

图4示出了其中可以实现图3的方法的计算系统。

图4的计算系统可以包括具有内部高速缓存(191)的处理器(181)、存储装置(187)、外部高速缓存(193)和经由互连(185)连接到处理器(181)和/或存储器(187)的存储装置(189)。

例如,处理器(181)可以具有执行指令的功能单元(109)。处理器(181)可以进一步包括寄存器(153)以包含存储器地址、即将在功能单元(109)中执行的指令的数据/操作数、和/或指令的执行结果。

例如,寄存器(153)可以包括用于加载执行指令的程序计数器和存储器地址寄存器。当在处理器(181)中执行指令时,存储在存储器地址寄存器中的存储器地址可用于加载指令的操作数,和/或存储由执行指令生成的计算结果。

处理器(181)可以在其程序顺序之外执行指令,并使用重排序缓冲器(113)使指令的结果在程序顺序中可用。

处理器(181)具有控制器(151),其被配置成用于在进入和/或离开重排序缓冲器(113)的结果的定时中引起随机性。例如,可以使用上述结合图1至3讨论的任何技术,经由对重排序缓冲器(113)的有用容量的随机化调整来实现随机性。例如,控制器(151)可以被配置为图1的缓冲器控制器(115)或图2的缓冲器容量控制器(114),以使用图3的方法来随机化重排序缓冲器(113)中的数据定时。

上述讨论的随机化技术可以使重排序缓冲器(113)的使用对于相同程序的每次执行不尽相同。使用这些技术的结果之一是,对于具有相同数据集的相同程序在完全相同的计算条件(相同数量的用户、相同数量的物理存储器等)下的多次执行,程序的执行时间可以不同。在诸多情况下,这种安排本身对于定时攻击是高度安全的。

例如,更为常见的安全性攻击之一是基于定时来确定密码密钥。当执行实例的定时仅相差一两个周期时,在具有以本公开中讨论的方式配置的重排序缓冲器的计算机系统上,大量的这种攻击可能变得无用。

例如,当指令的数据/操作数在内部高速缓存(191)、寄存器(153)和/或重排序缓冲器(113)中可用时,处理器(161)可以从内部高速缓存(191)(例如,指令缓冲器(103))向功能单元(109)发布指令。处理器(161)缓冲由功能单元(109)生成的指令的执行结果,以便根据指令的程序顺序进行分级。处理器(161)可以将来自重排序缓冲器(113)的结果以程序顺序移动到寄存器(153)、内部高速缓冲存储器(191)、外部高速缓冲存储器(193)、存储器装置(187)和/或存储装置(189)。

在一些示例中,处理器(181)的寄存器使用的地址是虚拟存储器地址;并且存储器管理单元(MMU)(183)可以将虚拟存储器地址转换为物理存储器地址以访问外部高速缓存(193)、存储器装置(187)和/或存储装置(189)。

例如,可以将存储器装置(187)中的数据高速缓存在处理器(181)的外部高速缓存(193)和/或处理器(181)的内部高速缓存(191)中。

例如,外部高速缓存(193)中的数据可以高速缓存在内部高速缓存(191)中。

例如,存储装置(189)中的数据可以高速缓存在存储装置(187)、外部高速缓存(193)和/或内部高速缓存(191)中。

在一些示例中,存储器管理单元(MMU)(183)控制内部高速缓冲存储器(191)、外部高速缓冲存储器(193)和存储器装置(198)之间的数据移动。

本文所公开的技术可至少应用于其中处理器与存储器分离且处理器经由通信总线和/或计算机网络与存储器和存储装置通信的计算机系统。此外,本文所公开的技术可应用于其中处理能力集成在存储器/存储装置内的计算机系统。例如,包括典型处理器的执行单元和/或寄存器的处理电路可实施于集成电路和/或存储器介质的集成电路封装内以在存储器装置内执行处理。因此,以上讨论并在附图中示出的处理器(例如,101)不一定是冯诺依曼体系结构中的中央处理单元。处理器可以是集成在存储器内的单元,以克服冯诺依曼瓶颈,该瓶颈由于数据在中央处理单元和根据冯诺依曼体系结构单独配置的存储器之间移动的等待时间所引起的吞吐量限制而限制了计算性能。

本公开的描述和附图是说明性的,且不应将其解释为限制本公开。描述了众多特定细节以提供透彻理解。然而,在某些示例中,没有描述公知的或常规的细节以避免使描述模糊。本公开中对一个实施例的引用不一定是对相同实施例的引用;并且,这种引用意味着至少一个。

在前述说明书中,已参考其特定示例性实施例描述了本公开。显然,在不脱离所附权利要求中阐述的较宽精神和范围的情况下,可以对其进行各种修改。因此,说明书和附图被认为是说明性的而不是限制性的。

- 防止针对重排序缓冲器的基于定时的安全攻击

- 基于物联网的针对保鲜温度监测定时控制装置